Fターム[5F048BG11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面のみを絶縁物で分離するもの (4,648)

Fターム[5F048BG11]の下位に属するFターム

選択酸化(LOCOS)分離 (1,064)

トレンチ(溝)分離 (3,479)

V溝 (2)

Fターム[5F048BG11]に分類される特許

1 - 20 / 103

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】higher-k材料であるチタン酸化膜の半導体基板との界面を安定化でき、さらなる微細化に対応できるゲート構造を実現できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜と、該ゲート絶縁膜の上に形成されたゲート電極とを備えている。ゲート絶縁膜は、アナターゼ型酸化チタンを主成分とする高誘電率絶縁膜5であり、ゲート電極は、第1の金属膜6又は第2の金属膜8を含む導電膜から構成されている。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

エッチング方法及び装置

【課題】基板に形成された絶縁膜をエッチングするとき、絶縁膜の下地に酸素プラズマの悪影響が生ずるのを防止できるエッチング方法を提供する

【解決手段】本発明のエッチング方法は、絶縁膜222をプラズマ化させた処理ガスに晒し、絶縁膜222を厚さ方向に途中までエッチングする第一のエッチング工程と、第一のエッチング工程の終了後に残存する絶縁膜222を酸素プラズマに晒し、残存する絶縁膜222の表面に堆積した堆積物を除去する堆積物除去工程と、残存する絶縁膜222をプラズマ化させた処理ガスに晒し、残存する絶縁膜222をエッチングする第二のエッチング工程と、を備える。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】ラッチ回路を有する半導体装置におけるデータの破壊を抑制する。

【解決手段】ラッチ回路に含まれる第1トランジスタP4と、ラッチ回路に含まれ、第1トランジスタP4と共通のウェル40内に形成された、第1トランジスタP4と同じ導電型の第2トランジスタP1と、第1トランジスタP4と第2トランジスタP1との間に設けられ、ウェル40を電源に接続するウェルコンタクトWCと、を備える。第1トランジスタP4側のウェル40内で発生した電荷は、ウェルコンタクトWCに流れるため、第1トランジスタP4におけるソフトエラーの影響が、第2トランジスタP1に伝搬することを抑制することができる。これにより、ラッチ回路内における2箇所のノードにおいて、同時に論理の反転が生じることを抑制することができるため、データの破壊を抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置およびその製造方法

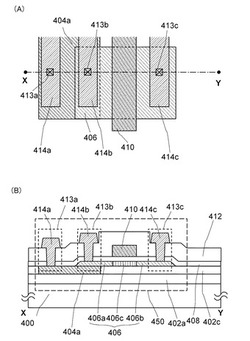

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の平坦性を維持しつつ、配線とインダクタとの間に生じる寄生容量を低減させた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に形成された第1の層間絶縁膜506と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた配線106と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた第1のダミーパターン107と、第1の層間絶縁膜506のうちインダクタ領域内に位置する部分に埋め込まれた第2のダミーパターン108と、第1の層間絶縁膜506の上方に形成された第2の層間絶縁膜と、第2のダミーパターン108の上方であって、第2の層間絶縁膜のうちインダクタ領域内に位置する部分に埋め込まれたインダクタ111とを備える。第2のダミーパターン108として金属が形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】TFT回路を備える半導体装置において、歩留まりの低下を抑制可能な半導体装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】ロジック回路10上に形成された層間絶縁膜22と、層間絶縁膜22上に形成され、上部から所定の高さまでシリサイド化されたシリサイド層30を含むアモルファスシリコン層23と、アモルファスシリコン層23上に形成されたTFTと、層間絶縁膜22を貫通する貫通孔24を埋め込むように形成され、ロジック回路10に電気的に接続すると共に、上部がシリサイド層30に接続するコンタクトプラグ25とを備える。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さ(RMS)が1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、または絶縁層表面の一部とドレイン電極表面との高低差は、5nm未満の半導体装置である。

(もっと読む)

半導体集積回路

【課題】アニールプロセス時において、アニール温度の温度むらを低減することを目的とする。

【解決手段】 複数のトランジスタが形成された第1領域100と、第1領域100の周囲に配置され、複数のダミートランジスタが形成された第2領域200とを備え、第2領域200に形成された複数のダミートランジスタのピッチpが、複数のトランジスタを形成する際に用いるフラッシュランプ光の中心波長λc以下である。さらに、第2領域のダミートランジスタの素子形成領域の幅が、ダミートランジスタのピッチの半分以下。

(もっと読む)

半導体装置の製造方法

【課題】不純物拡散領域の抵抗値のばらつきを抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体層にドーパント不純物を添加し、0.1秒〜10秒の活性化熱処理を行う。次いで、半導体層にイオン注入を行い、半導体層のドーパント不純物が添加された領域をアモルファス化する。次いで、0.1ミリ秒〜100ミリ秒の活性化熱処理を行い、アモルファス化した半導体層を再結晶化することにより、半導体層にドーパント不純物の拡散領域を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】チップサイズを増大させずに、より少ない製造工程数で製造された、抵抗値の異なる複数の抵抗素子を備えた半導体装置及び半導体装置の製造方法を提供する。

【解決手段】レジストマスク36をマスクとしてゲート電極23とマスク層22とを同一部材及び同一工程で形成し、形成されたマスク層22により高抵抗素子40となるポリシリコン高抵抗層16及びポリシリコン低抵抗層18の積層体と、低抵抗素子42となるポリシリコン高抵抗層16及びポリシリコン低抵抗層18の積層体と、をエッチングすることにより高抵抗素子40と、抵抗値が高抵抗素子40よりも低い低抵抗素子42と、を形成する。

(もっと読む)

半導体装置

【課題】パワーMOSFETを備える半導体装置のコストの低減を図る。

【解決手段】半導体装置1では、P型の半導体基板2上に、N型の半導体層3が積層されている。そして、半導体装置1は、LDMOS領域5に、ボディ領域8、ドレインバッファ領域9、ソース領域11およびゲート電極14などからなるLDMOSFETを備えている。すなわち、半導体装置1は、LDMOSFETを備えながら、厚膜SOI基板ではなく、N型の半導体層3が直上に設けられたP型の半導体基板2を採用している。そして、フィールド絶縁膜13上に7つのフィールドプレート15が設けられ、そのフィールドプレート15の間隔がボディ領域8側(ソース領域11側)ほど小さくされている。

(もっと読む)

1 - 20 / 103

[ Back to top ]