Fターム[5F048BH03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | PN接合分離 (956) | 素子領域底面のみにPN接合分離 (37)

Fターム[5F048BH03]に分類される特許

1 - 20 / 37

半導体装置

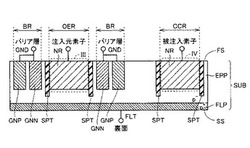

【課題】注入元素子から被注入素子への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】第1および第2の主表面を有する半導体基板SUB内にはエピタキシャル層EPPと、n型不純物領域NRを含む注入元素子と、注入元素子と間隔を隔てて形成された被注入素子と、注入元素子と被注入素子との間の領域の少なくとも一部に形成され、注入元素子と被注入素子とを結ぶ方向に対して交差する方向に延在する接地電位が印加されたn型領域GNNおよびp型領域GPPを有するバリア層BRとを備える。さらに半導体基板SUB内でエピタキシャル層EPPに接するように形成されたフローティングp型裏面領域FLPを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置

【課題】バルク半導体基板上に形成されるトンネルトランジスタ同士を電気的に分離することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板内に形成された第1および第2の素子分離絶縁膜とを備える。さらに、前記装置は、前記第1および第2の素子分離絶縁膜間の前記半導体基板上に、ゲート絶縁膜を介して形成されたゲート電極を備える。さらに、前記装置は、前記半導体基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記半導体基板内に前記第1および第2の素子分離絶縁膜に接するように形成され、前記第1および第2の主端子領域の下面よりも深い位置に上面を有する、前記第2導電型の第1の拡散層を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体装置及びその製造方法

【課題】小さいサイズでラッチアップの発生を防止できる半導体装置を提供する。

【解決手段】第1導電型の半導体基板1と、前記半導体基板内に形成された第1導電型の第1ウェル領域4と、前記半導体基板内に形成され、第1ウェル領域と隣り合う領域に配置された第2導電型のエピタキシャル領域2と、前記エピタキシャル領域内下方の領域に形成され、前記エピタキシャル領域よりも不純物濃度が高い第2導電型の埋め込み領域6と、第1ウェル領域と前記エピタキシャル領域及び前記埋め込み領域との境界に形成されたトレンチ8と、第1ウェル領域上に形成され、第2導電型のソース及びドレイン領域を有する第1半導体素子と、前記エピタキシャル領域上に形成され、第1導電型のソース及びドレイン領域を有する第2半導体素子と、を備える。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】高耐圧な半導体装置の製造方法を提供する。

【解決手段】半導体層に対してマスクを用いて選択的にイオン注入を行い、半導体層に第1導電型の第1の半導体領域と、前記第1の半導体領域よりも第1導電型不純物濃度が低い第1導電型の第2の半導体領域とを同時に形成する工程と、第1の半導体領域上に第2導電型のソース領域を形成する工程と、第2の半導体領域上であってソース領域との間にゲート電極を挟む位置に第2導電型のドレイン領域を形成する工程と、半導体層におけるゲート電極とドレイン領域との間の表層部にドレイン領域に接しドレイン領域よりも不純物濃度が低い第2導電型のドリフト領域を形成する工程とを備えている。

(もっと読む)

半導体装置

【課題】高耐圧の電界効果トランジスタを有する半導体装置のキンク現象を抑制または防止する。

【解決手段】高耐圧pMISQHp1のチャネル領域のゲート幅方向の両端の溝型の分離部3と半導体基板1Sとの境界領域に、高耐圧pMISQHp1のソースおよびドレイン用のp+型の半導体領域P1,P1とは逆の導電型のn+型の半導体領域NVkを、高耐圧pMISQHp1の電界緩和機能を持つp−型の半導体領域PV1,PV1(特にドレイン側)に接しないように、そのp−型の半導体領域PV1,PV1から離れた位置に配置した。このn+型の半導体領域NVkは、溝型の分離部3よりも深い位置まで延在されている。

(もっと読む)

CMOSFETデバイスおよびその製造方法

【課題】CMOSデバイスに新たに出現した中性子起因のバイポーラ型エラーモードMCBIに高い耐性を持つCMOSデバイスの新たな構造とその製造方法を提供する。

【解決手段】CMOSデバイスにおいて、両特性のMOSFET下面に埋め込みNウェル9を形成するトリプルウェル構造を有し、nMOSFETのストレージノード直下を含む領域または隣接する領域に、p−ウェル10とp基板12を電気的に接続する導通部8を形成する。これにより、正孔の逃げ道を形成する。この結果、p−ウェル10内のpn接合を中性子との核反応によって生成した2次イオンが貫通する際に残る正孔によるp−ウェル10の電位上昇を抑制できる。

(もっと読む)

半導体装置、及びその製造方法

【課題】、サイズを小さくできると共に、外部からのノイズに強く、漏洩電流が抑制された半導体装置及びその製造方法を提供すること。

【解決手段】 例えば、半導体基板10と、半導体基板10に形成されたP型のウェル10A(第1伝導型の第1領域)と、P型のウェル10A内に埋め込まれて形成されたN型のウェル10B(第2伝導型の第2領域)と、P型のウェル10A内であってN型のウェル10Bよりも上方に形成されたP型のウェル10C(第1伝導型の第3領域)と、P型のウェル10Cに形成された半導体素子20と、P型のウェル10CをN型のウェル10Bと共に取り囲むと共に、少なくとも底部がN型のウェル10Bと接触する深さを持って形成されたトレンチ型絶縁領域30と、を具備する半導体装置、及びその製造方法である。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間に配置される絶縁膜(例えば、BOX)にて構成される寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】低電位基準回路部LVに形成された第1サージ吸収層2aがトレンチ分離部5b内のドープトPoly−Si8bを通じてGND配線17aに電気的に接続されることでGND電位とされ、高電位基準回路部HVに形成された第2サージ吸収層2bがトレンチ分離部5b内のドープトPoly−Si8bを通じて仮想GND配線17bに電気的に接続されることで仮想GND電位とされるようにする。

(もっと読む)

半導体装置

【課題】ESD耐性が高い半導体装置を提供する。

【解決手段】P型基板2上にCMOS領域及びDMOS領域が形成された半導体装置1において、P型基板2上にN型エピタキシャル層3を形成し、その上にP型ウェル8を形成し、P型ウェル8の表層にN+型のソース層12及びドレイン層13を設ける。そして、ドレイン層13の直下域にN型ベース層31及びディープN型ベース層32を形成し、ソース層12の直下域にP型ベース層33及びディープP型ベース層34を形成する。これにより、ディープN型ベース層32とN型エピタキシャル層3との間に配置されたP型ウェル8のパンチスルー電圧VPTを、ソース層12、P型ウェル8及びドレイン層13からなる寄生横バイポーラトランジスタ42の動作電圧Vt1よりも低くする。

(もっと読む)

自己整合したソース/ドレイン領域を有するフィン型電界効果トランジスタ・デバイスおよびその形成方法

【課題】改良されたフィン電界効果トランジスタ(FinFET)デバイスと、その製造方法とを提供する。

【解決手段】1つの側面において、電界効果トランジスタ・デバイスを製造する方法は次のステップを含む。その上にシリコン層を有する基板が準備される。そのシリコン層においてフィン・リソグラフィー・ハードマスクがパターニングされる。フィン・リソグラフィー・ハードマスクの中央部分の上にダミー・ゲート構造が置かれる。ダミー・ゲート構造の周りにフィラー層が堆積させられる。フィン・リソグラフィー・ハードマスクの中央部分の上を中心として、フィラー層にトレンチを形成するためにダミー・ゲート構造が除去され、それはデバイスのフィン領域をデバイスのソース領域およびドレイン領域から区別する。フィン領域内のフィン・リソグラフィー・ハードマスクは、シリコン層に複数のフィンをエッチングするために使用される。フィンの上にゲート・スタックを形成するためにトレンチはゲート材料で満たされる。デバイスのソース領域およびドレイン領域を形成するためにフィラー層が除去され、ソース領域およびドレイン領域は無傷であってゲート・スタックと自己整合させられている。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元トランジスタでメモリセルを構成する際に問題となるチャネル部のフローティングを防止でき、高集積化可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】第1基柱2にチャネル部5と、チャネル部5の上下に形成された拡散層6,7と、チャネル部5の周りにゲート絶縁膜を介して形成されたゲート電極8とを備えた3次元トランジスタ1が、導電型の第2基柱3を囲むようにウェル領域上に複数配置され、複数個の3次元トランジスタ1が1つの第2基柱3を共有して、各々のチャネル部5がチャネル連結部4によって第2基柱3に接続されていることを特徴とする。また、6個からなる3次元トランジスタ1が、1個の第2基柱3を共有することができる。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが互いに異なる複数種類のMISトランジスタを内蔵する半導体集積回路装置において、信頼度の高いゲート絶縁膜を形成すると同時に、MISトランジスタの製造を容易とする。

【解決手段】シリコン酸化膜9を半導体基板1の表面に形成した後、実効膜厚が薄いゲート絶縁膜が形成される領域のシリコン酸化膜9をフッ酸水溶液を用いて除去し、その後半導体基板1上に高誘電率絶縁膜10を形成することにより、高誘電率絶縁膜10とシリコン酸化膜9との積層膜からなるゲート絶縁膜12、および高誘電率絶縁膜10からなるゲート絶縁膜11の2種類のゲート絶縁膜を半導体基板1上に形成する。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域3には、ドレイン領域となるn-拡散領域5が形成され、そのn-拡散領域5の一方の側には、p拡散領域7と、ソース領域となるn+拡散領域8が形成されている。n-拡散領域5の他方の側には溝部10が形成されて、絶縁体12が充填されている。n-拡散領域5の直下には、p-埋め込み層13が形成されている。n-型半導体領域3の領域には、高電位が印加されるn+拡散領域14が形成され、抵抗Rを有する配線20によってn-拡散領域5と電気的に接続されている。n+拡散領域8とn-拡散領域5とによって挟まれたp拡散領域7の部分の表面上には、ゲート絶縁膜19を介在させてゲート電極17が形成されている。

(もっと読む)

1 - 20 / 37

[ Back to top ]