Fターム[5F058BF11]の内容

Fターム[5F058BF11]の下位に属するFターム

スパッタ (401)

蒸着(電子ビーム加熱等を含む) (72)

イオンプレーティング (10)

イオンビーム蒸着 (17)

MBE (19)

Fターム[5F058BF11]に分類される特許

1 - 20 / 44

半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

構造健全性の監視を目的としたナノ粒子インクによる圧電センサの分散ネットワークのための方法及びシステム

【課題】構造物の表面に配置されたナノ粒子センサを利用した構造健全性監視の方法及びシステムを提供する。

【解決手段】構造物30の構造健全性172を監視するシステム170は、構造物30の上に沈着されるナノ粒子インクによる圧電センサアセンブリの分散ネットワーク120を含む。各アセンブリは、ナノ粒子インクによる複数の圧電センサ110及び複数の導電性インク電源及び複数のセンサ110を相互接続する通信線アセンブリ140を有する。このシステムはさらに、構造物30の上にナノ粒子インクによる圧電センサアセンブリの分散ネットワークを沈着させるインク沈着装置142を含む。このシステムはさらに、分散ネットワーク120に電力を供給する電源178を有する。このシステムはさらに、センサ110から一又は複数の信号を介して構造物の構造健全性データ174を読み出して処理するデータ通信ネットワーク179を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

成膜法及び成膜装置

【課題】粉末噴射コーティング法を用いて誘電体層を形成する成膜法及び成膜装置において、誘電体層の膜厚ムラを低減させる。

【解決手段】本発明に係る成膜法は、粉末噴射コーティング法を用いて、シート基材5の表面上に誘電体層を形成する方法であり、工程(a)と工程(b)とを有している。工程(a)では、シート基材5の表面を凸面状又は凹面状に湾曲させる。工程(b)では、シート基材5の湾曲した表面上に、粉末噴射コーティング法を用いて誘電体粉末を堆積させることにより、誘電体層を形成する。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタに関する新規な製造方法を提供する。

【解決手段】基板上に、非晶質酸化物層を形成する前に、基板表面にオゾン雰囲気中で紫外線を照射したり、基板表面にプラズマを照射したり、あるいは基板表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物を含み構成される活性層を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板上に、非晶質酸化物層を形成する後に、非晶質酸化物層の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

多孔性絶縁体及び電界効果トランジスタ

【課題】例えば、チタン酸ストロンチウムを活性層とした電界効果トランジスタのゲート絶縁体としても使用することのできる、新規な絶縁体を提供することを目的とする。

【解決手段】絶縁性を示す材質中に直径5〜100nmである空孔を複数有し、全体の体積に対する前記空孔の占める体積の割合である空孔率が20体積%以上であり、前記空孔には水分が含まれ、前記空孔の体積に対する前記水分の占める体積の割合である水分占有率が23〜100体積%である多孔性絶縁体を使用する。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

膜厚測定用標準試料、その製造方法、膜厚測定方法および半導体装置の製造方法

【課題】膜厚測定に用いる標準試料中のLaを含む膜の保管時の安定性を向上させる。

【解決手段】膜厚測定用標準試料100は、シリコン基板101上に設けられたLa含有膜103およびLa含有膜103の上部に設けられてLa含有膜103を覆うとともに金属窒化物を含む保護膜105を含む。これにより、Laを含む膜103の保管時の変質による膜厚変動を効果的に抑制する。このような膜厚測定用標準試料100を用いて、Laを含む膜の膜厚の測定値を補正するステップを含む、膜厚測定方法。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】多孔質ゲート絶縁層を設けることにより基板に発生する熱応力を低減し、基板の割れを防止することが可能な半導体デバイスおよびその製造方法を提供すること。

【解決手段】基板上に形成されたゲート電極およびゲート絶縁層上にソース電極及びドレイン電極並びに電極間を接続する半導体層を有し、ゲート絶縁層を挟んでゲート電極と反対側にソース電極、ドレイン電極とが配置された半導体素子において、多孔質ゲート絶縁層を設けることにより基板に発生する熱応力を低減し、基板の割れを防止する。

(もっと読む)

半導体装置の製造方法

【課題】塗布法や堆積法を用いて高品質な絶縁部材を半導体素子周辺に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上に、Si系絶縁材料からなる絶縁膜10を付加的に形成する工程と、絶縁膜10上に触媒金属膜11を形成する工程と、触媒金属膜11を触媒として用いて絶縁膜10に酸化処理を施す工程と、酸化処理を施した絶縁膜10を加工してゲート絶縁膜4を形成する工程と、ゲート絶縁膜4を含むMOSFET1を形成する工程と、を含む。

(もっと読む)

電磁気素子の製造方法

【課題】レジスト残渣に起因するリーク電流の増大を生じさせることがなく、微細パターンの形成が可能であり、電極のエッジ部分の絶縁膜が薄くなることに起因するリーク電流の増大を抑制することが可能な電磁気素子の製造方法を提供すること。

【解決手段】基板上に、12(CaxSr1-x)O・7Al2O3(0≦x≦1)を含む絶縁膜を形成する絶縁膜形成工程と、絶縁膜の上にアンモニウム塩アルカリ溶液を含む現像液で現像可能な第1フォトレジストを塗布し、第1フォトマスクパターンに応じて第1フォトレジストを露光する第1フォトレジストパターン形成工程と、第1フォトレジストをアンモニウム塩アルカリ溶液を含む現像液に接触させ、第1フォトレジストの可溶部分の溶解と同時に、絶縁膜をエッチングする現像・エッチング工程とを備えた電磁気素子の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】同一基板上に複数のゲート絶縁膜を有する半導体装置において、例えばコア部におけるHPトランジスタの高速性の確保と、例えばI/Oトランジスタ及びLPトランジスタのゲート耐圧の向上やゲートリーク電流の低減とを両立する。

【解決手段】半導体装置は、半導体基板11上に形成された複数のゲート絶縁膜を備えており、複数のゲート絶縁膜のうち、HPトランジスタ形成領域1Cにおける膜厚が最も薄いゲート絶縁膜は、シリコン酸化膜20よりなり、I/Oトランジスタ形成領域1A及びLPトランジスタ形成領域1Bにおける残りのゲート絶縁膜は、シリコン酸窒化膜16、17よりなる。

(もっと読む)

半導体装置

【課題】電気的性質が良好なhigh−k膜/Geゲートスタック構造を有する半導体装置を提供する。

【解決手段】Geを主成分とする半導体領域(10)と、前記半導体領域上に形成された絶縁膜(11)と、前記絶縁膜上に形成された金属膜(12)とを具備する半導体装置である。前記絶縁膜は、少なくとも1種の希土類元素(MR)と、TiおよびZrから選択される少なくとも1種のIV族元素(MIV)と、酸素とを含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、良好な移動度を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 第一の発明の半導体装置は、基板と、基板表面に形成され、Geを主成分とする半導体領域と、半導体領域上に形成された非金属Ge化合物層と、非金属Ge化合物層上に形成された絶縁膜と、絶縁膜上に形成された電極と、前記電極を挟む前記基板表面に形成されたソース・ドレイン領域とを備えることを特徴とする。非金属Ge化合物層は、例えばSrとGeの化合物、BaとGeの化合物もしくはBaとSiとGeの化合物を有する。

(もっと読む)

強誘電体膜、圧電素子、及び液体吐出装置

【課題】バイポーラ分極−電界曲線がダブルヒステリシス性を示し、大きな変位が期待される新規な強誘電体膜を提供する。

【解決手段】強誘電体膜は、最大印加電界Emaxと最小印加電界Eminの絶対値とを同一に設定して(Emax=|Emin|)測定されるバイポーラ分極−電界曲線が、少なくとも5個の変曲点を有し、かつ、最大分極値Pmaxと最小分極値Pminの絶対値とが略等しい(Pmax≒|Pmin|)ダブルヒステリシス性を有するものである。強誘電体膜は、1種又は2種以上のペロブスカイト型酸化物からなり、不可避不純物を含んでいてもよい。

(もっと読む)

ペロブスカイト型酸化物膜、強誘電体、圧電素子、液体吐出装置

【課題】通常ペロブスカイト型構造をとりにくい、または結晶性が悪化するBi系ペロブスカイト型酸化物を含み、強誘電性能(圧電性能)に優れたペロブスカイト型酸化物膜を提供する。

【解決手段】本発明のペロブスカイト型酸化物膜は、下記一般式(P1)で表されるペロブスカイト型酸化物を含むことを特徴とするものである。

(A1−x,Bx)(Cy,D1−y)O3 ・・・(P1)

(式中、0<x<1−y、0<y<1.0、AはBiを主成分とするAサイト元素、BはDとペロブスカイト構造を取る、Aとは異なる少なくとも1種のAサイト元素、CはAとペロブスカイト構造をとる元素を主成分とするBサイト元素、DはAとペロブスカイト構造を取り得ない、又は取りにくい少なくとも1種のBサイト元素。B〜Dは各々平均イオン価数3価の金属元素であるが,ペロブスカイト構造を取り得る範囲内でずれてもよい。)

(もっと読む)

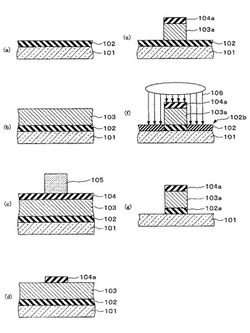

NAND型不揮発性半導体メモリ装置およびその製造方法

【課題】アルミニウム酸化物膜をブロック絶縁膜とする高性能なMONOS型のNAND型不揮発性半導体メモリ装置およびその製造方法を提供する。

【解決手段】半導体基板に、直列接続された複数のメモリセルトランジスタと、選択トランジスタを備えるNAND型不揮発性半導体メモリ装置である。メモリセルトランジスタは、半導体基板上の第1の絶縁膜102aと、電荷蓄積層104と、アルミニウム酸化物である第2の絶縁膜106aと、第1の制御ゲート電極108aと、第1のソース/ドレイン領域を有する。選択トランジスタは、半導体基板上の第3の絶縁膜102bと、アルミニウム酸化物であり、4価カチオン元素、5価カチオン元素、N(窒素)のうち少なくとも1種の元素を含有する第4の絶縁膜106bと、第2の制御電極108bと、第2のソース/ドレイン領域を有する。

(もっと読む)

窒化アルミニウム薄膜およびその製造方法

【課題】平坦で薄いAlN薄膜およびその製造方法を提供する。

【解決手段】AlN薄膜2は、III族元素、IV族元素およびV族元素から選ばれた1種以上の添加元素を0.001wt%以上10wt%以下含む。該AlN薄膜2は、III族元素、IV族元素およびV族元素から選ばれた1種以上の添加元素を0.001wt以上10wt%以下含むAlN焼結体を真空チャンバ内にセットし、基材1を真空チャンバ内にセットした状態で、AlN焼結体にレーザを照射することで発生したプラズマを用いて基材1上に形成可能である。

(もっと読む)

1 - 20 / 44

[ Back to top ]