Fターム[5F058BF72]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜の形成法 (10,542) | 基板、処理対象等の直接変換 (1,722) | プラズマ処理 (498)

Fターム[5F058BF72]の下位に属するFターム

Fターム[5F058BF72]に分類される特許

1 - 20 / 23

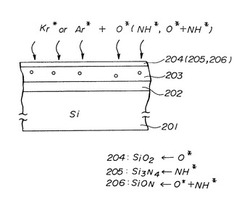

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

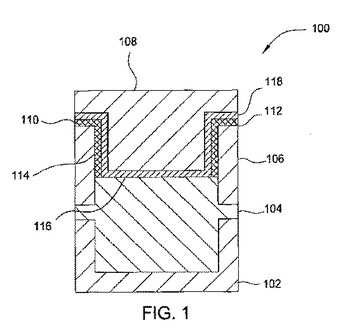

単一ステップによる選択的窒化の方法および装置

半導体基板を選択的に1ステップで窒化するための方法および装置が提供される。窒素は、選択的窒化プロセスを利用することにより、シリコン領域および酸化ケイ素領域を有する半導体基板のシリコン領域中に選択的に組み込まれる。窒素含有プラズマを形成し、このプラズマからイオンをフィルタリングまたは除去することにより、基板に窒素含有ラジカルが向けられてもよく、または、選択前駆体を使用する熱窒化プロセスを実施してもよい。遠隔プラズマジェネレータが、1つまたは複数のイオンフィルタ、シャワーヘッド、およびラジカル分配器を任意に備える処理チャンバに結合されてもよく、または、in situプラズマが生成され、1つまたは複数のイオンフィルタもしくはイオンシールドが、チャンバ内においてプラズマ発生ゾーンと基板支持体との間に配設されてもよい。  (もっと読む)

(もっと読む)

窒化膜の形成方法、酸窒化膜の形成方法、窒化膜のスパッタリング方法、ゲート絶縁膜の形成方法

【課題】実質的なリーク電流を生じることなく膜厚を減少させることができる高品質で均一な酸化膜、窒化膜あるいは酸窒化膜の形成方法を提供する。

【解決手段】基板上に絶縁膜を形成する工程と、前記絶縁膜をKrあるいはArを不活性ガスとしたプラズマに伴い生成された原子状酸素O*あるいは原子状窒化水素NH*に曝し、膜質を改変する工程とよりなる絶縁膜の形成方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】直接トンネル電流が流れる程度に薄膜化されたゲート絶縁膜におけるゲート電極からのドーパント原子の基板への拡散を防止すると共に、ゲートリーク電流を低減できるようにする。

【解決手段】第1の素子形成領域51及び第2の素子形成領域52に区画された半導体基板11上に、酸化膜からなる第1のゲート絶縁膜13Aを形成する。次に、第1のゲート絶縁膜13Aの第2の素子形成領域52に含まれる部分を除去し、半導体基板11に対して酸窒化性雰囲気で熱処理を行なうことにより、第2の素子形成領域52上に膜厚が第1のゲート絶縁膜13Aよりも小さい酸窒化膜からなる第2のゲート絶縁膜15Bを形成する。次に、第1のゲート絶縁膜13B及び第2のゲート絶縁膜15Bを窒素プラズマに暴露することにより、窒素原子をさらに導入された第1のゲート絶縁膜13C及び第2のゲート絶縁膜15Cを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタ及びセレクトトランジスタともに良好な特性を有する優れた半導体装置を提供する。

【解決手段】半導体基板10上に設けられた第1の下層絶縁膜20aと、第1の下層絶縁膜上に設けられた第1の中間絶縁膜30aと、第1の中間絶縁膜上に設けられた第1の上層絶縁膜40aと、第1の上層絶縁膜上に設けられた第1のゲート電極50aと、を有するメモリセルトランジスタ100aと、半導体基板上に設けられた第2の下層絶縁膜20bと、第2の下層絶縁膜上に設けられた第2の中間絶縁膜32bと、第2の中間絶縁膜上に設けられた第2の上層絶縁膜40bと、第2の上層絶縁膜上に設けられた第2のゲート電極50bと、を有するセレクトトランジスタ100bと、を備え、第2の中間絶縁膜32bのトラップ密度は、第1の中間絶縁膜30aのトラップ密度よりも低い。

(もっと読む)

絶縁膜、およびこれを用いた半導体装置

【課題】リーク電流を減少させることのできる絶縁膜を提供することを可能にする。

【解決手段】金属と、水素と、窒素とを含む非晶質の酸化物誘電体膜を有し、前記酸化物誘電体膜内の前記窒素の含有量[N]および前記水素の含有量[H]は、

{[N]−[H]}/2≦1.0×1021cm−3

を満たす。

(もっと読む)

絶縁膜の形成方法

【課題】高誘電率ゲート絶縁膜としての使用に適する高誘電率絶縁膜を良好な制御性をもって生産性良く形成する。

【解決手段】シリコン基体101の表層部を酸化してシリコン酸化膜102とする第1工程と、非酸化性雰囲気中においてシリコン酸化膜102の上に金属膜103を形成する第2工程と、非酸化性雰囲気中で金属膜103を希ガスプラズマに暴露することで、金属膜103を構成する金属原子をシリコン酸化膜102中に拡散させる第3工程と、金属原子が拡散したシリコン酸化膜102をラジカル酸化により酸化し、金属シリケート膜104を形成する第4の工程と、を備える。希ガスプラズマは金属膜103を構成する金属原子の原子量に最も近い原子量を有する希ガスを含む。

(もっと読む)

基板処理装置

【課題】低温で薄膜を形成した場合であっても、高品質な薄膜が形成できる半導体デバイスの基板処理装置を提供する。

【解決手段】ウエハ200を収容する処理室201内に第1の反応物質を供給し、ウエハ200の表面に存在する反応サイトとしての配位子と、第1の反応物質の配位子とを、配位子交換反応させる工程と、処理室201内に第2の反応物質を供給し、交換された後の配位子を反応サイトへ配位子交換反応させる工程と、処理室201内にプラズマにより励起された第3の反応物質を供給し、反応サイトへと交換反応が行われなかった配位子を、反応サイトへ配位子交換反応させる工程と、をウエハ200表面に所望の厚さの膜が形成されるまで繰り返す。

(もっと読む)

真空処理装置および真空処理方法

【課題】高周波放電によってプラズマを励起させ、活性種を生成させる放電室3と、放電室3で生成された活性種による処理対象である基板10を収容する基板処理室4と、プラズマを放電室3に閉じ込めると共に、貫通孔5を介して活性種を放電室3から基板処理室4へと移動させることができる仕切り板2とを備えた真空処理装置において、放電室3内に生ずる活性種の数を増大させることで、基板処理室4へ移動する活性種の数を増大させて、もって処理効率を向上させる。

【解決手段】放電室3において高周波放電を生じさせる電極間の間隔を15〜25mmとし、高電力の高周波でプラズマを形成する。

(もっと読む)

半導体装置の製造方法

【課題】SiC基板上にSiO2膜を有する半導体装置の製造に際して、そのSiO2/SiC界面近傍の界面準位密度が低減するとともに、SiO2膜の密度を高めてそのSiO2膜の厚みを20〜100nm程度とすることが容易である半導体装置の製造方法を提供する。

【解決手段】本発明における半導体装置の製造方法は、(a)SiC基板上に珪素および酸素の原料ガスを供給してSiO2膜を堆積する堆積工程と、(b)前記SiO2膜を堆積した前記SiC基板を200℃以上かつ700℃未満の温度に設定し、酸素ラジカルを発生してラジカル酸化する酸化工程とを備える。

(もっと読む)

SiC形成方法、膜形成方法、チャンバへのSiC形成方法、半導体製造装置の製造方法、SiC形成装置及びこれらで形成された膜構造

【課題】基板上やチャンバ内壁面にSiCの形成を可能とする。

【解決手段】チャンバ10内の基板22aへ珪素を供給すると共に、チャンバ10内へハロゲン含有ガスを供給し、ハロゲン含有ガスを解離して炭素含有部材20bから基板22aへ炭素を供給することによって基板22aにSiCを形成する。

(もっと読む)

パターン形成方法、および半導体装置の製造方法

【課題】 微細化への対応が可能で、かつプラズマダメージが生じにくいパターン形成方法および半導体装置の製造方法を提供する。

【解決手段】 パターン形成方法は、被処理体上に第1の線幅を有する初期パターンが形成されたシリコン表面を、プラズマ処理装置の処理室内でプラズマ酸化処理し、初期パターンの表面にシリコン酸化膜を形成する表面酸化工程と、シリコン酸化膜を除去する酸化膜除去工程と、を繰り返し行なうことにより、被処理体上に、第1の線幅に比べ微細な第2の線幅を持つ目的のパターンを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SiC基板上に、通常のシリコン酸化膜形成技術によってゲート絶縁膜を形成した場合、良好な電気的な特性を持つゲート酸化膜が得られない。

【解決手段】SiC基板上におけるゲート絶縁膜中の炭素含有量を減少させることによって、ヒステリシスが小さく、高耐圧の膜を得ることができた。このため、プラズマ処理装置を用いて、SiC基板上にシリコン酸化膜を形成した後、窒素原子を含むラジカルに、形成されたシリコン酸化膜を曝して改質を行うことにより、電気的特性の優れたゲート絶縁膜を得ることができた。

(もっと読む)

ガス放出孔部材を一体焼結したシャワープレートおよびその製造方法

【課題】プラズマの逆流防止のためにシャワープレートの縦孔内に配置されるガス放出孔部材(セラミックス部材あるいは多孔質ガス流通体)が隙間無く一体的に焼結結合され、シャワープレートの使用時に縦孔から脱落することがなく、また各縦孔からのガス放出量のバラツキがなく、プラズマの逆流の発生をより完全に防止でき、効率の良いプラズマ励起が可能なシャワープレートを提供すること。

【解決手段】プラズマ処理装置の処理室102に配置され、処理室102にプラズマを発生させるためにプラズマ励起用ガスを放出するシャワープレート105において、プラズマ励起用ガスの放出経路となる多数個の縦孔105内に、孔径が20μm乃至70μmのガス放出孔を複数個有するセラミックス部材、および/または最大気孔径が75μm以下のガス流通方向に連通した気孔を有する多孔質ガス流通体を一体的に焼結結合して配置した。

(もっと読む)

モデル作成方法ならびに半導体製造プロセスの結果分析方法及び記録媒体

【課題】 プロセスの物理・化学的なメカニズムに基づいて高精度かつ計算負荷の小さいモデルを作成することができるモデル作成方法を提供すること

【解決手段】 物理化学モデルで表されたプロセス(シリコン酸化プロセス)のうちの一部分(酸化種の濃度)についてシミュレーションを実行する。得られたシミュレーション結果を近似により第1の数式モデルに変換する。また、プロセスのうちシミュレーションを実行したプロセス以外の部分(ウェハ表面での酸化膜成長)を表す数式を近似して第2の数式モデルに変換する。次いで、第1の数式モデルと第2の数式モデルを合成してプロセス全体のモデルを表す第3の数式モデルを求める。

(もっと読む)

真空処理装置

【課題】 光学窓のクリーニング効果を従来よりもさらに高めて、メインテナンス周期を飛躍的に増大させることができる真空処理装置を提供すること。

【解決手段】 真空処理装置は、真空処理室10と、真空処理室10の壁部12に配置された透光性部材22を有する光学窓20と、真空処理室の内側にて透光性部材22の周縁側に配置された、第1開口14を有する接地電極12と、真空処理室10の外側にて透光性部材22の周縁側に配置された、第1開口14と対向する第2開口32を有するRF電極30とを有する。真空処理室10内に処理用ガスが導入され、RF電極30及び接地電極12間の電界によってプラズマを生成し、負の自己バイアス電位Vfに帯電された透光性部材22をプラズマ中のイオンによりスパッタしてクリーニングする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】フッ素添加カーボン膜からハードマスク層へのフッ素の突き抜けを抑え、熱処理後のハードマスク層の膜剥がれを抑える技術を提供する。

【解決手段】基板1上に形成されたフッ素添加カーボン膜20と、このフッ素添加カーボン膜20の上に形成され、SiCO膜23とSiO2膜24とを含むハードマスク層と、前記フッ素添加カーボン膜20とハードマスク層との間に、SiN膜21とSiCN膜22とを下からこの順序で積層して形成されたバリア層と、を備える。SiN膜21によりフッ素添加カーボン膜からハードマスク層へのフッ素の突き抜けが抑えられ、SiCN膜22によりハードマスク層の成膜プロセス時のフッ素添加カーボン膜20の酸化を抑えることができるので、熱処理後のハードマスク層やバリア層の膜剥がれを抑えることができる。

(もっと読む)

プラズマ処理装置及びそれに用いる基板加熱機構

【課題】パーティクル及びコンタミネーションによる汚染を抑制しつつ被処理基板を800℃以上の高温に安定して加熱することができるプラズマ処理装置及び基板加熱機構を提供する。

【解決手段】マイクロ波プラズマ処理装置は、基板載置台7、支持部8、支持部固定部24を備える。基板載置台7は発熱体74を内蔵する。発熱体74及び電極32は、SiCを含む材料からなり、電極32は、支持部固定部24に固定されるとともに、支持部8を貫通し、かつ先端部が発熱体74に接続されている。そして、石英を含む絶縁材料からなる電極被覆管43が、電極32の先端部以外の部分を被覆し、基板載置台7の発熱体74の下方部分、支持部8、及び支持部固定部24を貫通するように設けられている。

(もっと読む)

基板処理方法および基板処理装置

【課題】シリコン基板表面に形成された酸化膜をプラズマ窒化処理により窒化し、酸窒化膜に変換する際に、窒化処理に伴って生じる酸化による膜厚増大を抑制する。

【解決手段】基板処理方法は、シリコン基板表面を酸化処理することにより、酸化膜を形成する工程と、前記酸化膜を窒化処理することにより、酸窒化膜を形成する工程と、前記酸化処理工程の後、前記窒化処理工程の前に、前記シリコン基板表面から、酸素を排除する工程を含み、前記酸素を排除する工程は、加熱処理またはプラズマ処理により、前記酸化処理を行う処理室および前記窒化処理を行う処理室のいずれとも異なる処理室に前記シリコン基板を導入して実行され、前記酸素を排除する工程の後、前記シリコン基板は前記窒化処理を行う処理室に、真空搬送路を介して搬送される。

(もっと読む)

工程管理システム、工程管理方法及び半導体装置の製造方法

【課題】 同一のウェハに対して、互いに異なる処理を実行する2つの工程間の処理待ち時間を最小にすることができる工程管理システムを提供する。

【解決手段】 複数ロットを並列に処理する工程管理システムであって、同一のウェハ9に対して、互いに異なる処理を大気に晒さず連続して実行する第1及び第2の半導体製造装置31,32と、第1及び第2の半導体製造装置31,32のそれぞれの処理時間を記載したレシピのデータを格納するレシピ記憶部21と、レシピのデータに基づいて、第1及び第2の半導体製造装置間31,32の処理待ち時間が最小となるように、第1及び第2の半導体製造装置31,32のそれぞれの処理時刻を決定する処理時刻決定手段13と、決定された第1及び第2の半導体製造装置31,32のそれぞれの処理時刻に、第1及び第2の半導体製造装置31,32に並列に処理させる装置制御手段14とを備える。

(もっと読む)

1 - 20 / 23

[ Back to top ]