Fターム[5F064AA04]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | カスタムIC (1,426) | セミカスタムIC (1,415) | 標準セル、スタンダードセル (922)

Fターム[5F064AA04]の下位に属するFターム

ポリセル (86)

ビルディングブロック (241)

Fターム[5F064AA04]に分類される特許

1 - 20 / 595

スタンダードセル、および、半導体集積回路

半導体装置

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

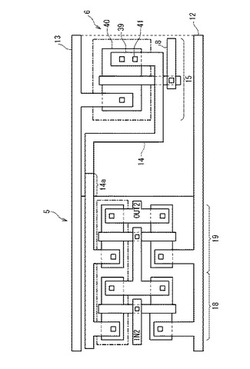

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】半導体装置の歩留まりが低下することを抑制する。

【解決手段】配線パターンを示す配線パターンデータを取得する(ステップS10)。次いで、配線パターンデータを解析して、第1方向パターン及び第2方向パターンを特定する(ステップS20)。第1方向パターンは、第1の方向に延伸するパターンであり、第2方向パターンは、第1の方向に直交する方向に延伸するパターンである。次いで、第1方向パターと第2方向パターンの交点を検出する。そして、この交点から延伸するパターンのうち、ビア、コンタクト及び他のパターンのいずれにも接続していないパターンを不要パターンとして検出し、検出した不要パターンを除去する(ステップS30)。そしてその後、設計した配線パターンに対して光近接効果補正を行う(ステップS40)。

(もっと読む)

半導体設計装置、半導体設計方法及びプログラム

【課題】信号の重要度を考慮に入れたセルの自動配置を行うアルゴリズムは存在しない。従って、重要配線が不必要に長くなる場合がある。重要配線が長くなると、重要配線を伝達する信号を劣化させる原因となり得る。そのため、信号の重要度を考慮に入れたセルの自動配置を行うことで、重要度の高い信号の品質を維持する半導体装置を設計できる半導体設計装置、が望まれる。

【解決手段】半導体設計装置は、半導体装置に含まれる複数のセルを接続する複数の信号配線から、伝達する信号が重要であることを示す重要配線情報が付された重要配線と、複数の信号配線のそれぞれに接続されているセルの数を示すセル接続数と、を抽出する配線情報抽出部と、配線情報抽出部が抽出した重要配線及びセル接続数に応じて、複数のセルの配置を決定するセル自動配置部と、を備えている。

(もっと読む)

配線支援方法及び装置

【課題】配線すべき複数の信号線を、ユーザの指定する目的に従って適切にグループ化する。

【解決手段】配線すべき複数の信号線を複数のグループに分けるための方法は、ユーザから、複数の信号線のグループ化の条件の指定を受け付けるステップと、指定された、グループ化の条件と、データ格納部に格納されている、複数の信号線の始点端子群と終点端子群との配置パターンとに基づいて、複数の信号線のグループ化の処理を切り替えて実施する実施ステップとを含む。

(もっと読む)

半導体集積回路の設計装置、及び半導体集積回路の設計方法

【課題】チップサイズを縮小することができる、半導体集積回路の設計装置、及び半導体集積回路の設計方法を提供する

【解決手段】下位階層の機能ブロック4に配置された複数のセル間を接続する第一の配線を設計する下位階層配線設計部311と、上位階層の機能ブロック間を接続する第二の配線を設計する上位階層配線設計部312とを備えており、下位階層配線設計部311は、機能ブロック4を複数の小領域4aに分割し、小領域4aごとに機能ブロック4内配線に必要となる必要配線層数Lnを算出して、最下部の配線層から必要配線層数Ln枚の配線層を配線可能領域として同領域内に第一の配線を配置し、上位階層配線設計部312は、第一の配線における配線可能領域以外の機能ブロック4の配線層に第二の配線を配置する。

(もっと読む)

半導体設計装置、半導体設計方法及びプログラム

【課題】レイアウトデータの検証を行うLVS処理やDRC処理と、OPC処理には、プログラムの実装に重複(冗長)な処理が存在する。そこで、これらの処理を、統合することも考えられる。しかし、そのような統合を実際に行えば、プログラムの変更が大規模になり、半導体設計装置のコストを上昇させてしまう。そのため、既存のリソースを有効活用しつつ、OPC処理の処理スピードを向上させた半導体設計装置が、望まれる。

【解決手段】半導体設計装置は、半導体集積回路のレイアウトデータの検証を行うレイアウトデータ検証部と、レイアウトデータ検証部が生成するOPC処理用中間データを用いて、OPC処理を行うOPC処理部と、を備えている。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

半導体集積回路のレイアウト方法、レイアウト装置およびプログラム

【課題】複数の階層ブロックが互いに重なり合うことを許容しつつレイアウト設計を行う際に、設計期間の長期化を防ぐこと。

【解決手段】複数の内部要素をそれぞれ含む複数の階層ブロックを、内部要素を割り当て可能な内部要素リソースが配置された実装領域に対してレイアウトする場合に、第1の階層ブロックと第2の階層ブロックとが重複領域において重なり合うとき、第1の階層ブロックの内部要素のうちの重複領域に含まれる第1の内部要素の個数と、第2の階層ブロックの内部要素のうちの重複領域に含まれる第2の内部要素の個数との合計が、重複領域に含まれる内部要素リソースの個数以下となるように、第1の階層ブロックおよび第2の階層ブロックを配置し、第1の内部要素の個数と第2の内部要素の個数との比に応じて、重複領域に含まれる内部要素リソースを、第1の階層ブロックと第2の階層ブロックに割り当てる。

(もっと読む)

配置配線装置

【課題】効率的にIR−Dropを防止することが可能な配置配線装置を提供すること。

【解決手段】複数のセルを配置した後、セル間の隙間が所定の大きさよりも小さい場合にはセル間の隙間が所定の大きさ以上となるようにセルの配置を変更する(S17)。そして、配置された複数のセルの間に容量セルを挿入し(S15)、配置された複数のセルの配線を行なう(S14,S16)。したがって、効率的にIR−Dropを防止することが可能となる。

(もっと読む)

半導体集積回路装置

【課題】チップ面積を増加させることなく、効率良くリーク電流を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は論理が同一のセルA−1,B−1,C−1を備えている。セルB−1はセルA−1よりセル幅W2が大きいが、MOSトランジスタのゲート長L1はセルA−1と等しい。セルC−1は、セルB−1とセル幅W2が等しいが、ゲート長L2が大きいMOSトランジスタを有しており、セルA−1,B−1と比べて回路遅延は遅くなるがリーク電流は小さくなる。このため例えば、空き領域に隣接したセルA−1をセルB−1に置き換え、タイミングに余裕があるパスにおけるセルB−1をセルC−1に置き換えることによって、チップ面積を増加させることなく、リーク電流を抑えることができる。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

ネットリスト変換装置、論理合成装置及びコンピュータプログラム

【課題】半導体集積回路の開発期間を短縮し、且つ、レイアウトエラー確率を低減する。

【解決手段】本発明の実施形態のネットリスト変換装置は、半導体集積回路を構成する複数のセルであって、第1遅延時間だけスキャン用データ信号を遅延させる第1スキャンフリップフロップを含む複数のセルの接続関係を示すネットリストを変換する。そのようなネットリスト変換装置は、論理ライブラリ30と、ネットリスト変換部18と、を備える。論理ライブラリ30は、半導体集積回路を構成する複数のセルの論理的機能を示す情報を含むセル論理情報であって、第1スキャンフリップフロップの論理的機能を示す情報と、第1遅延時間より大きいスキャン用第2遅延時間だけデータ信号を遅延させる第2スキャンフリップフロップの論理的機能を示す情報と、を含むセル論理情報を記憶する。ネットリスト変換部18は、セル論理情報を参照して、ネットリストの第1スキャンフリップフロップを第2スキャンフリップフロップに置換する。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

1 - 20 / 595

[ Back to top ]