Fターム[5F064BB00]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082)

Fターム[5F064BB00]の下位に属するFターム

Fターム[5F064BB00]に分類される特許

1 - 3 / 3

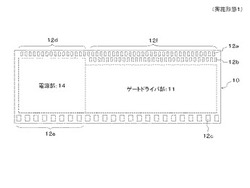

半導体装置

【課題】圧接時のバランスを保つために補強用のダミー端子を設けたとしても、チップ上により多くの回路素子を設けることができるようにすること。

【解決手段】COG実装に用いられる半導体装置10であって、チップの一の端部の近傍に第1のパターンで配置された出力端子群12fと、チップの一の端部の近傍であって出力端子群12fが配置された領域とは別の領域に配置されるとともに、第1のパターンと異なる第2のパターンで配置されたダミー端子12dと、を備える。第2のパターンは、第1のパターンよりも幅が狭く構成される。ダミー端子12dの近傍であって出力端子群12fの長さ方向の隣に電源部14が配される。

(もっと読む)

プログラム可能論理装置及びその論理回路構成方法

【課題】プログラマブル論理装置おいて、相互接続配線の交差部のスイッチング素子に、オン・オフの制御信号を送信する制御配線の数を大幅に削減する手段を提供する。

【解決手段】入出力リードを備えた複数個の論理素子、該論理素子間を相互に接続する相互接続線、前記入出力リードを前記相互接続線に第1制御信号によって接続させる第1接続手段と、前記相互接続線を互いに第2制御信号によって接続させるプログラム可能な第2接続手段とを備えたプログラム可能論理装置において、前記第1制御信号及び/又は第2制御信号がアナログ多値信号であることを特徴とするプログラム可能論理装置。また、前記第1接続手段及び/又は前記第2接続手段が、アナログ多値信号を1組のディジタル信号に変換するA/D変換手段を含む上記の装置。

(もっと読む)

半導体装置

【課題】 チップ面積を増加させずに、半導体チップの主面上に占める配線領域を拡大する。

【解決手段】 半導体チップの主面上に形成された例えばMISトランジスタなどを含んで構成される内部回路7から、例えばダイオードからなる保護素子11および保護素子12に電気的に接続する信号配線8を保護素子11と保護素子12との間の配線13上の取り出し口29から引き出して、信号配線8が占める信号配線領域10を、保護素子12上および電極パッド9下に設ける。

(もっと読む)

1 - 3 / 3

[ Back to top ]