Fターム[5F064CC06]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639) | FET (1,516)

Fターム[5F064CC06]の下位に属するFターム

JFET (4)

ショットキFET (1)

MOS−FET(MISも含む) (1,456)

ディプレッション、エンハンスメント型の特定 (6)

Fターム[5F064CC06]に分類される特許

1 - 20 / 49

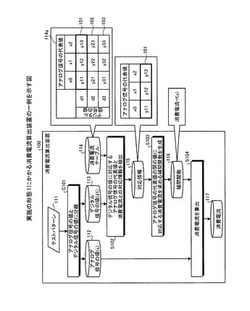

消費電流算出装置、消費電流算出プログラムおよび消費電流算出方法

【課題】ミックスドシグナル回路の消費電流を短時間で見積もること。

【解決手段】消費電流算出装置100は、対象回路へ入力されるデジタル信号の値113と、デジタル信号とともに対象回路へ入力されるアナログ信号の値112と、を取得する。消費電流算出装置100は、デジタル信号の値113およびアナログ信号の代表値の組み合わせごとに組み合わせが入力された場合の対象回路の消費電流を示す消費電流テーブル114から、デジタル信号の値113が対象回路へ入力された場合のアナログ信号の各代表値と消費電流との対応情報115を抽出する。消費電流算出装置100は、抽出した対応情報115に基づいて、アナログ信号の各代表値の間の値に対応する対象回路の消費電流を補間する補間関数116を生成し、生成した補間関数116に基づいて、アナログ信号の値112に対応する対象回路の消費電流117を算出する。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

スイッチング電源回路方式判定処理方法,CAD装置およびCADプログラム

【課題】 CAD装置で,スイッチング電源回路の方式を自動的に判別することを目的とする。

【解決手段】 CAD装置1は,判別対象とするスイッチング電源回路が配置されている基板に実装される部品およびネットの情報を示す実装CAD情報2,ならびに前記基板に配置される各部品の部品種別,部品内部の透過接続情報およびピン属性を示す部品情報3をもとに,スイッチング電源回路から開始かつ終了する経路を抽出し,該経路に接続する部品および接続関係を示すスイッチング電源回路経路情報14を生成する経路情報抽出部13と,スイッチング電源回路の経路に接続する部品および接続関係にもとづいてスイッチング電源回路の方式を定める条件をもとに,スイッチング電源回路経路情報14から,判定対象のスイッチング電源回路の方式を判定する回路方式判定部15とを備える。

(もっと読む)

プログラマブルLSI

【課題】低消費電力で、且つ、動的コンフィギュレーションにも対応できる高速なコンフィギュレーションを可能とし、起動するための時間が短いプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントと、複数のロジックエレメントに入力するためのコンフィギュレーションデータを記憶するメモリエレメントと、を有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有し、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更し、メモリエレメントは、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードと、を有する記憶素子を用いて構成する。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置の設計装置、及びプログラム

【課題】ダミーゲートパターンを形成するためのレジストパターンが倒れることを抑制する。

【解決手段】ダミーゲートパターン220は、複数の第1のダミーゲート電極222と、第2のダミーゲート電極224を備えている。第1のダミーゲート電極222は、ゲート電極112と同一方向を向いている。第2のダミーゲート電極224は、第1のダミーゲート電極222とは異なる方向、例えば直交する方向を向いており、第1のダミーゲート電極222を他の第1のダミーゲート電極222に接続している。本実施形態において全ての第1のダミーゲート電極222は、第2のダミーゲート電極224によって、他の第1のダミーゲート電極222に接続されている。

(もっと読む)

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

品質優先回路抽出装置、品質優先回路抽出方法、品質優先回路抽出プログラム、マスク作成システム、及びレイアウト制約作成システム

【課題】レイアウト上での素子配置の規則性情報と組み合わせて、差動対回路やカレントミラー回路のようなマスク検査品質を優先する部分回路の抽出を図ること。

【解決手段】品質優先回路ネットリスト抽出装置3で抽出した品質優先回路のネットリスト情報(差動対回路、カレントミラー回路)と品質優先回路レイアウト抽出装置5で抽出した品質優先回路のレイアウト情報(行/列/アレイ構造)から、レイアウトデータに含まれる素子図形に対してマスク検査精度の優先順位を決定する。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

半導体集積回路のレイアウト検証方法

【課題】半導体集積回路のレイアウト修正に要する工数を減少させる。

【解決手段】レイアウト検証方法は、2つの検証領域のレイアウト図形を相互に比較することでレイアウト図形が相互に不一致となる不一致図形を取得する不一致図形取得工程(1000)と、不一致図形が2つの検証領域のうちいずれの検証領域に存在するかを判定する不一致図形判定工程(1100)と、不一致図形判定工程(1100)の結果に基づいて、2つの素子のうち、不一致図形が存在する検証領域における検証素子と不一致図形との距離である不一致距離を算出する不一致距離算出工程(1200)と、不一致距離に応じて、不一致図形が検証素子に及ぼす特性影響を算出する特性影響算出工程(7110)と、を備えている。

(もっと読む)

半導体デバイスモデルのモデルパラメータ抽出装置およびモデルパラメータ抽出プログラム

【課題】モデルの特性のたわみが無くなるようなモデルパラメータの抽出を実行する。

【解決手段】ビンニング処理を実行するビンニング処理部(18)と、ビンニング処理によって構成される複数のビンに対応してモデルパラメータを抽出するモデルパラメータ抽出部(11)とを具備するモデルパラメータ抽出装置(1)を構成する。モデルパラメータ抽出部(11)は、対象ビンの第1端部(A)に対応する第1モデルパラメータ(P2A)を抽出する。そして、対象ビンの第2端部(B)に対応する第2モデルパラメータ(P2B)の候補(P2B’)を、第1モデルパラメータ(P2A)に基づいて設定する。第1モデルパラメータ(P2A)と第2モデルパラメータの候補(P2B’)とに基づいて半導体デバイスの電気的特性を示す有限曲線の始点側傾斜と終点側傾斜とを特定し、それらの比較結果に基づいて、第2モデルパラメータ(P2B)を抽出する。

(もっと読む)

再構成可能集積回路

【課題】基本の回路要素の基本タイルの間の配線状態を設定する複数のプログラマブル配線スイッチが不揮発性記憶素子で構成される再構成可能集積回路を提供する。

【解決手段】再構成可能集積回路は、複数の入力端子と出力端子を備えるマルチプレクサ型のプログラマブル配線スイッチを構成する複数の不揮発性記憶素子を備える。入力端子から出力端子への信号電圧の伝搬経路にスイッチ機能を有する電界効果トランジスタ構造の不揮発性記憶素子が配置されており、不揮発性記憶素子が入力端子からの信号電圧を選択的に出力端子に伝搬するマルチプレクサ型のプログラマブル配線スイッチを構成するため、不揮発性記憶素子に対して導通状態もしくは非導通状態とする結線情報を記憶する書き込み動作、結線情報を消去する消去動作と、不揮発性記憶素子の導通状態もしくは非導通状態を確認する読み出し動作を直接行う制御回路を備える。

(もっと読む)

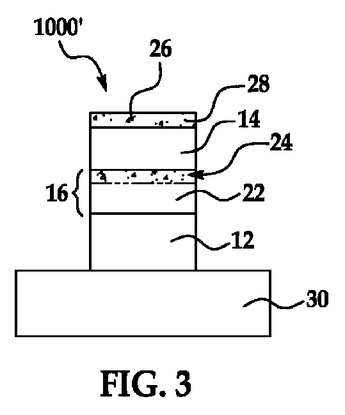

電気的に作動するデバイス及びそのデバイスにおけるドーパントの形成を制御する方法

電気的に作動するデバイスが、第1の電極、第2の電極並びに当該第1及び第2の電極間に堆積させた活性領域を備えている。当該デバイスは、i)第1の電極と活性領域との界面、又はii)第2の電極と活性領域との界面、又はiii)活性領域と第1及び第2の電極のそれぞれとの各界面で局在化された、少なくとも1つのドーパント導入剤又はドーパントをさらに含む。  (もっと読む)

(もっと読む)

集積回路設計方法、集積回路設計装置、集積回路及び電子機器

【課題】処理負荷の増大を抑えながら、これまで配線が混雑していた領域でも確実にセルや配線を配置できる集積回路設計方法等を提供する。

【解決手段】集積回路設計方法は、所与の領域を配線グリッド変更領域として設定する配線グリッド変更領域設定ステップと、前記配線グリッド変更領域設定ステップにおいて前記配線グリッド変更領域として設定された前記領域内の配線グリッドの間隔をより小さく変更する配線グリッド変更ステップと、前記領域内において、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに所与の配線を配置すると共に、前記配線グリッド変更ステップにおいて変更された前記配線グリッドの間隔に対応したセルグリッド間隔でその構成が指定されたセルを、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに配置する配置配線ステップとを含む。

(もっと読む)

集積回路設計方法及び集積回路設計装置

【課題】処理負荷の増大を抑えながら、所定のマクロブロック周辺において複数の配線の影響を確実に低減できる集積回路設計方法及び集積回路設計装置を提供する。

【解決手段】集積回路設計方法は、所与の領域を配線グリッド変更領域として設定する配線グリッド変更領域設定ステップと、前記配線グリッド変更領域設定ステップにおいて前記配線グリッド変更領域として設定された前記領域内の配線グリッドの間隔をより大きく変更する配線グリッド変更ステップと、前記領域内において、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに所与の配線を配置すると共に、前記配線グリッド変更ステップにおいて変更された前記配線グリッドの間隔に対応したセルグリッド間隔でその構成が指定されたセルを、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに配置する配置配線ステップとを含む。

(もっと読む)

半導体集積回路のマスクレイアウト検証方法

【課題】半導体集積回路の製造工程における設計パターンの微細化や回路の高密度化に伴い製造ばらつきが増加するなかで、半導体素子の配置やその周辺の状況が所望の通りであることを短時間で効率的に検証する。

【解決手段】条件入力工程109では、回路特性を同一に合わせるべき特定のレイアウトパターンが複数含まれるようなレイアウトパターン分割条件108を入力する。データ分割工程103では、入力されたマスクレイアウト設計データを前記レイアウトパターン分割条件に従って複数のレイアウトパターン群に分割する。基準パターン選択工程105では、前記複数に分割されたレイアウトパターン群毎に、パターンマッチングの基準となる基準パターンを選択する。パターンマッチング工程106では、各レイアウトパターン群別に、そのレイアウトパターン群内の各レイアウトパターンと前記基準パターンとを比較する。

(もっと読む)

移相器の拡張によるトランジスタエンドキャップにおけるラインエンド収縮の緩和

【課題】ラインエンド収縮を低減するのに好適なシステムおよび方法を提供すること。

【解決手段】本発明の1つの実施形態は、集積回路製造のための光学リソグラフィプロセスの間のラインエンド収縮を低減するシステムおよび方法を提供する。本システムは、集積回路の仕様を受取ることによって動作し、仕様は、ゲートを含むトランジスタを定義する。次に、本システムは、仕様内のゲートを識別し、ゲートは、光学リソグラフィイプロセスの間のラインエンド収縮を引き起こし易いエンドキャップを含む。続いて、本システムは、ゲートを形成するために使用される移相器を拡張し、その結果、移相器は、エンドキャップの少なくとも1部分を定義し、それによって、光学効果が原因となるエンドキャップのラインエンド収縮を低減する。

(もっと読む)

半導体回路の設計方法および製造方法

【課題】所望の回路特性に合致する半導体回路のレイアウトを効率的に取得する。

【解決手段】トランジスタの構成部品の設計図形パターンの寸法または部品パラメータをシミュレーション部に入力される模擬パラメータに変換する変換工程と、複数トランジスタを複数グループにグループ分けするグループ構成工程と、複数グループからいずれかの選択グループを選択する工程と、複数グループで選択グループ以外の非選択グループの部品パラメータとして固定のパラメータ値を設定する固定パラメータ設定工程と、選択グループにおいて部品パラメータの組み合わせを設定し、変換工程を通じてシミュレーションを実行し、それぞれの部品パラメータの組み合わせに対する回路特性を得るシミュレーション工程と、すでに選択グループに選択済みのグループとは別のグループを選択し、固定パラメータ設定工程からシミュレーション工程までを繰り返し実行する制御工程とを実行する。

(もっと読む)

1 - 20 / 49

[ Back to top ]