Fターム[5F064CC12]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639) | FET (1,516) | MOS−FET(MISも含む) (1,456) | CMOS (629)

Fターム[5F064CC12]に分類される特許

1 - 20 / 629

半導体集積回路

スタンダードセル、および、半導体集積回路

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】クロックツリーにおけるクロックスキューの調整において、精度の確保とデューティ保持とを両立させる。

【解決手段】レイアウト装置(10)において、MOSトランジスタ1段で形成された第1セルと、MOSトランジスタ複数段で形成された第2セルとがライブラリ化されたテーブルを設ける。また、上記レイアウト装置には、上記第1セルと上記第2セルとの組み合わせによるコンビネーションチェーンを上記クロックツリーに挿入することで、上記クロックツリーにおける異なるクロック系統間のクロックスキューを調整可能な演算処理部(12)を設ける。上記コンビネーションチェーンによってクロックスキューの調整を行うことで、個々の第1セルでの遅延誤差が伝播されるのを抑制し、遅延計算における遅延誤差の低減を図る。また、第1セルはMOSトランジスタ1段で形成され、そこで論理反転されるため、デューティ保持の観点で有利とされる。

(もっと読む)

半導体装置および半導体パッケージ

【課題】パッドが設けられた面の向きを変えても、パッドを基板に接続するボンディングワイヤが交差しない半導体装置を提供する。

【解決手段】複数のパッドを含む第1のパッド群と、第1のパッド群に平行に一列に配置された複数のパッドを含む第2のパッド群と、第1のパッド群を基準にして第2のパッド群とは反対側に設けられた複数のバッファ回路を含む第1のバッファ回路群と、第2のパッド群を基準にして第1のパッド群とは反対側に設けられた複数のバッファ回路を含む第2のバッファ回路群と、第1のパッド群の複数のパッドのそれぞれを第2のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第1の配線と、第2のパッド群の複数のパッドのそれぞれを第1のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第2の配線と、を有する。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

半導体チップ

【課題】チップ面積が小さく低コストで誤動作が発生し難い半導体チップを提供する。

【解決手段】半導体チップ1をパッケージ3に搭載する場合は80個のパッドPAをパッケージ3の80個の端子TAに接続し、半導体チップ1をパッケージ5に搭載する場合は100個のパッドPA,PB,PCをパッケージ5の100個の端子TAに接続する。半導体チップ1の内部回路は、電極E1,E2が絶縁されている場合は80端子のマイクロコンピュータ4として動作し、電極E1,E2がボンディングワイヤWの端部によって短絡されている場合は100端子のマイクロコンピュータ4として動作する。したがって、パッケージの端子数を設定する専用パッドが不要となる。

(もっと読む)

半導体集積回路システムおよび半導体集積回路システムの配置配線方法

【課題】EMI低減に有効な半導体集積回路システムを提供する。

【解決手段】バスライン8上に配置された中央演算処理装置1と、演算論理装置6と、デカップリングキャパシタ形成領域100・合成論理形成領域200・インピーダンス形成領域300を有する半導体集積回路400と、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26・電源配線配置配線情報格納部28を有する記憶装置2とを備え、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26のそれぞれの格納データに基づいて、それぞれ合成論理形成領域200・デカップリングキャパシタ形成領域100・インピーダンス形成領域300における配置配線を実行する半導体集積回路システム10。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

消費電力解析装置及び方法

【課題】 本発明の課題は、組み合せ回路を含めた電力解析を効率的かつ高速に行うことを目的とする。

【解決手段】 上記課題は、回路の動作記述の抽象度が異なる概要回路モデルと、該概要回路モデルより抽象度が低い詳細回路モデルとを含む回路データと、該回路の電力検証方法に係る動作シーケンス・データとを記憶する記憶部と、論理回路の動作シミュレーションを行う論理シミュレーション部に、前記前記概要回路モデルと前記詳細回路モデルとを含む前記回路データをロードし、該記憶部に記憶されている前記動作シーケンス・データに従って、該概要回路モデルによって前記動作シミュレーションを行わせる概要モードと、該詳細回路モデルによって該動作シミュレーションを行わせる詳細モードとを切り替えて、該論理シミュレーション部に該動作シミュレーションを行わせるシミュレーション制御部とを有することを特徴とする消費電力解析装置により達成される。

(もっと読む)

半導体集積回路装置

【課題】チップ面積を増加させることなく、効率良くリーク電流を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は論理が同一のセルA−1,B−1,C−1を備えている。セルB−1はセルA−1よりセル幅W2が大きいが、MOSトランジスタのゲート長L1はセルA−1と等しい。セルC−1は、セルB−1とセル幅W2が等しいが、ゲート長L2が大きいMOSトランジスタを有しており、セルA−1,B−1と比べて回路遅延は遅くなるがリーク電流は小さくなる。このため例えば、空き領域に隣接したセルA−1をセルB−1に置き換え、タイミングに余裕があるパスにおけるセルB−1をセルC−1に置き換えることによって、チップ面積を増加させることなく、リーク電流を抑えることができる。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

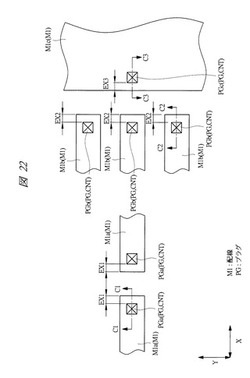

半導体装置

【課題】配線におけるエレクトロマイグレーション耐性を向上させる。

【解決手段】ソース領域42、ソース領域44およびドレイン領域46を有するP型MOSFET40と、ソース領域52、ソース領域54およびドレイン領域56を有し、かつP型MOSFET40と隣接するN型MOSFET50と、ドレイン領域46およびドレイン領域56に接続するドレイン電極と、ドレイン電極と接続し、かつドレイン電極上に設けられた複数のビア10と、を備え、P型MOSFET40とN型MOSFET50は、インバータ回路を構成しており、ドレイン電極は、ビア10を介しては、インバータ回路の出力信号配線30と接続し、他には接続していない。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

1 - 20 / 629

[ Back to top ]