Fターム[5F064DD01]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076)

Fターム[5F064DD01]の下位に属するFターム

自動配置、レイアウト (711)

最適化 (397)

階層構造 (175)

単位セル、ブロック内での配置、レイアウト (423)

素子、セル、ブロックの大きさ (500)

素子、セル、ブロックの形状 (355)

素子、セル、ブロックの方向、角度 (184)

素子、セル、ブロックの個数、密度 (216)

素子、セル、ブロックの位置、座標 (576)

素子、セル、ブロックの配列、ピッチ (599)

素子間、セル間、ブロック間距離 (382)

素子、セル、ブロックの入出力端子 (350)

不使用素子、セル、ブロックの取扱い (180)

Fターム[5F064DD01]に分類される特許

1 - 20 / 28

半導体集積回路

集積回路設計装置及び集積回路の設計プログラム

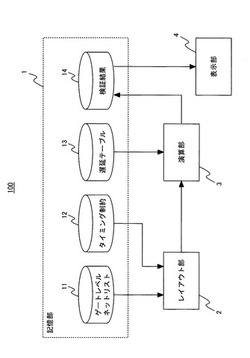

【課題】設計作業に要する時間を短くすることができる集積回路設計装置及び集積回路の設計プログラムを提供すること。

【解決手段】本発明は、記憶部1、レイアウト部2、演算部3及び表示部4を有する。記憶部1は、ゲートレベルネットリスト11、タイミング制約12及び遅延テーブル13が予め記憶される。遅延テーブル13は、回路に配置されるセルのファンアウト数及びセルに接続される配線の長さに対応する最小の遅延が格納される。レイアウト部2は、ゲートレベルネットリスト11及びタイミング制約12に基づきセルレイアウトを生成し、それぞれのセルのファンアウト数とセルに接続される配線の長さとを算出する。演算部3は、算出したファンアウト数及び配線の長さに対応する遅延を遅延テーブル13から読み出し、セルレイアウトがセットアップタイムを満たすか否かの検証を行う。表示部4は、検証結果14を視認可能な状態で表示する。

(もっと読む)

半導体装置の製造方法及び設計装置

【課題】大きさの異なる複数のダイを効率よく製造可能な半導体装置の製造方法を提供する。

【解決手段】大きさの異なる複数のダイパターンが、繰り返し配置されたウェハマップを作成し(ステップS12)、そのウェハマップをもとに、同一ウェハから大きさの異なる複数のダイを個片化するようにダイシングラインを設定したダイシングマップを作成する(ステップS13)。これにより、ダイシング工程(ステップS5)において、同一のウェハから大きさの異なる複数のダイが個片化される。

(もっと読む)

回路解析方法、半導体集積回路の製造方法、回路解析プログラム、及び回路解析装置

【課題】TATを短縮しつつ、解析精度の高いタイミング解析を行う。

【解決手段】本発明による回路解析装置10は、レイアウト変更後の設計対象回路に対してタイミング解析を行う。回路解析装置10は、抽出範囲基準41が設定される記憶装置13と、抽出範囲設定部1と、タイミング解析部とを具備する。抽出範囲設定部1は、レイアウトの変更箇所を含む抽出範囲基準41を寄生素子の抽出対象範囲100として設定する。タイミング解析部2、4、6は、抽出対象範囲100から抽出された寄生素子を含む所定の範囲100、200、300を解析対象として、タイミング解析を行う。

(もっと読む)

半導体集積回路

【課題】回路の集積度の向上を図ることが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路のプログラム素子のゲート電極は、第1のMOSトランジスタの他端に一端が接続され、接地電位に他端が接続されるとともに、ゲート絶縁膜上に形成されたポリシリコン膜と、ポリシリコン膜上に形成されたシリサイド膜と、を含む。プログラム素子にデータを書き込むための書き込み動作モードにおいては、電圧供給端子の電位を正の書き込み電位に設定するとともに、第1の入力信号により第1のMOSトランジスタを所定期間オンすることにより、シリサイド膜をエレクトロマイグレーションさせ、プログラム素子に記憶されたデータを読み出すための読み出し動作モードにおいては、電圧供給端子の電位を書き込み電位よりも低い正の読み出し電位に設定するとともに、第2の入力信号により第2のMOSトランジスタを所定期間オンした後、第1の入力信号により第1のMOSトランジスタを所定期間オンする。

(もっと読む)

配線モジュール及び半導体集積回路装置

【課題】ハードマクロと周辺部に配置された周辺バッファ回路との間で相対的な配置が変更された場合に、再度タイミング検証をやり直す必要のない配線モジュールを提供すること。

【解決手段】線対称の配線モジュール10であって、第1の端子11a、第2の端子11b及び第3の端子11cと、第1の端子11a及び第2の端子11bを接続する第1の配線12aと、第1の配線12aの中点及び第3の端子11cを接続する第2の配線12bと、を備え、第1の端子11a及び第2の端子11bを対称軸について互いに対称に設ける。

(もっと読む)

リピータ回路、リピータ回路設計装置、リピータ回路設計プログラムおよびリピータ回路設計方法

【課題】複数の電源電圧条件下であっても適切な遅延をおこなうリピータ回路を提供する。

【解決手段】リピータ回路100は、複数の電源電圧条件下で利用される設計対象回路に搭載され、電源電圧条件ごとに前記設計対象回路を流れる信号の伝送タイミングを遅延させるリピータが挿入された複数の伝送路110、120と、設計対象回路を動作させる電源電圧条件に応じて、前記複数の伝送路の中からいずれか一つの伝送路を選択して当該伝送路に前記信号を伝送させる伝送制御部130とを備える。

(もっと読む)

磁性装置を備えた集積回路チップ

【課題】配線密度を増加させるという要求を満たすことができる集積回路チップを提供する。

【解決手段】ロジックゲートアレイを提供する。ロジックゲートは、シリコン基板102と、シリコン基板102上に配置されている第1のロジックゲート層202と、第1のロジックゲート層202上に配置されている第2のロジックゲート層206と、第1のロジックゲート層202と第2のロジックゲート層206との間に配置されるとともに、第1および第2のロジックゲート層の磁性ゲートを接続する接続線層204とを備え、第1のロジックゲート層202、第2のロジックゲート層206、および接続線層204がいずれもビアホール210で電気的に接続されている。

(もっと読む)

クロック供給回路及びその設計方法

【課題】配線混雑を抑制しつつ、各配線層の配線の出来具合に起因するクロックスキューを抑制できるクロック供給回路を提供する。

【解決手段】本発明に係るクロック供給回路は、クロックツリー構造を有し、クロック信号を複数の動作素子216〜223に供給するクロック供給回路200であって、前記クロックツリー構造を構成する複数の駆動素子201〜215と、前段の駆動素子の出力と次段の複数の駆動素子又は動作素子とをそれぞれ接続する複数の接続配線224〜238とを備え、複数の接続配線224〜238は、基準配線層で形成される複数の第1配線224〜237と、前記基準配線層を使用する回路ブロック239上に存在する第2配線238とを含み、第2配線238の回路ブロック239上の配線は、前記基準配線層より上層の所定の配線層で形成される。

(もっと読む)

半導体集積回路及びその製造方法

【課題】高速回路部分の性能は下げないか同等でありながら高精度マスクを用いると共にこれより精度の低い低精度マスクを用いて配線もしくは拡散層を形成した半導体集積回路及びその製造方法を提供する。

【解決手段】配線若しくは拡散層を形成する少なくとも1つの高精度マスク及び少なくとも1つの当該高精度マスクよりも低精度の低精度マスクを準備し、前記半導体集積回路の所定の回路部分(メモリ等ハード化メガセル)を前記高精度マスクを用いて露光する(それ以外の回路部分は遮光マスク8で覆う)ことにより前記所定の回路を形成する工程と、前記半導体集積回路の前記所定の回路部分以外の他の回路部分(ランダムロジック、入出力バッファ)を前記低精度マスクを用いて露光する(所定の回路部分は遮光マスク9で覆う)ことにより前記他の回路を形成する工程とを具備する。

(もっと読む)

三次元集積電気回路の配線構造及びそのレイアウト方法

【課題】複数のモジュール間を3次元的に接続する3次元集積電気回路の配線構造において、ネットワークの高い性能及びハードウェアの量と機能を維持しつつ、配線長を低減し、モジュール間の通信遅延を低減する。

【解決手段】本発明による三次元集積電気回路の配線構造は、複数の電気回路モジュールと、前記電気回路モジュールを相互に交換接続する交換接続手段と、前記電気回路モジュールと前記交換接続手段とを接続する配線及び前記交換接続手段間を接続する配線とで構成される二次元集積電気回路モジュールを三次元的に積層して構成される三次元集積電気回路の配線構造であって、前記二次元集積電気回路モジュール間の配線は前記二次元集積電気回路モジュールのほぼ中央を貫通する貫通ビアを通して構成され、前記電気回路モジュール及び前記交換接続手段とを接続する配線構成をFat Treeトポロジ又はFat H−Treeトポロジを用いて構成される。

(もっと読む)

半導体装置の製造方法

【課題】微細かつ高精度なパターンを含む半導体装置を高い生産効率で製造することができる半導体装置の製造方法を提供する。

【解決手段】露光装置Aを用いて所定の寸法精度内に転写可能なマスクAを準備し(s1)、マスクAでの転写パターンにおいて、所定の寸法精度内に転写すべき複数のクリティカルパターン部を選定し、各クリティカルパターン部の近傍領域に関する開口率をそれぞれ算出する(s2)。複数のクリティカルパターン部のうち、開口率が最大となるクリティカルパターン部αおよび開口率が最小となるクリティカルパターン部βをそれぞれ特定する(s3,s4)。露光装置Bを用いてマスクAを転写した場合、クリティカルパターン部α,βの各寸法が所定の許容範囲に収まるかを評価し(s5)、各寸法が所定の許容範囲に収まる場合、露光装置BとマスクAの組合せにより露光を実施する(s6)。

(もっと読む)

レイアウト設計方法およびレイアウト設計装置

【課題】複数の電源受給領域間での信号の行き来の発生を検出し、実デバイスにおいて、予測不能なタイミング違反が発生することを防止できるレイアウト設計方法およびレイアウト設計装置を提供する。

【解決手段】複数の電源受給領域のそれぞれに、対応する電源の供給を受けて動作する回路セルを配置し、回路セル間の接続の情報を含む第1のレイアウトデータを作成し、回路が動作タイミングの仕様を満たすように回路セル間に追加セルを配置し、回路セルおよび追加セル間の接続の情報、並びに、回路セルおよび追加セルのそれぞれが複数の電源受給領域のいずれに位置するかを示す電源受給領域情報を含む第2のレイアウトデータを作成し、第1のレイアウトデータと第2のレイアウトデータとを比較して追加セルを把握するとともに、追加セルの後段および前段に接続される回路セルであるレシーバセルとドライバセルとの間で異なる電源受給領域間の行き来が発生している箇所を抽出する。

(もっと読む)

半導体集積回路装置、データ記録装置及び半導体集積回路装置のレイアウト方法

【課題】少なくとも2つの画像データインターフェースを有し、画像データの信頼性の観点から画像データインターフェース及びメモリインターフェースについての有効な配置を行った半導体集積回路装置を提供すること。

【解決手段】第1の画像データインターフェース部110は半導体チップ200の第1の辺230に沿って設けられている電極領域210及び入出力バッファ領域220に配置される。第2の画像データインターフェース部130は第2の辺240に沿って設けられている電極領域210及び入出力バッファ領域220に配置される。第1のメモリインターフェース部160は第3の辺250に沿って設けられている電極領域210及び入出力バッファ領域220に配置される。第2のメモリインターフェース部170は第4の辺260に沿って設けられている電極領域210及び入出力バッファ領域220に配置される。

(もっと読む)

半導体集積回路の電源制御回路、および制御方法

【課題】消費電力削減のためのプログラム作成を不要とし、汎用LSIの消費電力を低減させる。

【解決手段】LSIのCPUから制御対象モジュールへのアクセスを検出するアクセス検出手段2と、そのアクセスが検出されたとき、制御対象モジュールに電源を接続する電源接続手段3とを備える。

(もっと読む)

半導体集積回路

【課題】 信号出力の同時スイッチングによる電源ノイズの発生、及び、それに起因する回路の誤動作を簡易に防止可能な半導体集積回路を提供する。

【解決手段】 半導体集積回路のチップ周辺部に複数配置する入出力バッファセル2,3の夫々が、出力バッファ回路4に供給すべき第1電源電圧Vccと第2電源電圧Vssの少なくとも何れか一方の電源電圧をチップ外部から受け取るための電源パッド6,7を備える。好ましくは、1つの信号パッド5と第1電源電圧Vccをチップ外部から受け取るための1つの第1電源パッド6を有する第1入出力バッファセル2と、1つの信号パッド5と第2電源電圧Vssをチップ外部から受け取るための1つの第2電源パッド7を有する第2入出力バッファセル3の少なくとも2種類の入出力バッファセルを備える。

(もっと読む)

プログラマブル論理デバイス、回路情報入力制御装置および半導体装置

【課題】データ転送用に特別な回路を専用に用意することなく、データの通信部分が処理性能全体のボトルネックとならないようにすることができるとともに、メモリに記録するのと同程度の回路間の設計の独立性を確保することができるプログラマブル論理デバイスを提供する。

【解決手段】処理回路部において論理回路Aと論理回路Bとを続けて実行する際に(S1〜S5)、処理回路部が論理回路Aの実行終了後に(S6のYes)、回路情報入力制御部の制御によって論理回路Aと論理回路Bのどちらでも利用するデータの転送を行うためのデータ転送用論理回路である論理回路Tに切り替え(S7)、処理回路部が論理回路Tによるデータ転送の実行を終了した後(S8のYes)、回路情報入力制御部の制御によって論理回路Bに切り替える(S9〜S10)。

(もっと読む)

基板結合等価回路の生成方法

【課題】半導体基板に寄生する基板インピーダンスを介して電気的に結合する基板結合対策として、ガードリング等による、基板結合に対する低減効果を、設計段階で精度よく予測するシミュレーション手法による大規模半導体集積回路における基板結合の等価回路の生成方法を提供する。

【解決手段】基板結合等価回路の生成方法は、半導体集積回路の形成された半導体チップを水平方向にスライスした2個以上の水平部分チップに分割し、それぞれの水平部分チップを抵抗メッシュ近似して基板結合等価回路を導出して、これらの基板結合等価回路を回路ネットリスト上で接続することにより半導体チップ全体の基板結合等価回路を得る。この等価回路を用いて半導体チップ断面方向に強く局所性を持った不純物濃度分布があっても精度劣化しない基板結合による雑音を解析することを可能とする。

(もっと読む)

半導体集積回路の設計方法および半導体集積回路

【課題】

アンテナ基準を満足するMOSFETとダミーのMOS容量素子を形成することにより、アンテナ効果による素子破壊を防止する半導体集積回路の設計方法および半導体集積回路に関する。

【解決手段】

半導体基板4上に形成されたゲート配線層2と、トランジスタ形成領域上の前記ゲート配線層2下部に形成されたゲート酸化膜5と、半導体基板4上の前記ゲート配線層2下部に形成されたダミーゲート酸化膜13とを有し、前記ゲート酸化膜5と前記ダミーゲート酸化膜13を合わせた電荷許容量が、予め設定された値以上であることを特徴とする半導体集積回路である。

(もっと読む)

半導体装置

【課題】 パッドの下方に半導体素子を設けることができ、信頼性の高い半導体装置を提供する。

【解決手段】 本発明の半導体装置は、

素子形成領域10Aと該素子形成領域10Aの周囲に設けられた素子分離領域20とを有する半導体層10と、

前記素子形成領域10A内に形成された素子30と、

前記半導体層10の上方に設けられた層間絶縁層60と、

前記層間絶縁層60の上方に設けられ、平面形状が短辺と長辺とを有する長方形である電極パッド62であって、前記素子30と平面視で少なくとも一部が重複する前記電極パッド62と、を含み、

前記半導体層10において、前記電極パッド62の前記短辺の鉛直下方から外側に位置する所定の範囲は、素子禁止領域12である。

(もっと読む)

1 - 20 / 28

[ Back to top ]