Fターム[5F064DD04]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 階層構造 (175)

Fターム[5F064DD04]に分類される特許

1 - 20 / 175

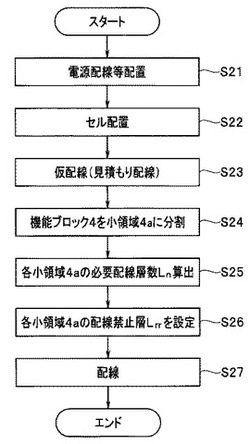

半導体集積回路の設計装置、及び半導体集積回路の設計方法

【課題】チップサイズを縮小することができる、半導体集積回路の設計装置、及び半導体集積回路の設計方法を提供する

【解決手段】下位階層の機能ブロック4に配置された複数のセル間を接続する第一の配線を設計する下位階層配線設計部311と、上位階層の機能ブロック間を接続する第二の配線を設計する上位階層配線設計部312とを備えており、下位階層配線設計部311は、機能ブロック4を複数の小領域4aに分割し、小領域4aごとに機能ブロック4内配線に必要となる必要配線層数Lnを算出して、最下部の配線層から必要配線層数Ln枚の配線層を配線可能領域として同領域内に第一の配線を配置し、上位階層配線設計部312は、第一の配線における配線可能領域以外の機能ブロック4の配線層に第二の配線を配置する。

(もっと読む)

半導体集積回路のレイアウト方法、レイアウト装置およびプログラム

【課題】複数の階層ブロックが互いに重なり合うことを許容しつつレイアウト設計を行う際に、設計期間の長期化を防ぐこと。

【解決手段】複数の内部要素をそれぞれ含む複数の階層ブロックを、内部要素を割り当て可能な内部要素リソースが配置された実装領域に対してレイアウトする場合に、第1の階層ブロックと第2の階層ブロックとが重複領域において重なり合うとき、第1の階層ブロックの内部要素のうちの重複領域に含まれる第1の内部要素の個数と、第2の階層ブロックの内部要素のうちの重複領域に含まれる第2の内部要素の個数との合計が、重複領域に含まれる内部要素リソースの個数以下となるように、第1の階層ブロックおよび第2の階層ブロックを配置し、第1の内部要素の個数と第2の内部要素の個数との比に応じて、重複領域に含まれる内部要素リソースを、第1の階層ブロックと第2の階層ブロックに割り当てる。

(もっと読む)

フロアプラン作成情報生成方法、フロアプラン作成情報生成プログラム、フロアプラン作成情報生成装置、フロアプラン最適化方法、フロアプラン最適化プログラム及びフロアプラン最適化装置。

【課題】フロアプラン設計におけるイタレーションを防ぎ、設計期間を短縮する。

【解決手段】複数の回路モジュールの接続情報を含むネットリストと、前記複数の回路モジュールにグループを設定するためのグループ設定情報と、を記憶部に記憶し、ネットリスト及びグループ設定情報に基づき、複数の回路モジュールにグループを設定し(S21)、設定されたグループ間におけるタイミング制約を満たす距離を算出し(S23)、算出されたグループ間の距離を含み、フロアプランを作成するためのフロアプラン作成情報を生成する(S25)。

(もっと読む)

LSIのレイアウトパターン表示装置および表示方法

【課題】レイアウトパターン上で、直観的に回路素子を認識可能とし、回路素子間の信号の流れの把握を容易にする。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。条件設定部800には、セル枠決定に用いる特定のレイヤーを示す情報がセル枠決定条件として設定されており、セル枠決定部600は、個々のセルについて、当該特定のレイヤーに収録されている図形を抽出し、抽出した図形の論理和図形を形成し、この論理和図形の外接矩形をセル枠として求める。端子図形生成部500は、求めたセル枠とセル間配線との交差位置に端子図形を生成する。レイアウトパターン表示部400は、セル枠と端子図形をレイアウトパターン上に重畳表示する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

レイアウト検証装置及びレイアウト検証方法

【課題】汎用性が高く、効率的に検証処理を行うことができるレイアウト検証技術を提供する。

【解決手段】レイアウトデータがデザインルールに反するか否かの検証を行うに際し、所定の設計値に基づき、レイアウトデータ(1)を、擬似エラー領域内のものとそれ以外のものとに区分し、通常のデザインルール(4)からの許容範囲内のものとして擬似エラー領域用のデザインルール(13)を作成し、擬似エラー領域外のレイアウトデータについては通常のデザインルールで検証を行い、擬似エラー領域内のレイアウトデータについては擬似エラー領域用のデザインルールで検証を行う。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】LSIのレイアウト設計において、TAT(Turn Around Time)を増加させることなくタイミング収束を実現する。

【解決手段】LSIのレイアウト設計方法は、レイアウト対象の集積回路のネットリストに基づいて、前記集積回路をクロックドメインに分けることでクロックドメイン回路集合体に区分する工程と、前記クロックドメイン回路集合体の各々に対するタイミング制約を作成する工程と、所定の基準に基づいて前記クロックドメイン回路集合体間の配置順序を決定する工程と、前記クロックドメイン回路集合体を前記配置順序に従って配置し配線することにより前記集積回路のレイアウトを作成する工程とを備える。レイアウト設計後のタイミング収束のTATを短縮することが可能となる。

(もっと読む)

階層レイアウト設計装置、階層レイアウト設計方法およびプログラム

【課題】複数の下位階層ブロックに跨るセル同士を各下位階層ブロックに設けた端子を経由して相互に接続する場合に、セル間を結ぶ経路が迂回経路となること。

【解決手段】階層レイアウト設計装置は、第1の下位階層ブロックに含まれるセルから出力された信号を受信する出力端子を該セルの近傍に配置する出力端子配置部と、第2の下位階層ブロックに含まれる複数のセルへ前記出力端子から出力された信号を供給する入力端子を、該複数のセルを囲む最小の矩形領域の境界上であって、前記出力端子が配置された箇所からの距離が最短の箇所に配置する入力端子配置部と、を備えている。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

設計支援装置、設計支援方法および設計支援プログラム

【課題】処理の高速化を図ること。

【解決手段】記憶部1a1は、複数の階層を有する半導体集積回路モデル2の階層Cに属するモジュール2dが備える配線のうち、階層Cより上位の階層A、Bに属するモジュール2a、2bが備える配線に対し加害者ネットまたは被害者ネットとなる可能性のある配線L1に関する配線情報D1を記憶する。配線特定部1bは、階層Bに属するモジュール2b内で閉じた配線であり、かつ、記憶部1a1に記憶されている配線情報D1の配線L1に対する被害者ネットまたは加害者ネットとなる配線を特定する。

(もっと読む)

設計支援装置、制御方法および制御プログラム

【課題】配線の効率化を図ること。

【解決手段】設計支援装置1は、表示部2に接続されており、記憶部1aと、選択部1bと、配置部1cと、判断部1dと、配線部1eと、確定部1fとを有している。記憶部1aは、回路の論理接続情報と配置対象のセルのセル情報を記憶する。選択部1bは、記憶部1aに記憶されたセル情報のうち、配置対象のセルのセル情報を選択する。配置部1cは、入力された座標に基づき、選択されたセル情報のセルの仮の配置を行う。判断部1dは、配線モードであるか否かを判断する。配線部1eは、判断部1dが配線モードであると判断した場合、仮の配置がされたセルに接続する配線について仮の配線を行う。確定部1fは、セルの配置位置の確定に基づいて、配線されたセルの仮の配線の配置位置を確定する。

(もっと読む)

半導体集積回路

【課題】セル内のメタル配線幅を、設計上許容すべき最大駆動容量Cmax未満の配線幅に設定して、セル内の容量を削減し、セル相互間距離が非常に近い回路などにおいて伝播遅延を所定時間以下に設計することができるようにする。

【解決手段】配線幅以外は全て同一のレイアウトパターンを備えた2種類のスタンダードセル101、151が用意される。一方のスタンダードセル101は、セル内部のメタル配線108、110の配線幅Ws1、Wd1は太く、他方のスタンダードセル151では、セル内部のメタル配線158、160の配線幅Ws2、Wd2は、前記一方のスタンダードセル101の配線幅Ws1、Wd1よりも細く設定される(Ws2<Ws1、Wd2<Wd1)。配線幅の細いセルライブラリ151は、駆動負荷の小さい回路に限定して適用される。

(もっと読む)

半導体集積回路階層設計方法

【課題】対象階層マクロブロックから他の階層マクロブロックへの配線間容量を更に抑制すること。

【解決手段】本発明では、チップ全体を階層的に分割した複数の階層マクロブロックを生成する(S2)。階層マクロブロック30に対する回路図データから、初段、最終段のセルを表す境界セル群40〜43、44〜47と、上位の階層マクロブロック60のセル71、72及び境界セル群40〜43、44〜47を接続する境界パス群53、54とを抽出する(S3)。階層マクロブロック30において、境界31の一部分32から内部に延びる境界回路領域61と、境界回路領域61を囲う境界セル領域62と、それ以外の領域63とを決定し(S4)、境界セル群40〜43、44〜47を境界セル領域62に配置する(S5)。階層マクロブロック60にセル71、72を配置すると同時に、境界回路領域61に境界パス群53、54を配置する(S9)。

(もっと読む)

基板の配線設計方法及びプログラム

【課題】配線設計において、簡易的に配線混雑を回避することが可能な配線設計方法を提供することを目的とする。

【解決手段】複数の第1方向配線の配線層及び複数の第2方向配線の配線層を備える基板対して概略配線を行い、基板を複数のタイルに分割し、複数のタイルに対応するように、複数の第1方向配線の配線層及び複数の第2方向配線の配線層を分割して、複数の第1方向配線の部分配線領域と、複数の第2方向配線の部分配線領域と、を形成し、タイルにおける第1方向配線がオーバーフローしている場合には、このタイルに対応する第2方向配線の部分配線領域を、第1方向配線の部分配線領域に変更する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】

複数階層を有する半導体集積回路の階層レイアウトを行なう際に、複数個所で使用される下位モジュールについての各配置箇所における下位モジュール近傍の上位階層の配線状況を考慮して、下位モジュールのレイアウト設計を行なうことを課題とする。

【解決手段】

上記課題を解決するために、本発明に係るレイアウト設計装置は、複数階層を有する半導体集積回路のレイアウト設計装置であって、複数個所で使用される下位モジュールについて、前記下位モジュールが配置される上位モジュール内のそれぞれの配置箇所近傍の上位階層の配線情報を抽出し、抽出した上位階層の配線情報を、前記下位モジュールのレイアウト設計を行なう際の配線禁止領域として設定し、前記下位モジュールのレイアウトを行なう。

(もっと読む)

フロアプランデータ生成装置及び方法

【課題】チップの設計期間を短縮する。

【解決手段】CPU1は、設計対象の回路を構成するセルのうち、所定のサイズより大きいセルサイズを有するセルのみの回路情報をゲートレベルで記述した簡易ネットリスト43と、所定のサイズより大きいセルサイズを有するセルのみの仕様データを含むセルリスト44とを用いてフロアプランを行い、仮フロアプランデータ47を生成する。CPU1は、ユーザによって回路全体のフロアプランが行われるときに、回路を構成するセルの仕様データである全体ライブラリ42と、回路を構成するセルの回路情報をゲートレベルで記述した全体ネットリスト45と、仮フロアプランデータ47と、簡易ネットリスト43を全体ネットリスト45に整合させるためのセルリスト44とを出力する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法及びプログラム

【課題】ハードマクロのレイアウト設計時に空き領域を削減して、ハードマクロのサイズを小さくすること。

【解決手段】半導体集積回路のハードマクロのレイアウト設計方法において、コンピュータが、中継用セルを配置する領域を規定するとともに該中継用セルが有する入出力端子に相当する箇所を配線禁止領域として含むレイアウトセルをハードマクロ上に配置する工程と、前記ハードマクロを構成する機能ブロックを配置する工程と、前記配線禁止領域を回避しつつ前記機能ブロックに対する配線を配置する工程と、を含む。

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】クロックツリー設計において、簡潔なスキュー調整をすることができるレイアウト装置及びレイアウト方法を提供すること。

【解決手段】本発明にかかるレイアウト装置1は、想定スキュー値記憶部141、遅延挿入部133、遅延調整部134を備える。想定スキュー値記憶部141は、クロックツリーの段数に応じて予め定められた想定スキュー値を格納する。遅延挿入部133は、想定スキュー値が要求スキュー値以下である場合、当該クロックツリーの最上位側に遅延調整バッファ206を挿入する。遅延調整部134は、クロックツリーのスキュー値が要求スキュー値以下となるように、クロックツリーの配線後に、遅延調整バッファ206の遅延を調整する。

(もっと読む)

1 - 20 / 175

[ Back to top ]