Fターム[5F064DD07]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの大きさ (500)

Fターム[5F064DD07]の下位に属するFターム

Fターム[5F064DD07]に分類される特許

1 - 20 / 245

スタンダードセル、および、半導体集積回路

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラム

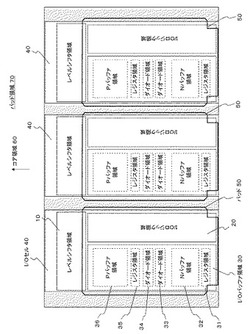

【課題】レイアウト設計において、複数のI/Oバッファセルを2列以上に配列する場合、I/Oバッファ領域の近傍にリピータを挿入する領域を確保し、手戻りをできるだけ抑えることができる、半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラムを提供する。

【解決手段】リピータを含まないフィルセル(FC)と、リピータを含むフィルセル(FCR)とが用いられる。フィルセル(FC)は、同列で互いに隣接したI/Oバッファセル(Bm=1、n、Bm=1、n+1など)間に配置される。なお、複数のI/Oバッファセルは、2列に配置されている。I/Oバッファセルからプリミティブセルまでの配線長に基づいて、すでに配置されているフィルセル(FC)が、リピータを含むフィルセル(FCR)に置換される。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

半導体集積回路装置

【課題】チップ面積を増加させることなく、効率良くリーク電流を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は論理が同一のセルA−1,B−1,C−1を備えている。セルB−1はセルA−1よりセル幅W2が大きいが、MOSトランジスタのゲート長L1はセルA−1と等しい。セルC−1は、セルB−1とセル幅W2が等しいが、ゲート長L2が大きいMOSトランジスタを有しており、セルA−1,B−1と比べて回路遅延は遅くなるがリーク電流は小さくなる。このため例えば、空き領域に隣接したセルA−1をセルB−1に置き換え、タイミングに余裕があるパスにおけるセルB−1をセルC−1に置き換えることによって、チップ面積を増加させることなく、リーク電流を抑えることができる。

(もっと読む)

半導体集積装置

【課題】共通放電経路との間の異種電源間ESD保護回路をそれぞれの電源のパッドの近くに配置することのできる半導体集積装置を提供する。

【解決手段】実施形態の半導体集積装置1は、パッドPと、自己電源用ESD保護回路ESD1とを有し、VDDc系統の電源供給に使用の電源用I/OセルIOC1と、パッドPと、自己電源用ESD保護回路ESD1と、異種電源間ESD保護回路ESD2とを有し、VDDa、VDDb系統の電源供給に使用の電源用I/OセルIOC2とを備える。信号入出力用I/OセルIOC100と同一外形寸法の電源用I/OセルIOC1およびIOC2が、列状に配置されたIOC100と同列に配置され、電源用I/OセルIOC2の異種電源間ESD保護回路ESD2へ接続される共通放電経路CDLが、電源用I/OセルIOC1から、列状に配置されたIOC100を貫通して、電源用I/OセルIOC2へ配線される。

(もっと読む)

ネットリスト変換装置、論理合成装置及びコンピュータプログラム

【課題】半導体集積回路の開発期間を短縮し、且つ、レイアウトエラー確率を低減する。

【解決手段】本発明の実施形態のネットリスト変換装置は、半導体集積回路を構成する複数のセルであって、第1遅延時間だけスキャン用データ信号を遅延させる第1スキャンフリップフロップを含む複数のセルの接続関係を示すネットリストを変換する。そのようなネットリスト変換装置は、論理ライブラリ30と、ネットリスト変換部18と、を備える。論理ライブラリ30は、半導体集積回路を構成する複数のセルの論理的機能を示す情報を含むセル論理情報であって、第1スキャンフリップフロップの論理的機能を示す情報と、第1遅延時間より大きいスキャン用第2遅延時間だけデータ信号を遅延させる第2スキャンフリップフロップの論理的機能を示す情報と、を含むセル論理情報を記憶する。ネットリスト変換部18は、セル論理情報を参照して、ネットリストの第1スキャンフリップフロップを第2スキャンフリップフロップに置換する。

(もっと読む)

ホールドエラー修正方法、ホールドエラー修正装置及びホールドエラー修正プログラム

【課題】ホールドエラーをより確実に修正することが可能なホールドエラー修正方法、ホールドエラー修正装置及びホールドエラー修正プログラムを提供する。

【解決手段】ホールドエラー修正方法は、レイアウトデータ53に対しタイミング解析を行ってタイミングレポート54を生成し、ホールドエラーセルとは別のセルを置換元セルに選択し、置換元セルよりも駆動能力が小さいセルを置換先セルに選択し、レイアウトデータ53において置換元セルを置換先セルに置換し、置換により生成された空き領域に、ホールドエラーセルのホールドエラーを修正するためのホールドバッファを挿入して、挿入したレイアウトデータを生成するものである。

(もっと読む)

半導体集積回路装置のレイアウト設計方法

【課題】チップサイズの増大を抑制できる半導体集積回路装置のレイアウト設計方法を提供する。

【解決手段】外部電源電圧が供給される第一電源線と第一電源線にスイッチとなる第二電源ドライバを介して接続される第二電源線とを備えた、SCRC方式を採用した半導体集積回路装置において、第二電源ドライバのレイアウト面積の増大を抑制するために、半導体集積回路装置の全回路を機能別回路に分割し、機能別回路領域毎に、SCRC方式による制御対象の回路であるSCRC使用動作回路のトランジスサイズに応じて第二電源ドライバとして用いるMOSトランジスタのサイズを決定する。

(もっと読む)

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

回路設計検証装置および回路設計検証方法

【課題】回路シミュレーション用のネットリストに基づいて、当該回路のファンアウトを計算できるようにすること。

【解決手段】回路設計検証装置は、半導体素子レベルの回路シミュレーション用のネットリストを、論理を構成する複数の駆動回路に分割するネットリスト分割部と、前記複数の駆動回路のそれぞれに含まれるMOSトランジスタのゲート長およびゲート幅からゲートサイズを算出するゲートサイズ算出部と、前記複数の駆動回路のそれぞれによって駆動される後段の素子の負荷容量を算出する負荷容量算出部と、算出されたゲートサイズおよび算出された負荷容量に基づいて、前記複数の駆動回路のそれぞれに対するファンアウトを算出するファンアウト算出部と、を備えている。

(もっと読む)

半導体集積回路の設計方法及び半導体集積回路の設計支援装置

【課題】論理回路の面積縮小化を実現しつつ、設計TATの短縮を可能とする技術を提供する。

【解決手段】複合論理マクロセルを、基本マクロセルに置き換えて面積の総和を抽出し、その面積の総和と複合論理マクロセルの面積とを比較して面積縮小化に有効となる複合論理マクロセルを選択する。その選択された複合論理マクロセルにフラグを設定する。フラグを設定したマクロセルと同等の論理を論理情報から検索する論理構造検索処理を行い、置換対象となる基本マクロセルにフラグを設定する。置換対象のフラグを設定した基本マクロセルを、フラグ設定した複合論理マクロセルに置き換える等価論理置換処理を行う。

(もっと読む)

タイミング解析方法、タイミング解析装置、およびタイミング解析プログラム

【課題】遅延計算に要する処理時間を短縮して、タイミング解析全体に要する処理時間を短縮可能とする。

【解決手段】タイミング解析方法は、半導体チップ上にレイアウトされた回路に対して電圧降下解析を行い、電圧降下解析結果に基づいて、チップ上の電圧降下を所定の電圧範囲ごとの領域として電圧降下領域ファイルを作成し、遅延のばらつきを表現する第1OCV係数が電圧降下を考慮して所定の電圧ごとに対応付けられたOCV係数ファイルを用いて、電圧降下領域ファイルの所定の電圧範囲に対応する第2OCV係数を領域ごとに算出し、算出した第2OCV係数と領域とを対応付けてOCV領域ファイルを作成し、遅延ライブラリを用いてレイアウトされた回路に対して遅延計算を行い、遅延計算結果とOCV領域ファイルの領域ごとの第2OCV係数を用いてタイミング解析を行う。

(もっと読む)

半導体集積回路のレイアウト方法及びプログラム

【課題】パワードメインを自動作成する。

【解決手段】設計された回路が仕様を満たしているか否かを評価するための機能シミュレーション処理(9)と、上記機能シミュレーション処理の結果に基づいて、活性化タイミングが所定の範囲内で揃う論理ブロック毎にクラスタ分割することでパワードメインを得るクラスタ分割処理(10)とがコンピュータで行われる。これにより、パワードメインは、コンピュータで行われる処理によって得られるため、人手(設計者の手作業)によって求める場合に比べてパワードメインの最適化を図ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

1 - 20 / 245

[ Back to top ]