Fターム[5F064DD24]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子間、セル間、ブロック間距離 (382)

Fターム[5F064DD24]に分類される特許

1 - 20 / 382

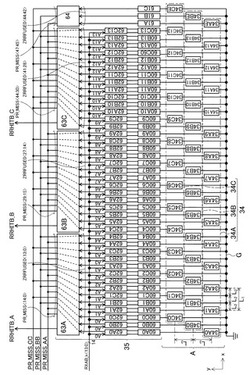

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】クロックツリーにおけるクロックスキューの調整において、精度の確保とデューティ保持とを両立させる。

【解決手段】レイアウト装置(10)において、MOSトランジスタ1段で形成された第1セルと、MOSトランジスタ複数段で形成された第2セルとがライブラリ化されたテーブルを設ける。また、上記レイアウト装置には、上記第1セルと上記第2セルとの組み合わせによるコンビネーションチェーンを上記クロックツリーに挿入することで、上記クロックツリーにおける異なるクロック系統間のクロックスキューを調整可能な演算処理部(12)を設ける。上記コンビネーションチェーンによってクロックスキューの調整を行うことで、個々の第1セルでの遅延誤差が伝播されるのを抑制し、遅延計算における遅延誤差の低減を図る。また、第1セルはMOSトランジスタ1段で形成され、そこで論理反転されるため、デューティ保持の観点で有利とされる。

(もっと読む)

半導体集積回路のレイアウト設計装置、方法、及びプログラム

【課題】アナログ回路において最適な配線効率を実現するためのレイアウト設計を可能にする。

【解決手段】機能ブロックを構成する素子をその種類毎にグループ化する。機能ブロック内の素子の配置を各素子の接続関係に基づいて決定する。この時、グループを構成する素子の分割数を考慮してもよい。機能ブロックの配置順序を面積又は幅が大きい順に配置されるように決定する。また、配置順序はユーザの指定により調整できることが好ましい。配置順序と回路全体の接続情報とに基づいて各機能ブロックの配置位置を決定する。

(もっと読む)

半導体集積回路のレイアウト方法、レイアウト装置およびプログラム

【課題】複数の階層ブロックが互いに重なり合うことを許容しつつレイアウト設計を行う際に、設計期間の長期化を防ぐこと。

【解決手段】複数の内部要素をそれぞれ含む複数の階層ブロックを、内部要素を割り当て可能な内部要素リソースが配置された実装領域に対してレイアウトする場合に、第1の階層ブロックと第2の階層ブロックとが重複領域において重なり合うとき、第1の階層ブロックの内部要素のうちの重複領域に含まれる第1の内部要素の個数と、第2の階層ブロックの内部要素のうちの重複領域に含まれる第2の内部要素の個数との合計が、重複領域に含まれる内部要素リソースの個数以下となるように、第1の階層ブロックおよび第2の階層ブロックを配置し、第1の内部要素の個数と第2の内部要素の個数との比に応じて、重複領域に含まれる内部要素リソースを、第1の階層ブロックと第2の階層ブロックに割り当てる。

(もっと読む)

配置配線装置

【課題】効率的にIR−Dropを防止することが可能な配置配線装置を提供すること。

【解決手段】複数のセルを配置した後、セル間の隙間が所定の大きさよりも小さい場合にはセル間の隙間が所定の大きさ以上となるようにセルの配置を変更する(S17)。そして、配置された複数のセルの間に容量セルを挿入し(S15)、配置された複数のセルの配線を行なう(S14,S16)。したがって、効率的にIR−Dropを防止することが可能となる。

(もっと読む)

フロアプラン作成情報生成方法、フロアプラン作成情報生成プログラム、フロアプラン作成情報生成装置、フロアプラン最適化方法、フロアプラン最適化プログラム及びフロアプラン最適化装置。

【課題】フロアプラン設計におけるイタレーションを防ぎ、設計期間を短縮する。

【解決手段】複数の回路モジュールの接続情報を含むネットリストと、前記複数の回路モジュールにグループを設定するためのグループ設定情報と、を記憶部に記憶し、ネットリスト及びグループ設定情報に基づき、複数の回路モジュールにグループを設定し(S21)、設定されたグループ間におけるタイミング制約を満たす距離を算出し(S23)、算出されたグループ間の距離を含み、フロアプランを作成するためのフロアプラン作成情報を生成する(S25)。

(もっと読む)

回路動作の検証装置及び回路動作の検証方法

【課題】電圧規格や電流規格を満たさない箇所があった場合に、その影響を反映させて検証を行うことができる回路動作の検証装置を提供する。

【解決手段】回路動作の検証装置は、結線情報4と、定格情報6とを用い、回路に入力する信号パターン7が与えられると、その入力パターン7に基づいて回路動作を検証する(S1〜S5)。そして、検証の結果、回路素子に印加される電圧や通電される電流等が定格値を超えることで破壊に至る回路素子が存在すると、当該回路素子を破壊の態様に応じた破壊状態モデルに置換し(S6)、破壊状態モデルに置換した回路について検証を継続する。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】情報が読み取られることを防止する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置10は、コンタクト15aを有する第2絶縁層15と、コンタクト17aを有する第3絶縁層17と、第2絶縁層15と第3絶縁層17との間に配置された第2配線層16と、を備え、コンタクト15aとコンタクト17aとの間の第2配線層16の部分には配線が配置されておらず、コンタクト15aとコンタクト17aとの間の距離は、コンタクト15a又はコンタクト17aと、第2絶縁層15及び第3絶縁層17及び第2配線層16内の他のコンタクト又は配線との間の距離よりも短い。

(もっと読む)

半導体集積回路のレイアウト装置、レイアウト方法及びそれらに用いられるセルデータ

【課題】タイミング違反を容易に解消して工数の増大を抑制すること等が可能な半導体集積回路のレイアウト装置を提供すること。

【解決手段】本発明にかかる半導体集積回路のレイアウト装置は、セルデータを記憶する記憶装置13と、記憶装置13からセルデータを読み出して自動配置配線を行うレイアウト部242と、を備える。また、セルデータは、ターゲットセルに対する配置の状況に応じた遅延をターゲットセルに対して付加する遅延考慮フィラーセルの情報を有する。

(もっと読む)

データ保持装置及びこれを用いた論理演算回路

【課題】マスクパターンの疎密に起因する強誘電体素子の特性ばらつきを適切に低減することが可能なデータ保持装置及び、これを用いた論理演算回路の提供。

【解決手段】データ保持装置において、不揮発性記憶部に含まれる複数の強誘電体素子X(素子幅m)は、各々よりも素子幅の小さいダミー素子Y(素子幅n、ただしn<m)によって包囲されている。これによってマスクパターンの疎密に起因するエッチングのローディング効果を抑制する事が可能となる。

(もっと読む)

半導体集積回路及びそのレイアウト方法

【課題】短時間でレイアウト構成を行うことができる半導体集積回路及びそのレイアウト方法を提供すること。

【解決手段】本発明の一態様である半導体集積回路100は、出力回路11、信号分岐用セル12、マスタ回路13及びチェッカ回路14を有する。出力回路11は、出力信号を出力する。信号分岐用セル12は、出力信号を分岐した第1及び第2の出力信号を出力する。第1及び第2の出力信号に分岐される前の出力信号が伝搬する共通線部である第1の配線16の長さは、制約値X以下である。マスタ回路13は、第1の出力信号を受ける。チェッカ回路14は、第2の出力信号を受け、マスタ回路13と冗長構成回路を構成する。

(もっと読む)

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

クロックツリー設計装置及びクロックツリー設計方法

【課題】クロックレイテンシを最小にする条件下において、クロックスキュー及びバッファ数を比較的少なくする。

【解決手段】実施形態のクロックツリー設計装置は、ターゲットシンクからのマンハッタン距離と最遠シンクからのマンハッタン距離とが等しくなる等距離点の集合を求める等距離点集合算出部と、クロックパスのパス長を最短のマンハッタン距離にするパス設定ブロック領域を設定するパス設定ブロック設定部と、等距離点の集合のうちパス設定ブロック領域内でクロックソースから最も遠い距離の点を分岐点とする分岐点設定部と、クロックソースから分岐点までのパス設定ブロック領域内にターゲットシンクと最遠シンクとの共有パスを設定すると共に、分岐点からターゲットシンクまでのクロックパス及び分岐点から最遠シンクまでのクロックパスをパス長が最短のマンハッタン距離となるように設定するパス設定部とを具備する。

(もっと読む)

レイアウト設計方法、レイアウト設計プログラム及びレイアウト設計装置

【課題】被クリップセルとクリップセル間の配線引き回しを抑え、配線引き回しに起因した不具合を回避する。

【解決手段】レイアウト設計において、ネットリストを用い、被クリップセルと、その被クリップセルに接続されるクリップセルとを抽出し(ステップS1)、抽出された被クリップセルとクリップセルとを関連付けた関連付け情報を生成する(ステップS2)。そして、生成された関連付け情報に基づき、被クリップセルとクリップセルとを隣接させる等して一体で配置し(ステップS3)、配置された被クリップセルとクリップセルとを配線で接続する(ステップS4)。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置および半導体集積回路の設計方法

【課題】本発明は、半導体集積回路を備えた半導体装置および半導体集積回路の設計方法に関し、IO領域を有効に利用しつつパッケージの高さ寸法の増大を有効に抑えた接続を可能とする。

【解決手段】半導体基板の表面の第1の辺に沿って、第1のIOセルと、第2のIOセルとを交互に配置したIO領域を有し、第1のIOセルは、第1の辺から所定の距離の位置に配置されたボンディングパッドを有し、第2のIOセルは、第1のIOセルのボンディングパッドより第1の辺から遠い位置にボンディングパッドを有し、かつ、第1のIOセルの少なくとも1つは、第1の辺から所定の距離の位置に配置された第1のボンディングパッドに加えて、第2のIOセルのボンディングパッドより第1の辺から遠い位置に、第2のボンディングパッドを有する第3のIOセルに置きかえられている。

(もっと読む)

半導体集積回路の設計方法

【課題】設計フローの負荷を増大させることなく、それぞれの回路モジュールに必要十分な容量セルを、それぞれの回路モジュールに近接配置することができる半導体集積回路の設計方法を提供する。

【解決手段】本発明は、それぞれが複数の論理セルを含む複数の回路モジュールからなる半導体集積回路の設計方法であって、複数の回路モジュールのそれぞれの、複数の論理セルおよび複数の論理セルの端子間の接続の情報を記述するネットリストに、複数の論理セルに電源を供給する電源配線間に接続されるセルであり、複数の論理セルのいずれとも独立で、かつ、複数の論理セルの端子と接続される端子を持たない容量セルの記述を追加し、複数の論理セルおよび複数の容量セルのレイアウトデータが格納されたセルライブラリを備えた設計支援システムを利用して、回路モジュールのそれぞれに対応する、複数の論理セルおよび容量セルを配置する配置領域を設定し、複数の論理セルおよび容量セルを対応する配置領域内に配置する工程を含む。

(もっと読む)

1 - 20 / 382

[ Back to top ]