Fターム[5F064EE05]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 単位セル、ブロック内(上)の配線 (232)

Fターム[5F064EE05]の下位に属するFターム

不使用セル、ブロックにおける配線 (78)

Fターム[5F064EE05]に分類される特許

1 - 20 / 154

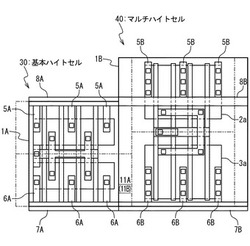

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

半導体レイアウト設定装置、半導体レイアウト設定方法、及び半導体レイアウト設定プログラム

【課題】チップ面積増大を回避し、適切にリピータバッファを挿入する

【解決手段】レイアウト対象の半導体装置は、第1及び第2の電源ドメインを有し、第2の電源ドメインに属する接続元と接続先を接続する配線を有する。配線禁止許可領域設定部120は、第1の電源ドメイン内に排他的配線禁止領域及び通過配線許可領域を、リピータバッファが駆動可能な最大配線長であるリピータ配線最大長に基づいて設定する。配線設定部130は、排他的配線禁止領域及び通過配線許可領域に基づいて、配線を修正する。リピータ挿入部140は、リピータ配線最大長に応じ、配線に挿入するリピータバッファを設定する。排他的配線禁止領域は、第1の電源ドメイン内で接続する配線は許容し、通過配線を禁止する。通過配線許可領域は、第1の電源ドメインから排他的配線禁止領域を除外した領域であり、通過配線が許容される。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体装置

【課題】配線におけるエレクトロマイグレーション耐性を向上させる。

【解決手段】ソース領域42、ソース領域44およびドレイン領域46を有するP型MOSFET40と、ソース領域52、ソース領域54およびドレイン領域56を有し、かつP型MOSFET40と隣接するN型MOSFET50と、ドレイン領域46およびドレイン領域56に接続するドレイン電極と、ドレイン電極と接続し、かつドレイン電極上に設けられた複数のビア10と、を備え、P型MOSFET40とN型MOSFET50は、インバータ回路を構成しており、ドレイン電極は、ビア10を介しては、インバータ回路の出力信号配線30と接続し、他には接続していない。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後のプログラマブルスイッチの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】各論理ブロック間の配線接続を制御するプログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

半導体集積回路

【課題】フリップフロップにおけるアクティブ領域のレイアウトの凹凸を低減する。

【解決手段】半導体チップには、クロック領域CR1、ラッチ領域LR1およびバッファ領域BR1が設けられ、クロック領域CR1にはアクティブ領域AK5、AK6が形成され、ラッチ領域LR1にはアクティブ領域AK1、AK2が形成され、バッファ領域BR1にはアクティブ領域AK3、AK4が形成され、アクティブ領域AK1〜AK6の幅をそれぞれにおいて均一の幅として分割されている。

(もっと読む)

半導体装置の製造方法

【課題】ロジック回路を含む半導体装置に関し、処理時間を短縮し製造コストを低減する。

【解決手段】ロジック回路の形成領域(114)は、所定の精度で光近接補正処理された第1領域(114b,170)と、所定の精度より低い精度で光近接補正処理された第2領域(114a,180)とを備える。特に第1領域(114b,170)は、トランジスタとして動作するゲート配線(172)を有し、第2領域(114a,180)は、トランジスタとして動作しないダミーレイアウト(182)を有する。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

デューティ調整回路の設計装置及び設計方法

【課題】任意のデューティ比であるデューティ調整回路が設計可能なデューティ調整回路の設計装置を提供する。

【解決手段】調整方法決定部は、デューティ調整回路のネットリストと、デューティ調整回路の初期状態のタイミング情報と、ドライバビリティ指定情報と、デューティ比の目標値と、を入力し、立ち上がり時間と立ち下がり時間のどちらの調整によりデューティ比の調整をするか決定する。置換セル数決定部は、調整方法決定部の決定に基づいて置き換える遅延セルの数と種類を遅延調整セルライブラリの中から選択する。遅延調整セル置換部は、置換セル数決定部の決定に基づいて、デューティ調整回路に含まれる複数の遅延調整セルの中から選択した遅延調整セルを初期状態とは異なる遅延調整セルに置き換える。

(もっと読む)

マクロ用レイアウト検証装置及び検証方法

【課題】マクロのレイアウト情報に基づいて、当該マクロが使用されるLSIのレイアウト設計時に発生する可能性がある設計規則違反を予め検出する。

【解決手段】マクロ用レイアウト検証装置は、マクロの端子にビアコンタクトを配置したと仮定する手段と、ビアコンタクトとマクロ内レイアウトとの関係が設計規則に違反するか否かを判定する手段と、を具備する。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子単体の駆動力にはバラツキがあっても、搭載回路の駆動力のウェーハ間のバラツキを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】実施形態の製造方法は、複数の半導体素子が並列に配置された回路を有する半導体装置の製造方法であって、上層配線形成工程用に、複数の半導体素子の並列接続数がそれぞれ異なる複数のマスクを製作しておき(工程S01)、半導体基板上に半導体素子を形成し(工程S02)、上層配線を形成する工程の前に、半導体基板上に形成された半導体素子のオン電流の測定を行い(工程S03)、その測定の結果にもとづいて、上層配線形成工程用の複数のマスクから1枚のマスクを選択し(工程S04)、選択したマスクを用いて上層配線を形成する(工程S05)。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

制御電圧生成回路、定電流源回路及びそれらを有する遅延回路、論理回路

【課題】回路規模を増大させることなくトランジスタの閾値電圧に応じた制御電圧を精度良く生成することが可能な制御電圧生成回路を提供すること。

【解決手段】本発明にかかる制御電圧生成回路は、高電位側電源と低電位側電源との間に直列に接続された同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのドレイン電圧を参照電圧Vp1として生成する参照電圧生成部11と、高電位側電源と低電位側電源との間に直列に接続され参照電圧生成部11と同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのゲートに参照電圧が供給され、何れかのMOSトランジスタのドレイン電圧を制御電圧(バイアス電圧)として出力する電圧変換部12と、を備える。

(もっと読む)

半導体集積回路

【課題】動作特性を劣化させることなくセル面積の縮小化を図ったマクロセル構造の半導体集積回路を得る。

【解決手段】Pウェル領域1の中央部にNウェル領域2が形成される。Nウェル領域2の平面視上方及び下方にN活性領域4a及び4bが形成される。Pウェル領域1内においてN活性領域4aの平面視上方及び下方にPウェルコンタクト領域5a及び5bが横方向に延びて形成される。Nウェル領域2内において中央にP活性領域3が形成され、P活性領域3の左横に縦方向に延びてNウェルコンタクト領域6が形成される。P活性領域3の中心部を横断するVDD用メタル配線層14の一部であるウェルコンタクト部14cは、Nウェルコンタクト領域6上にも形成され、ウェルコンタクト部14cとNウェルコンタクト領域6とは複数のコンタクトホール21を介して電気的に接続される。

(もっと読む)

半導体装置

【課題】ボンディングパッドの直下の酸化膜を壊すことなくウエハテストを行う。

【解決手段】半導体基板9と、半導体基板9上に形成された5層の配線層と、前記5層の配線層のうち、最上層の第5配線層5に形成され、それぞれ一部が露出した複数のボンディングパッド5eと、半導体基板9上に形成され、かつボンディングパッド5eの下において平面視でボンディングパッド5eと重なる位置に配置され、さらにボンディングパッド5eと電気的に接続されたトランジスタ素子等の能動素子と、を有しており、ボンディングパッド5eの直下には、5層の配線層のうちのいずれの配線層も設けられていない緩衝膜7が形成されている。

(もっと読む)

1 - 20 / 154

[ Back to top ]