Fターム[5F064EE41]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766)

Fターム[5F064EE41]の下位に属するFターム

Fターム[5F064EE41]に分類される特許

1 - 7 / 7

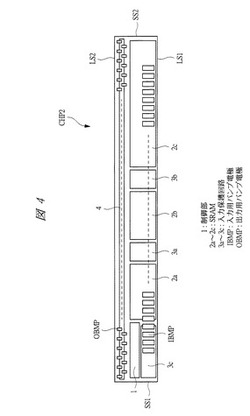

半導体装置

【課題】半導体チップのチップサイズを縮小化することができる技術を提供する。特に、LCDドライバを構成する長方形形状の半導体チップにおいて、短辺方向のレイアウト配置を工夫することにより、半導体チップのチップサイズを縮小化することができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップCHP2は、複数の入力用バンプ電極IBMPのうち一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されている一方、複数の入力用バンプ電極IBMPのうち他の一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されずにSRAM2a〜2c(内部回路)が配置されている。

(もっと読む)

標準セルのレイアウト構造、標準セルライブラリ、及び半導体集積回路のレイアウト構造

【課題】半導体集積回路の製造歩留まりの低下要因の1つであるビアコンタクトの粗密を軽減して、ビアコンタクトの製造不良を改良する。

【解決手段】回路の論理動作上は不必要であるオフトランジスタ126、127を備えた標準セルのレイアウト構造において、前記各オフトランジスタ126、127の不純物拡散領域103、106にダミービアコンタクト116、117が配置される。前記各ダミービアコンタクト116、117には、ダミーメタル配線122、123が接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の接続孔を用いて配線間を接続する半導体装置において、信頼性を向上させる。

【解決手段】第1の絶縁膜8上及び第1の配線10a上に形成された第2の絶縁膜11と、第2の絶縁膜11に形成されており、第1の配線10aの上方を通る溝12aと、溝12aの底部に位置していて第1の配線10a上に配置された第1の接続孔及び第2の接続孔12bと、溝12a、並びに第1の接続孔及び第2の接続孔12bに埋め込まれた第2の配線13aとを具備する、第2の配線13aは、第1の配線10aとは同一長さにおける抵抗値が異なり、第2の接続孔は第1の配線10a又は第2の配線13aの幅方向において第1の接続孔と異なる位置に配置されている。

(もっと読む)

半導体集積回路のレイアウトデータ作成装置及びレイアウトデータ作成方法、半導体装置の製造方法

【課題】半導体集積回路の検証精度を向上し、高信頼性、高歩留まり且つ高集積の半導体装置を実現すること。

【解決手段】半導体集積回路の仕様の情報に基づき論理回路図を設計する論理回路図設計部と、論理回路図に基づきレイアウトデータを作成するレイアウトデータ作成部と、レイアウトデータから配線の抵抗の情報を抽出する抵抗情報抽出部と、回路シミュレーションを実行する回路シミュレーション実行部と、配線の抵抗の情報及び回路シミュレーションの実行結果に基づき配線における電流の向きを識別する電流方向識別部と、配線における電流の向きの情報に基づき配線のレイアウトデータが半導体集積回路の仕様の情報から抽出するデザインルールに違反しているか否かを検証してその検証結果を生成する検証部と、レイアウトデータを出力するデータ出力部と、を有する。

(もっと読む)

半導体装置

【課題】 オープン不良の発生を抑制して高い信頼性を実現することができる半導体装置を提供する。

【解決手段】 ヒューズ配線1において、ヒューズ開口部3の周縁に位置する部分からその端部をヒューズ配線層の直近の上層又は下層の配線層と電気的に接続するビアホール2までの間に腐食原因物質の侵入を遅延させる侵入経路の延長構造を設けた。

(もっと読む)

半導体集積回路装置

【課題】

配線間の絶縁性を確保できるような配置配線を行う。

【解決手段】

同一配線層内において、所定の電圧が供給される第1の配線11と、所定の電圧以上の電圧となる第2の配線12と、所定の電圧以下の電圧となる第3の配線13と、を含む。あるいは、所定の電圧が供給される第1の配線11と、所定の電圧以下の電圧となる第2の配線12と、所定の電圧以上の電圧となる第3の配線13と、を含む。そして、第2の配線12と第3の配線13との間に第1の配線11が介在するようにそれぞれの配線が配線間隔dで配置配線される。予め電位差の少ないことが分かっている配線11が配線12に常に隣接するように配線される。したがって、配線12との電位差が大きくなる可能性のある配線13が配線12に直接的に隣接することがない。このような配線配置の結果、配線間の絶縁性を充分確保できるような配線がなされる。

(もっと読む)

電源配線構造、該電源配線構造を備えた半導体集積回路、電源配線方法ならびに該電源配線方法を用いる半導体集積回路設計方法

【課題】エレクトロマイグレーションの発生を抑制できる電源配線構造を提供すること。

【解決手段】本電源配線構造は、互いに異なる配線層である第1、第2の電源配線1010,1030を備え、かつ、前記両電源配線1010,1030が互いの交差領域でビア1060により電気的に接続されている電源配線構造であって、前記交差領域から第1の電源配線1010の配線方向1020に第2の電源配線1030が延長されて第3の電源配線1070が構成され、かつ、第1および第3の電源配線1010,1070がビア1060により電気的に接続されている。

(もっと読む)

1 - 7 / 7

[ Back to top ]