Fターム[5F064GG00]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798)

Fターム[5F064GG00]の下位に属するFターム

拡散、イオン注入 (156)

エッチング (379)

結晶成長、エピタキシャル成長 (57)

熱処理、アニール (65)

その他 (111)

Fターム[5F064GG00]に分類される特許

1 - 20 / 30

半導体装置およびその製造方法

【課題】銅を主成分とする配線層を有し、かつヒューズの切断によって特性の悪化を招くことのない半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、銅を主成分とするメタル配線34と、メタル配線34よりも上層に形成された最上層配線5と、メタル配線34と最上層配線5との間を接続するためのプラグ9が形成されるプラグ形成層10に少なくとも一部が形成され、銅以外の金属材料を主成分とする導電性材料で形成されたヒューズ膜4とを含む。

(もっと読む)

銅技術相互接続構造を使用する集積回路デバイス用のアルミニウム・パッド電力バスおよび信号ルーティング技術

【課題】電力バス相互接続構造の工程数を低減して製造できる半導体装置の製造方法を提供する。

【解決手段】第1のパッシベーション・スタック149を、導電性ランナ132、134および誘電体層162の上に形成する。開口を、通常のリソグラフィ技術および誘電エッチング技術によって、第1のパッシベーション・スタックを貫通して画定し形成する。露出された表面上に導電性バリア層166を形成する。アルミニウム層をブランケット堆積して、開口を充填する。パターニング、エッチング工程によって、開口内に、アルミニウム・パッド170を形成する。開口内に、ランナ134と導電性接触する導電性バイア172を形成する。アルミニウム・パッドを形成するために用いられるのと同じパターニング、エッチング工程において、アルミニウム層内に電力バス174も形成する。

(もっと読む)

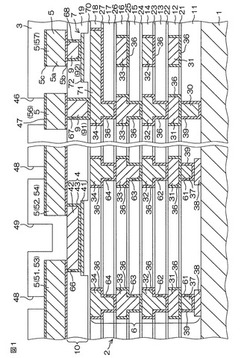

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20と、シリコン基板20の上方に形成された層間絶縁膜38と、層間絶縁膜38の上に互いに間隔をおいて複数形成されたヒューズ41a、41bと、層間絶縁膜38の上であって、隣接するヒューズ41a、41bの間に形成されたダミーパターン41xと、ヒューズ41a、41bのうちの少なくとも一部とダミーパターン41xとを覆うと共に、下から順に塗布型絶縁膜46と窒化シリコン膜47とを備えたパシベーション膜48と有する半導体装置による。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】レーザートリミング加工を行うヒューズ素子を有する半導体集積回路装置の信頼性を向上させる。

【解決手段】隣り合うヒューズ素子に接続する第1層目のアルミニウム配線間のスペース幅を第1層目の金属間絶縁膜の側壁厚さの2倍未満とすることで、吸湿性のSOGの露出を防止する。また、第1層目のアルミニウム配線側面にサイドスペーサーを設けることでより一層の信頼性向上を図る。

(もっと読む)

半導体装置の設計方法および半導体装置の製造方法

【課題】本発明によれば、素子や配線の配置面積を縮小しつつ、ビアの高抵抗不良およびオープン不良が発生しないようにする。

【解決手段】半導体装置100は、下部電極106と上部電極110と、その間に形成された容量膜108とを含む容量112と、下部電極106に電気的に接続する一以上の第1のビア(128)を含む第1のビア群と、上部電極110に電気的に接続するとともに第1のビア群と同時に形成される一以上の第2のビア(130)を含む第2のビア群と、を含む。半導体装置100は、容量112の容量値を第1のビア群および第2のビア群に含まれる第1のビア(128)および第2のビア(130)の総数で除した値が所定値以下となるように第1のビアおよび第2のビアの数を設定する工程を含む方法で設計される。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

性能を改善する新しいレイアウト構造

【課題】性能を改善する新しいレイアウト構造を有する集積回路を提供する。

【解決手段】半導体基板の活性領域102、第1ゲート114、前記活性領域に形成され、前記第1ゲートに隣接した第1領域に設置された第1ソース116、及び前記活性領域に形成され、前記第1ゲートに隣接した第2領域に設置された第1ドレイン118を含む前記活性領域に設置された電界効果トランジスタ108、及び前記第1ドレインに隣接して設置された分離ゲート140、及び前記活性領域に形成され、前記分離ゲートに隣接して設置されて、それと前記第1ドレインが前記分離ゲートの異なる側に位置する分離ソース142を含む前記活性領域に設置された分離構造を含む集積回路。

(もっと読む)

電子回路デザインのさまざまな段階中にコンパクトな製造モデルを実行するための、機械によって実行される方法

【課題】電子回路デザインのさまざまな段階中にコンパクトな製造モデルを実行するための方法、システムおよびコンピュータプログラム製品を開示する。

【解決手段】いくつかの実施例では、上記方法またはシステムは、物理学ベースのデータを受取るまたは特定する。いくつかの実施例では、上記方法またはシステムは、高品質製造プロセスモデルを用いることによって、対応する製造プロセスのための物理学ベースのデータを受取るまたは特定する。いくつかの実施例では、上記方法またはシステムは、物理学ベースのデータを用いて、高品質製造プロセスモデルを微調整、修正または調整する。いくつかの実施例では、上記方法またはシステムは、適切なモジュールを呼出す。いくつかの実施例では、上記方法またはシステムは、コンパクトな製造モデルおよびコレクト・バイ・デザインモジュールを実行し、電子回路デザインのさまざまな段階に対して指針を提供する。

(もっと読む)

半導体装置

【課題】微細化が可能な遅延回路部を有する半導体装置を提供する。

【解決手段】ゲート電極11g〜14gのトランジスタを有する論理回路部1aと、ゲート電極17g、18gが、それぞれ、配置されて形成されたPMOS及びNMOSトランジスタを構成トランジスタとするCMOSインバータを有し、CMOSインバータの構成トランジスタのそれぞれのドレインに、ドレイン同士が接続されたゲート電極19g、20gを有するノーマリオン型のPMOS及びNMOSトランジスタのそれぞれのソースが接続され、ゲート電極17g、18gの電位より低いゲート電位が印加される遅延生成部を有し、論理回路部1aの出力をCMOSインバータに入力して、遅延生成部のドレインから出力する遅延回路部3aと、ダミーゲート29gとを備え、ゲート電極11g〜20g及びダミーゲート29gが、所定の長さ及び幅を有し、間隔Dで正対した配列関係を有する。

(もっと読む)

半導体装置

【課題】 半導体装置においては、冗長回路や、基準電圧発生回路の調整のためにトランジスタのゲート絶縁膜を容量絶縁膜としたアンチヒューズが使用されている。しかしトランジスタのゲート絶縁膜が薄膜化されることで、ゲート絶縁膜を破壊した時にソフトブレークダウンとなり、良好なオーミック特性が得られにくいという問題がある。

【解決手段】 本発明のアンチヒューズは、容量絶縁膜として、サイドウォール絶縁膜を使用する。素子分離絶縁領域に基板と電気的にフローティングの状態で作られたトランジスタのゲート電極とSAC(セルフ・アライン・コンタクト)プロセスにより作成されたコンタクト電極を両電極として構成する。厚いサイドウォール絶縁膜を容量絶縁膜とすることで書き込み時にはハードブレークダウンとなり良好なオーミック特性が得られる。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】 クロックスキューの低減化およびチップ面積の削減化が図られた半導体集積回路を提供する。

【解決手段】 第1の半導体集積回路チップと第2の半導体集積回路チップとが互いに積層され、電気的に接続された半導体集積回路において、第1の半導体集積回路チップに配置されたクロック配線からクロック信号が供給された複数のフリップフロップ11と、第2の半導体集積回路チップに配置された組み合わせ論理回路群21とが、交互に接続されて形成された同期論理回路を備えた。

(もっと読む)

集積回路装置製造システム

【課題】回路パスの遅延値を設計遅延値に近づけることによって回路歩留まりの高い集積回路装置の製造が可能となる製造システムを提供する。

【解決手段】品種設計情報から得られるクリティカルパス内での論理セルの使用状況を記録したデータベース1と、検査工程S1で取得したゲート電極加工仕上がり寸法を記録したデータベース2とを入力として、データベース1に基づきモデル回路パスを生成し、データベース2のゲート電極仕上がり寸法を反映した当該モデル回路パスを用いて回路パス遅延5を算出する。トランジスタ特性と製造条件との相関関係を記録したデータベース100を参照して、回路パス設計遅延6と回路パス遅延5との差分11が小さくなるように新製造条件12を決定し、検査工程S1よりも後の工程の製造条件を変更する。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】微細・高集積化に対応して多層配線化された半導体集積回路装置において、ヒューズ部の切断による信頼性の低下や製造歩留りの低下を招くことなく、ヒューズ部の上部の開口部の形成時間を短縮して製造時間を短縮する。

【解決手段】半導体基板11上に形成された絶縁膜41と、絶縁膜41上に形成された配線層からなるヒューズ部13を備え、ヒューズ部13の配線層は、少なくとも銅からなる導電用金属層13Aを有する。また、ヒューズ部13の配線層は、絶縁膜41上に形成されたバリア金属層40をさらに備え、導電用金属層13Aは、バリア金属層40上に形成されている。

(もっと読む)

半導体装置

【課題】被トリミング素子の確実な溶断と下地基板のダメージ低減とを同時に実現可能な半導体装置を提供する。

【解決手段】下地基板10上に被トリミング素子20が配置されており、当該素子20に被さるように絶縁層30が配置されている。絶縁層30はシリコン酸化膜31から成り、具体的にはBPSG等のリンを含有したシリケートガラスが好ましい。酸化膜31において被トリミング素子20上の厚さdは約90〜270nmであり、酸化膜31は被トリミング素子20上においてトリミング用レーザーに対して約80%以上の透過率を有する。絶縁層30として被トリミング素子20上での厚さdが約65〜195nm程度のシリコン窒化膜を用いても上述の約80%以上の透過率が得られる。被トリミング素子20の下に回路素子14が配置されている。被トリミング素子20と酸化膜12との間にシリコン窒化膜を配置してもよい。

(もっと読む)

トリミングパターンおよびその溶断方法

【課題】トリミングパターンのヒューズ部の溶断に大電流を用いた場合においても、ヒューズ部の溶断後の切断幅を安定させて切断不良を低減すると共に半導体装置の主回路への熱影響を防止する手段を提供する。

【解決手段】第1の端子と、第2の端子と、第1および第2の端子の間に配置されたヒューズ部とを有するトリミングパターンにおいて、第1の端子とヒューズ部との間にエミッタ電極とベース電極とコレクタ電極とを有するバイポーラトランジスタを設け、第1の端子をエミッタ電極に接続すると共に、ヒューズ部の一端をコレクタ電極に接続し、他端を第2の端子に接続する。

(もっと読む)

冗長ビア構造を有する半導体装置

【課題】専有面積の少ない冗長ビア構造を提供する。

【解決手段】第1,第2の配線層間のビア構造が,絶縁層に形成される複数のビアホールと,第1の配線層に形成され,複数のビアホールを含むビアホール形成領域を第1の配線層の主配線方向に拡張し第2の配線層の第2の主配線方向には拡張しない領域を有する第1のビアランドと,第2の配線層に形成され,ビアホール領域を第2の主配線方向に拡張し第1の主配線方向には拡張しない領域を有する第2のビアランドとで構成する。

(もっと読む)

半導体装置及びヒューズの切断方法

【課題】レーザーで切断されるヒューズの下方に半導体素子を配置することができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1に形成された放電用の不純物領域7aと、半導体基板1上又は上方に形成された第1の絶縁膜8と、第1の絶縁膜8上に形成された遮光用導電膜10cと、遮光用導電膜10cを不純物領域7aに接地させる接地用配線9と、第1の絶縁膜8及び遮光用導電膜10cの上、又は上方に形成された第2の絶縁膜11と、第2の絶縁膜11上に形成され、遮光用導電膜11の上方に位置するヒューズ13とを具備する。

(もっと読む)

集積回路、および集積回路装置

【課題】論理素子、メモリ、論理素子領域などが固定されない集積回路および集積回路装置を提供する。

【解決手段】時間の経過t0、t1、t2、t3・・・tn(ただし、nは任意の整数)とともに回路機能が異なる素子の集合であって、時間の経過t0、t1、t2、t3・・・tnとともに異なる回路機能の部分が素子の全体集合である集積回路を用いる。また、時間の経過t0、t1、t2、t3・・・tnとともに回路機能が異なる素子の集合であって、時間の経過t0、t1、t2、t3・・・tnとともに回路機能の異なる部分が任意の個数の部分集合である集積回路を用いる。

(もっと読む)

自動設計プログラムおよび記録媒体

【課題】 面積を制御して所望の加工パターンを容易に設計することが可能な自動設計プログラムを提供する。

【解決手段】 加工形状の大きさの下限値のデータEaと、互いに隣接する前記加工形状の距離の下限値のデータWaと、前記加工形状の配列のピッチのデータP1と、が入力される第1の処理S20と、前記データP1に基づいて、前記加工形状が前記加工対象面に形成される個数のデータN1を算出する第2の処理と、前記加工形状の大きさのデータEを変更しながら前記加工形状の面積のデータS0を算出し、S0×N1で算出される前記加工パターンの面積のデータS1が、前記所定の面積範囲となる前記加工形状の大きさのデータE1を算出する第3の処理S30と、前記データP1、N1、E1で規定される加工パターンを形成する第4の処理S60と、をコンピュータに実行させる、自動設計プログラム。

(もっと読む)

半導体集積回路における容量付加方法および半導体集積回路

【課題】 FIB加工により付加する容量の容量値を把握できるようにする。

【解決手段】 デバイス周辺部の空き領域に配置されたFIB加工テスト用のインバータ7の入力端子にプローブ用入力パッド4を接続すると共に出力端子にプローブ用出力パッド5を接続し、該プローブ用出力パッド5に接続されるようにFIB加工により所定の形状寸法のパターンの容量C1を形成し、インバータ7を動作可能状態に設定してから、プローブ用入力パッド4に第1のプローブを介して信号を入力すると共にプローブ用出力パッド5から第2のプローブを介して出力信号を得て、該出力信号の実際の応答遷移時間と予め得ておいたインバータ7の応答遷移時間と容量値の関係特性とから容量C1の容量値を得て、該得た容量値の容量C1の前記パターンに基づき所望の箇所に所望の容量値の容量を付加する。

(もっと読む)

1 - 20 / 30

[ Back to top ]