Fターム[5F064HH01]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ハードウェア関係 (668)

Fターム[5F064HH01]の下位に属するFターム

Fターム[5F064HH01]に分類される特許

1 - 20 / 345

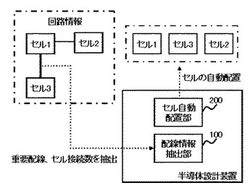

半導体設計装置、半導体設計方法及びプログラム

【課題】信号の重要度を考慮に入れたセルの自動配置を行うアルゴリズムは存在しない。従って、重要配線が不必要に長くなる場合がある。重要配線が長くなると、重要配線を伝達する信号を劣化させる原因となり得る。そのため、信号の重要度を考慮に入れたセルの自動配置を行うことで、重要度の高い信号の品質を維持する半導体装置を設計できる半導体設計装置、が望まれる。

【解決手段】半導体設計装置は、半導体装置に含まれる複数のセルを接続する複数の信号配線から、伝達する信号が重要であることを示す重要配線情報が付された重要配線と、複数の信号配線のそれぞれに接続されているセルの数を示すセル接続数と、を抽出する配線情報抽出部と、配線情報抽出部が抽出した重要配線及びセル接続数に応じて、複数のセルの配置を決定するセル自動配置部と、を備えている。

(もっと読む)

配線支援方法及び装置

【課題】配線すべき複数の信号線を、ユーザの指定する目的に従って適切にグループ化する。

【解決手段】配線すべき複数の信号線を複数のグループに分けるための方法は、ユーザから、複数の信号線のグループ化の条件の指定を受け付けるステップと、指定された、グループ化の条件と、データ格納部に格納されている、複数の信号線の始点端子群と終点端子群との配置パターンとに基づいて、複数の信号線のグループ化の処理を切り替えて実施する実施ステップとを含む。

(もっと読む)

半導体集積回路システムおよび半導体集積回路システムの配置配線方法

【課題】EMI低減に有効な半導体集積回路システムを提供する。

【解決手段】バスライン8上に配置された中央演算処理装置1と、演算論理装置6と、デカップリングキャパシタ形成領域100・合成論理形成領域200・インピーダンス形成領域300を有する半導体集積回路400と、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26・電源配線配置配線情報格納部28を有する記憶装置2とを備え、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26のそれぞれの格納データに基づいて、それぞれ合成論理形成領域200・デカップリングキャパシタ形成領域100・インピーダンス形成領域300における配置配線を実行する半導体集積回路システム10。

(もっと読む)

回路動作の検証装置及び回路動作の検証方法

【課題】電圧規格や電流規格を満たさない箇所があった場合に、その影響を反映させて検証を行うことができる回路動作の検証装置を提供する。

【解決手段】回路動作の検証装置は、結線情報4と、定格情報6とを用い、回路に入力する信号パターン7が与えられると、その入力パターン7に基づいて回路動作を検証する(S1〜S5)。そして、検証の結果、回路素子に印加される電圧や通電される電流等が定格値を超えることで破壊に至る回路素子が存在すると、当該回路素子を破壊の態様に応じた破壊状態モデルに置換し(S6)、破壊状態モデルに置換した回路について検証を継続する。

(もっと読む)

LSIのレイアウトパターン表示装置および表示方法

【課題】レイアウトパターン上で、直観的に回路素子を認識可能とし、回路素子間の信号の流れの把握を容易にする。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。条件設定部800には、セル枠決定に用いる特定のレイヤーを示す情報がセル枠決定条件として設定されており、セル枠決定部600は、個々のセルについて、当該特定のレイヤーに収録されている図形を抽出し、抽出した図形の論理和図形を形成し、この論理和図形の外接矩形をセル枠として求める。端子図形生成部500は、求めたセル枠とセル間配線との交差位置に端子図形を生成する。レイアウトパターン表示部400は、セル枠と端子図形をレイアウトパターン上に重畳表示する。

(もっと読む)

消費電流算出装置、消費電流算出プログラムおよび消費電流算出方法

【課題】ミックスドシグナル回路の消費電流を短時間で見積もること。

【解決手段】消費電流算出装置100は、対象回路へ入力されるデジタル信号の値113と、デジタル信号とともに対象回路へ入力されるアナログ信号の値112と、を取得する。消費電流算出装置100は、デジタル信号の値113およびアナログ信号の代表値の組み合わせごとに組み合わせが入力された場合の対象回路の消費電流を示す消費電流テーブル114から、デジタル信号の値113が対象回路へ入力された場合のアナログ信号の各代表値と消費電流との対応情報115を抽出する。消費電流算出装置100は、抽出した対応情報115に基づいて、アナログ信号の各代表値の間の値に対応する対象回路の消費電流を補間する補間関数116を生成し、生成した補間関数116に基づいて、アナログ信号の値112に対応する対象回路の消費電流117を算出する。

(もっと読む)

LSI設計方法,設計プログラムおよび設計装置

【課題】従来のLSI設計フローではクロックの遅延やスキューが無いことを前提とするため,クリティカルパスにてタイミングが仕様を満たさないことがSTA後に判明する。

【解決手段】ハードウェア記述ファイルと制約条件ファイルとから第1のクロックと第2のクロックのそれぞれのクロックツリーによる想定遅延値をそれぞれ生成し,第1のクロックと第2のクロックの想定遅延値をもとにしてクリティカルパスをデータベースへ登録するデータベース構築工程と,ハードウェア記述ファイルと制約条件ファイルについて論理合成を行うとともに,クリティカルパスをそれ以外のパスよりも優先して最適化し,ネットリストを生成する論理合成工程とを有するLSI設計方法。

(もっと読む)

ソフトウェアシミュレーション装置、シミュレーション方法、及びプログラム

【課題】不定値を適切に扱うことができるソフトウェアシミュレーションを実現するシミュレーション装置、シミュレーション方法、及びプログラムを提供すること

【解決手段】所定回路シミュレータ90は、所定の回路(たとえばフリップフロップ回路、メモリ回路)の動作を模擬(シミュレーション)する。不定値変換手段30は、所定回路シミュレータ90からの出力が不定値である場合に"0"または"1"に変換して後段のシミュレータに出力する。

(もっと読む)

消費電力解析装置及び方法

【課題】 本発明の課題は、組み合せ回路を含めた電力解析を効率的かつ高速に行うことを目的とする。

【解決手段】 上記課題は、回路の動作記述の抽象度が異なる概要回路モデルと、該概要回路モデルより抽象度が低い詳細回路モデルとを含む回路データと、該回路の電力検証方法に係る動作シーケンス・データとを記憶する記憶部と、論理回路の動作シミュレーションを行う論理シミュレーション部に、前記前記概要回路モデルと前記詳細回路モデルとを含む前記回路データをロードし、該記憶部に記憶されている前記動作シーケンス・データに従って、該概要回路モデルによって前記動作シミュレーションを行わせる概要モードと、該詳細回路モデルによって該動作シミュレーションを行わせる詳細モードとを切り替えて、該論理シミュレーション部に該動作シミュレーションを行わせるシミュレーション制御部とを有することを特徴とする消費電力解析装置により達成される。

(もっと読む)

配線抵抗網作成装置および配線抵抗網作成方法

【課題】配線形状の複雑化に起因するエレクトロマイグレーション解析の処理時間の増加を抑制する。

【解決手段】配線パターン分割部(22)と、ビア部分抵抗網設定部(25)と、配線部分抵抗網設定部(24)と、配線抵抗・ビア抵抗接続部(28)を有する配線抵抗網作成装置(10)を構成する。配線パターン分割部(22)は、レイアウトデータからビアとの接続位置情報を含む配線パターンを取得し、配線パターンをアレイビア部分と配線部分に分割する。ビア部分抵抗網設定部(25)は、アレイビア部分に対応するビアノードおよびビア部分抵抗を含むビア部分抵抗網を設定する。配線部分抵抗網設定部(24)は、配線部分に対応する配線ノードおよび配線部分抵抗を含む配線部分抵抗網を設定する。配線抵抗・ビア抵抗接続部(28)は、ビア部分抵抗網と配線部分抵抗網を接続して配線抵抗網データを生成する。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

原版データの生成方法、原版作成方法、原版データを作成するためのプログラム及び処理装置

【課題】 微細なパターンを精度よく形成する原版のデータを生成する生成方法を提供する。

【解決手段】 光源からの光を用いて原版を照明する照明光学系と、前記原版のパターンを基板に投影する投影光学系とを備える露光装置に用いられる原版のデータをコンピュータによって生成する生成方法であって、近似空中像に基づいて主パターンを決定し、補助パターンを挿入することで原版のデータを生成する生成方法を提供する。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

レイアウト設計方法及びレイアウト設計装置

【課題】チップ面積を小さくすることのできるレイアウト設計方法を提供する。

【解決手段】レイアウト設計方法は、所定のタイミング制約F1を満足させるように、セルを配置し、低抵抗配線が形成される第1配線層を使用してセル間のパスの接続配線を形成する処理(ステップS2〜S4)を有する。また、レイアウト設計方法は、タイミング制約F1を満足させたまま、パスの接続配線のうち、セル間に配置されるバッファ回路によって区切られる複数のステージ中の少なくとも一つのステージに対応する接続配線におけるレシーバ側からの一部を、第1配線層から該第1配線層よりも配線遅延が大きくなる第2配線層に置き換えて形成する配線置換処理(ステップS5)を有する。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

ノイズ振幅評価方法、ノイズ振幅評価装置およびプログラム

【課題】トラップによって引き起こされる半導体集積回路の特性変位量を精度良く高速に求める。

【解決手段】半導体集積回路を構成するトランジスタ中のトラップの数を乱数により決定する工程(ステップS02)と、トラップの各々の属性値を乱数により決定する工程(ステップS03)と、トラップの集合の部分集合であって、部分集合に属するトラップがすべて同時に特性変動を起こした状態に遭遇する確率と、部分集合に属するトラップがすべて同時に特性変動を起こしたときに生じる半導体集積回路の特性変位量と、から所定の期間内に生じる半導体集積回路の特性変位量を推測する工程(ステップS04)と、を含む。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

1 - 20 / 345

[ Back to top ]