Fターム[5F064HH08]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ソフトウェア(プログラム)関係 (5,214) | 使用言語 (170)

Fターム[5F064HH08]に分類される特許

1 - 20 / 170

設計支援装置

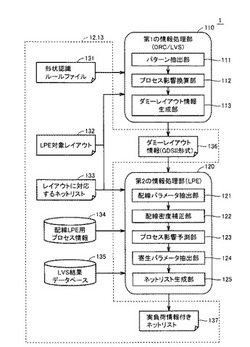

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

検証装置、検証方法及びプログラム

【課題】検証する範囲を少なくして、検証コストや検証時間の増大を抑制する。

【解決手段】抽出部12が、第1のクロック信号で動作する回路部21と、第2のクロック信号で動作する回路部22とを含む検証対象回路(論理回路20)から、ハンドシェイクの手順に従って回路部21と回路部22間でのデータの送受信を行うハンドシェイク部23を抽出し、検証部13が抽出されたハンドシェイク部23の信号が、その手順を満たすかを検証し、手順を満たさない信号があるとき、回路部21と回路部22のうち当該信号を出力する側で、当該信号が手順を満たさなくなる条件が回路動作時に起こり得るか検証する。

(もっと読む)

ソフトウェアシミュレーション装置、シミュレーション方法、及びプログラム

【課題】不定値を適切に扱うことができるソフトウェアシミュレーションを実現するシミュレーション装置、シミュレーション方法、及びプログラムを提供すること

【解決手段】所定回路シミュレータ90は、所定の回路(たとえばフリップフロップ回路、メモリ回路)の動作を模擬(シミュレーション)する。不定値変換手段30は、所定回路シミュレータ90からの出力が不定値である場合に"0"または"1"に変換して後段のシミュレータに出力する。

(もっと読む)

半導体装置設計方法および半導体装置設計支援プログラム

【課題】EBDに近いモデリング精度を維持しつつ、モデリングの効率を高める。

【解決手段】複数のチップ(CHIP1〜4)が積層され、それぞれのチップが共通の外部端子104に接続される積層型の半導体装置100の設計に関する。まず、電磁界解析ツールにより、外部端子104とチップを接続するプリント基板配線(共通配線106、個別配線108)の電気的なパラメータを算出し、それらをEBDのパラメータとして設定する。設定されたパラメータに基づいて半導体装置100の電気的な特性をシミュレーション計算する。パラメータの計算・設定に際しては、所定の配線、たとえば、共通配線106や個別配線108などのプリント基板配線の長さを示すパラメータをゼロに設定する。

(もっと読む)

電子回路網の信頼性を向上させるための装置および関連する方法

【課題】電子回路網の信頼性を向上させるための装置および関連する方法を提供すること。

【解決手段】上記装置は、装置の第1の構成に使用される第1のセットの回路要素と、装置の第2の構成に使用される第2のセットの回路要素とを含み、装置の第1の構成は、装置の信頼性を向上させるために、装置の第2の構成に切り替えられる。上記方法は、第1の構成に割り当てられた第1のセットの回路要素を使用することによって、第1の構成で集積回路(IC)を動作させることと、第2の構成に割り当てられた第2のセットの回路要素を使用することによって、第2の構成でICを動作させることとを含み、第1の構成でICを動作させた後に第2の構成でICを動作させるのは、ICの信頼性を向上させる。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

クロックツリー生成方法、クロックツリー生成プログラム、記録媒体、およびクロックツリー生成装置

【課題】外部電源電圧が変動した場合でも、安定に動作する半導体装置を実現することが可能なクロックツリー生成方法を提供する。

【解決手段】プログラム5のCTS部8は、電源領域Aから電源領域Bにクロック信号CLK1,CLK2を伝達する経路L1,L2を設け、電源領域A内の経路L1,L2にそれぞれアンカーバッファB1,B2を配置し、遅延回路D1,D2を電源領域B内の経路L1,L2にそれぞれ配置し、遅延回路D3,D4をアンカーバッファB1,B2の入力ノード側の経路L1,L2にそれぞれ配置する。したがって、外部電源電圧VDD1,VDD2が変動した場合でも、クロック信号CLK1,CLK2の遅延時間は同じになる。

(もっと読む)

回路シミュレーション方法および回路シミュレーション装置

【課題】寄生素子を考慮した半導体集積回路の回路シミュレーションにおいて、精度を落とさずにシミュレーション時間を短縮する。

【解決手段】半導体集積回路のレイアウトデータ110から寄生素子を含むネットリスト130を作成する寄生素子抽出部120と、寄生の影響を考慮する必要の無い回路ブロック情報を格納したデータベース部150と、データベース部150内に登録された回路ブロックが、対象としている半導体集積回路に存在するか否か判定する回路判定部160と、同じ回路ブロックが存在すると判定された時に、レイアウトデータ110から抽出したネットリスト130の中で、同じ回路ブロックと判断された部分のネットリストをネットリスト置換部180によって、寄生素子を含まない回路ブロックのネットリスト130Zに置換することで不要な寄生素子を削除しネットリストを簡素化して、回路シミュレータ190で回路シミュレーションを実施する。

(もっと読む)

動作合成方法,装置およびプログラム

【課題】 動作合成において,動作記述をパイプライン処理する際にオペレーションを各ステージに偏りなく配置したRTLを生成することを目的とする。

【解決手段】 動作合成装置1は,動作記述を解析してオペレーションを演算単位に分割し,分割オペレーションの実行順序と各々の処理時間を算出するオペレーション分割部16と,動作記述からパスを選択し,パス内の分割オペレーションの総処理時間をパイプライン処理のステージ数で割ってステージ内処理時間を求め,選択したパスでの分割オペレーションの実行順序にもとづいて分割オペレーションを順にステージに割り当て,割り当てた分割オペレーションの処理時間の合計がステージ内処理時間を超えたときに,そのステージに割り当てている分割オペレーションを,該ステージに配置するステージ割当部17と,該ステージの配置をもとに動作記述をRTL記述に変換する出力部18を備える。

(もっと読む)

クロック経路抽出装置

【課題】タイミング検証におけるクロック系統の解析時間を短縮することのできるクロック経路抽出装置を提供する。

【解決手段】実施形態のクロック経路抽出装置1は、クロック経路探索部11が、RTL記述データ100を解析し、指定されたモジュールのクロック端子からクロック生成起点までのクロック経路を探索し、クロック経路抽出部12が、クロック制御情報200にもとづいて無効クロック経路を除外し、有効クロック経路のみを抽出する。さらに、クロック系統図生成部13が、クロック生成起点のクロック周波数情報300にもとづいて、クロック周波数が同一である有効クロック経路を有する複数のモジュールを、クロック周波数ごとに1つのブロックに集約し、そのブロックおよびクロック生成起点をそれぞれ図形で表し、その図形間を1本のクロック線で結んだクロック系統図を生成する。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体集積回路の設計方法及び半導体集積回路の設計支援装置

【課題】論理回路の面積縮小化を実現しつつ、設計TATの短縮を可能とする技術を提供する。

【解決手段】複合論理マクロセルを、基本マクロセルに置き換えて面積の総和を抽出し、その面積の総和と複合論理マクロセルの面積とを比較して面積縮小化に有効となる複合論理マクロセルを選択する。その選択された複合論理マクロセルにフラグを設定する。フラグを設定したマクロセルと同等の論理を論理情報から検索する論理構造検索処理を行い、置換対象となる基本マクロセルにフラグを設定する。置換対象のフラグを設定した基本マクロセルを、フラグ設定した複合論理マクロセルに置き換える等価論理置換処理を行う。

(もっと読む)

論理シミュレーション方法および論理シミュレーション装置

【課題】論理シミュレーションに要する時間を削減する。

【解決手段】RTL記述の論理シミュレーション結果とゲートレベルの論理シミュレーション結果とが一致しているか否かを判定する。そして、判定結果が不一致であった場合に、RTL記述の論理シミュレーション結果情報とゲートレベルの論理シミュレーション結果情報の不一致箇所を抽出する。抽出した不一致ポイントに基づき、ゲートレベルの論理シミュレーション結果情報をRTL記述の論理シミュレーション結果情報に強制代入記述を作成する。その強制代入記述を含むForceファイルに基づき再度ゲートレベルの論理シミュレーションを実施する。

(もっと読む)

半導体集積回路の設計方法および設計装置

【課題】無駄領域を削減するとともに配線混雑の発生も抑制できる回路設計方法を提供する。

【解決手段】データフローを参照し、同じタイミングで動作するレジスタ群を終点として、それらの終点レジスタから同じタイミングで動作する前段方向の始点レジスタ群までを一つの集まりとしてクラスタ化する。クラスタ化したクラスタをさらに複数のクラスタに分割する場合(ST207)、分割後のクラスタ同士が共有する始点レジスタを複製して(ST235)、分割されたクラスタ同士で始点レジスタを共有しないようにする。

(もっと読む)

設計支援装置、設計支援方法および設計支援プログラム

【課題】処理の高速化を図ること。

【解決手段】記憶部1a1は、複数の階層を有する半導体集積回路モデル2の階層Cに属するモジュール2dが備える配線のうち、階層Cより上位の階層A、Bに属するモジュール2a、2bが備える配線に対し加害者ネットまたは被害者ネットとなる可能性のある配線L1に関する配線情報D1を記憶する。配線特定部1bは、階層Bに属するモジュール2b内で閉じた配線であり、かつ、記憶部1a1に記憶されている配線情報D1の配線L1に対する被害者ネットまたは加害者ネットとなる配線を特定する。

(もっと読む)

回路モデル生成装置

【課題】 本発明の課題は、素子データを含むアナログ回路モデルを生成することを目的とする。

【解決手段】 上記課題は、回路図データとレイアウトデータとを格納する記憶領域と、前記レイアウトデータから寄生素子に係る素子データを抽出する抽出手段と、前記回路図データに前記素子データを含む回路モデルをハードウェア記述言語によって生成する回路モデル生成手段とを有する回路モデル生成装置により達成される。

(もっと読む)

設計ライブラリデータベース

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】1実施形態に係る設計ライブラリデータベースは、2次元的に区画して各々薄膜トランジスタのチャネル領域のサイズを超える複数の結晶粒規定領域が配置された結晶化半導体薄膜を用いる薄膜トランジスタ回路の設計ライブラリデータベースであって、各々のチャネル領域が単一の前記結晶粒規定領域内の固定位置に配置される2個以上の薄膜トランジスタおよび前記2個以上の薄膜トランジスタを相互接続する配線を含む様々な論理ゲート回路をそれぞれ表す複数のスタンダードセル、並びに前記様々な論理ゲート回路の様々な組み合わせをそれぞれ表す複数のマクロセルの少なくとも一方のセルのライブラリ、および前記複数の結晶粒規定領域が配置された結晶化アレイパターンのスタンダードセルのライブラリを含みハードディスクに登録される。

(もっと読む)

アサーションベース検証装置、およびアサーションベース検証方法

【課題】大規模で複雑化した半導体集積回路に対する機能検証を効率よく実行しつつ、検証対象の半導体集積回路の品質を向上させる技術を提供する。

【解決手段】論理シミュレーション実行部(15)(17)の機能によって、制御可アサーション記述ファイル(25)の、処理対象アサーション記述と処理非対象アサーション記述とを特定する。処理対象アサーション記述を用いてDUT(22)に対するアサーションベース検証を実行しつつ、発火条件を満足したか否かを判定した結果に基づいて発火情報レジスタ(28)を書き換える。発火情報レジスタ(28)のデータに基づいてアサーション制御情報(27)を更新して新たなアサーション制御情報(27)とし、新たなアサーション制御情報(27)を用いてアサーションベース検証を実行する。

(もっと読む)

半導体集積回路の検証装置及び検証方法

【課題】設計品質の向上を可能とする。

【解決手段】半導体集積回路を構成する回路の接続関係を示す接続仕様情報と、前記半導体集積回路の構成を記述した回路記述情報との回路接続関係の一致性を検証する半導体集積回路の検証装置であって、前記接続仕様情報をアサーション言語で記述された接続情報ファイルに変換するアサーション生成部と、前記接続仕様情報からオープンである端子を抽出した第1の端子情報と、前記回路記述情報からオープンである端子の情報を抽出した第2の端子情報とに応じて、前記第1の端子情報と第2の端子情報の一致性を比較する比較部と、前記接続情報ファイルと前記回路記述情報とに応じてフォーマル検証を行うフォーマル検証部と、を有し、前記フォーマル検証部の検証結果と前記比較部の比較結果から、半導体集積回路を構成する回路の接続関係を検証する半導体集積回路の検証装置。

(もっと読む)

1 - 20 / 170

[ Back to top ]