Fターム[5F064HH15]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | 出力、表示 (483) | 図形表示 (122)

Fターム[5F064HH15]の下位に属するFターム

拡大、縮小表示 (8)

Fターム[5F064HH15]に分類される特許

1 - 20 / 114

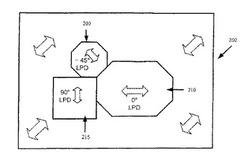

局所優先方向アーキテクチャ、ツール、及び機器

【課題】「局所優先方向」配線モデルを使用してネットをルーティングするための機器を提供する。

【解決手段】本発明の一部の実施形態は、1つ又はそれよりも多くのEDAツール(プレーシング、ルーティングなどのような)と共に使用される「局所優先方向(LPD)」配線モデルを提供する。LPD配線モデルは、少なくとも1つの配線層が、各々が特定の配線層とは異なる優先方向を有する一組の領域を有することを可能にするものである。更に、各領域は、その組における少なくとも1つの他の領域の局所優先方向とは異なる局所優先方向を有する。更に、少なくとも2つの領域は、2つの異なる多角形形状を有し、その組における領域は、その組における別の領域を取り囲むことはない。

(もっと読む)

LSIのレイアウトパターン表示装置および表示方法

【課題】レイアウトパターン上で、直観的に回路素子を認識可能とし、回路素子間の信号の流れの把握を容易にする。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。条件設定部800には、セル枠決定に用いる特定のレイヤーを示す情報がセル枠決定条件として設定されており、セル枠決定部600は、個々のセルについて、当該特定のレイヤーに収録されている図形を抽出し、抽出した図形の論理和図形を形成し、この論理和図形の外接矩形をセル枠として求める。端子図形生成部500は、求めたセル枠とセル間配線との交差位置に端子図形を生成する。レイアウトパターン表示部400は、セル枠と端子図形をレイアウトパターン上に重畳表示する。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

レイアウト検証装置及びレイアウト検証方法

【課題】汎用性が高く、効率的に検証処理を行うことができるレイアウト検証技術を提供する。

【解決手段】レイアウトデータがデザインルールに反するか否かの検証を行うに際し、所定の設計値に基づき、レイアウトデータ(1)を、擬似エラー領域内のものとそれ以外のものとに区分し、通常のデザインルール(4)からの許容範囲内のものとして擬似エラー領域用のデザインルール(13)を作成し、擬似エラー領域外のレイアウトデータについては通常のデザインルールで検証を行い、擬似エラー領域内のレイアウトデータについては擬似エラー領域用のデザインルールで検証を行う。

(もっと読む)

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

クロック経路抽出装置

【課題】タイミング検証におけるクロック系統の解析時間を短縮することのできるクロック経路抽出装置を提供する。

【解決手段】実施形態のクロック経路抽出装置1は、クロック経路探索部11が、RTL記述データ100を解析し、指定されたモジュールのクロック端子からクロック生成起点までのクロック経路を探索し、クロック経路抽出部12が、クロック制御情報200にもとづいて無効クロック経路を除外し、有効クロック経路のみを抽出する。さらに、クロック系統図生成部13が、クロック生成起点のクロック周波数情報300にもとづいて、クロック周波数が同一である有効クロック経路を有する複数のモジュールを、クロック周波数ごとに1つのブロックに集約し、そのブロックおよびクロック生成起点をそれぞれ図形で表し、その図形間を1本のクロック線で結んだクロック系統図を生成する。

(もっと読む)

設計支援装置、設計支援方法および設計支援プログラム

【課題】処理の高速化を図ること。

【解決手段】記憶部1a1は、複数の階層を有する半導体集積回路モデル2の階層Cに属するモジュール2dが備える配線のうち、階層Cより上位の階層A、Bに属するモジュール2a、2bが備える配線に対し加害者ネットまたは被害者ネットとなる可能性のある配線L1に関する配線情報D1を記憶する。配線特定部1bは、階層Bに属するモジュール2b内で閉じた配線であり、かつ、記憶部1a1に記憶されている配線情報D1の配線L1に対する被害者ネットまたは加害者ネットとなる配線を特定する。

(もっと読む)

未知の半導体装置の機能の非破壊的な決定

【課題】外部放射線に対して応答する接合を分析することを通して機能を推測することによる、集積回路の非破壊的なリバースエンジニアリングのためのシステム及び技術を提供する。

【解決手段】少なくとも1つの電源と電気的に導通している複数の半導体接合を含む半導体装置の機能を決定するための以下を含む方法。

・半導体装置の表面を照射すること;

・照射に応答する複数の半導体接合のうち少なくとも幾つかのレイアウトを決定すること;

・決定されたレイアウト内で、複数の半導体接合の少なくとも幾つかのグルーピングを同定し、各ブルーピングはそれぞれの機能セルを表すこと;

・複数の外部アクセス可能な接点のうち少なくとも1つへの刺激を変化させること;及び

・前記変化した刺激に応答して複数の相互接続された機能セルの1つ以上の接続を推測すること。

(もっと読む)

データ生成方法

【課題】エッチング処理により基板上に設計データ通りの配線パターンを形成できるようにする、レジストパターンのデータを生成するデータ生成方法を実現する。

【解決手段】レジストパターンのデータ生成方法は、基板面に相当する仮想平面上において、設計データに規定された配線の外郭上の或るポイントを基準点として所定形状を有し、当該ポイント上に位置するエッチング液によって銅箔がエッチングされ得るエッチング影響エリアを含む第1の基準エリアを設定する設定ステップS101と、レジストパターンの外郭の位置を、第1の基準エリアに占めるエッチング影響エリアの面積を表わすエリア面積パラメータに応じて決定する決定ステップS102と、設計データに規定された配線の外郭上の任意の位置に順次設定されるポイントに対して設定ステップS101および決定ステップS102を繰り返し実行することで、レジストパターンの外郭を画定する画定ステップS103と、を備える。

(もっと読む)

配線設計支援方法、配線設計支援プログラム、及び配線設計支援装置

【課題】バスの配線経路の設計精度を向上させること。

【解決手段】コンピュータが、一以上の配線層を含む配線領域に対して、それぞれ図形によって表現された複数のバスの経路を前記バス間で交差しないように生成する配線プラン生成手順と、前記バスごとに、当該バスが接続される部品内からの当該バスの所属ネットごとの配線の引き出しの可否の検証を行う妥当性判定手順と、前記妥当性判定手順によって全ての前記所属ネットが引き出せることが確認された前記バスの前記所属ネットを示す図形を前記配線領域に記録する配線プラン確定手順とを実行し、前記妥当性判定手順によって少なくとも一部の前記所属ネットが引き出せないことが確認された前記バスについて前記配線プラン生成手順を再実行する。

(もっと読む)

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

フロアプランデータ生成装置及び方法

【課題】チップの設計期間を短縮する。

【解決手段】CPU1は、設計対象の回路を構成するセルのうち、所定のサイズより大きいセルサイズを有するセルのみの回路情報をゲートレベルで記述した簡易ネットリスト43と、所定のサイズより大きいセルサイズを有するセルのみの仕様データを含むセルリスト44とを用いてフロアプランを行い、仮フロアプランデータ47を生成する。CPU1は、ユーザによって回路全体のフロアプランが行われるときに、回路を構成するセルの仕様データである全体ライブラリ42と、回路を構成するセルの回路情報をゲートレベルで記述した全体ネットリスト45と、仮フロアプランデータ47と、簡易ネットリスト43を全体ネットリスト45に整合させるためのセルリスト44とを出力する。

(もっと読む)

半導体集積回路装置およびその製造方法、配線配置装置、配線配置方法、配線配置プログラム、並びに記録媒体

【課題】スタンダードセルを利用して機能回路ブロックをレイアウトする際、供給電源の品質を動作レベルに保ちながら、製造品質を左右する各配線層の占有率のばらつきを少なくする。

【解決手段】スタンダードセル1を、これを構成するセル構成トランジスタを有し、全スタンダードセルに共通接続される電源供給配線及び接地供給配線、および個々のスタンダードセルの機能を実現するための信号配線を含まず、かつ各スタンダードセルの機能を該セル構成トランジスタにより決定する最小限の配置配線、および該セル構成トランジスタの直近に配置され、該スタンダードセルの信号端子を含むよう構成した。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】局所的に高温となる領域の温度を低下させること。

【解決手段】

設計支援装置は、設計対象回路のレイアウトデータ100内で所定温度以上となる領域1を有する熱解析結果と、当該レイアウトデータ100内のパスに関する解析結果とを取得する。そして、領域1内に配置されているセルの中から非クリティカルパス上の任意のセルを領域1の温度を低下させる対象セルに決定し、決定結果を出力する。つぎに、決定された対象セルに対して温度を低下させる処理を実施する。対象セルの出力に抵抗素子を接続させる。または、対象セルの配置位置を領域1の外に再配置させるか、対象セルのセルタイプを消費電力値の低いセルタイプに変換する。

(もっと読む)

配線設計方法、設計装置及びプログラム

【課題】設計時間の短縮を図ること。

【解決手段】設計装置の記憶装置には、半導体装置を検証ステップの格子にて区画した各領域に含まれるレイアウトパターンの面積がそれぞれ格納されるセル面積テーブルと、移動される検証エリアの位置に対応し、各検証エリアには所定数の領域が含まれ、検証エリアに対してその検証エリアに含まれるレイアウトパターンの占有率が、各検証エリアに対応して格納されるセル占有率テーブルを含む面積DB33が記憶される。図形DB32にはインスタンスの面積テーブルが含まれる。CPUは、配置されたインスタンスの面積テーブルに従って編集対象のセル面積テーブルを変更し、そのセル面積テーブルに従ってセル占有率テーブルを更新し、セル占有率テーブルの値によりレイアウトパターンの占有面積をチェックする。

(もっと読む)

アップサンプリング装置及びダウンサンプリング装置

【課題】レイアウトデータの階層構造を有効に利用して、精度を高く維持しつつ処理の能率を高めることのできるアップサンプリング装置、ダウンサンプリング装置を提供する。

【解決手段】アップサンプリング部44は、メッシュ付加部441および新メッシュデータ設定部442を備えている。メッシュ付加部441は、空間フィルタ部423から入力される画像データに新たなメッシュを付加する。新メッシュデータ設定部442は、付加されたメッシュ上の画像データにゼロの値を設定し、メッシュが付加される前の画像データとともに、逆フーリエ変換部424へ出力する。

(もっと読む)

回路設計装置および回路設計プログラム

【課題】GUI機能を利用しスタティックノイズの改善を効率よく行なえるようにする。

【解決手段】ノイズチェック結果に基づき回路設計を行なうものであって、表示部30と、前記表示部30の制御を行なう表示制御部と、注目配線を指定する指定部と、前記指定部によって指定された前記注目配線のノイズチェック対象となる配線区間を有する全ての配線を、影響配線として、配線結果を保持するデータベースから抽出する影響配線抽出部とを有している。そして、前記表示制御部は、前記注目配線と前記影響配線抽出部によって抽出された前記影響配線とを前記表示部30で表示する制御を行なう。

(もっと読む)

デバイス特性出力装置及びデバイス特性出力プログラムを記憶する記憶媒体

【課題】デバイス特性の変化量に依存することなく、ユーザにとって見やすいシミュレーション結果を出力する。

【解決手段】デバイス特性出力装置10は、デバイス特性の実測データ、デバイス特性のターゲットを示すターゲットデータ、及びデバイス特性のシミュレーション結果を示す第1シミュレーションデータの入力を受け付ける入力部14aと、実測データとターゲットデータとの関係を示すリファレンスデータを生成するリファレンスデータ生成部14bと、リファレンスデータに基づいて、第1シミュレーションデータを異なるスケールで表される第2シミュレーションデータに変換する変換部14cと、第2シミュレーションデータを出力する出力部14eと、を備える。

(もっと読む)

半導体装置、下層配線設計装置、下層配線設計方法およびコンピュータプログラム

【課題】MIMキャパシタの構造破壊に起因するリーク電流の上昇を低減する構成を備えた半導体装置を提供することを課題とする。

【解決手段】複数の下層配線11を備える下層配線層10と、下層配線層10の上方に設けられる、下部電極21と容量誘電膜22と平面形状が下部電極21より小さい上部電極23とを下からこの順に積層したMIMキャパシタ20と、MIMキャパシタ20の上方に設けられ、ビア40、41を介して下部電極21および上部電極23のそれぞれに接続する複数の上層配線31を備える上層配線層30と、を備えた半導体装置であって、上部電極23の平面形状は矩形に構成され、上部電極23の平面のいずれか一以上の辺であるエッジ部の直下には下層配線11が配置されていない半導体装置を提供する。

(もっと読む)

設計支援装置、設計支援方法及び設計支援プログラム

【課題】設計支援装置、設計支援方法及び設計支援プログラムにおいて、LSIの配線の解析及び設計変更を容易に行うことを目的とする。

【解決手段】半導体装置の物理設計を行う設計支援装置において、表示装置と、配線を前記表示装置に表示する際に、各配線の消費電力に関する要素に基づく強調表示と、各配線の設計変更の難易度に関する要素に基づく強調表示の少なくとも一方を前記表示装置に表示させる演算処理装置を備えるようにする。

(もっと読む)

1 - 20 / 114

[ Back to top ]