Fターム[5F082BA35]の内容

Fターム[5F082BA35]の下位に属するFターム

Fターム[5F082BA35]に分類される特許

1 - 20 / 192

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

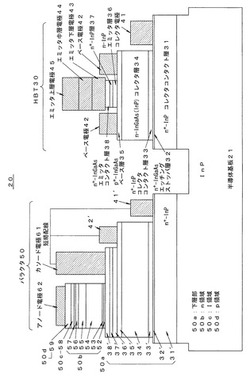

トランジスタ素子

【課題】単体構造のHBTデバイスと同等の信頼性を得る。

【解決手段】化合物半導体からなる、高電子移動度トランジスタ(HEMT)とヘテロバイポーラトランジスタ(HBT)とを、同一基板上に重ねてエピタキシャル成長した多層構造のトランジスタ素子において、エピ層として内在するインジウムガリウムリン層(InGaP)のバンドギャップエネルギを1.91eV以上にすることを特徴とする。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

電圧検知回路

【課題】高精度で低コストの電圧検知回路を提供する。

【解決手段】パワーオンリセット回路は、分圧回路1、バイポーラトランジスタQ1,Q2、抵抗素子R1,R2、およびベース電流補償回路10を備える。分圧回路1の出力電圧VINがバンドギャップ電圧VBGの場合、バイポーラトランジスタQ1,Q2のコレクタ電流I1,I2が一致する。電圧補償回路10は、電流I1に基いてバイポーラトランジスタQ1,Q2のベース電流の和に相当する電流I6を生成し、その電流I6をバイポーラトランジスタQ1,Q2のベースに供給する。したがって、バイポーラトランジスタQ1,Q2の各々のベース電流が大きい場合でも、高い検出精度が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】BiCMOSプロセスにより製造される半導体装置において、V−NPNトランジスタの製造工程を合理化する。また、そのトランジスタのhFEを大きな値に調整する。

【解決手段】N+型エミッタ領域14Eの下のP型ベース領域7の底部に接触してN型ベース幅制御層9が形成されている。N型ベース幅制御層9が形成されることで、N+型エミッタ領域14Eの下のP型ベース領域7が局所的に浅くなっている。また、P型ベース領域7は、P型ウエル領域6の形成工程を用いて形成し、N型ベース幅制御層9は、N型ウエル領域8の形成工程を用いて形成することにより、工程合理化を図ることができる。

(もっと読む)

III−V族化合物半導体エピタキシャルウエハ

【課題】充分な選択比を備え、また、除去が比較的容易なエッチングストッパ層を得る。

【解決手段】GaAs基板10上に設けられた高電子移動度トランジスタ構造20と、高電子移動度トランジスタ構造20の上に設けられたヘテロ接合バイポーラトランジスタ構造40と、を備え、高電子移動度トランジスタ構造20とヘテロ接合バイポーラトランジスタ構造40との間には、As濃度が1.0×1016atoms/cc以上1.0×1021atoms/cc以下のInGaAsP層からなるエッチングストッパ層30を備える。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ

【課題】オン抵抗の低いストッパー層を有するIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板8上に、GaAs層、AlGaAs層からなるバッファ層9、n型不純物を含有するAlGaAs層又はInGaP層若しくはSiプレナードープ層からなる電子供給層10、InGaAs層からなるチャネル層12、ノンドープ又は低濃度n型不純物を含有するGaAs層又はAlGaAs層からなるショットキー層14、ノンドープ又は低濃度n型不純物を含有するInGaP層からなるストッパー層15、n型不純物を含有するGaAs層からなるキャップ層16を積層したHEMT構造18を有するIII−V族化合物半導体エピタキシャルウェハ17において、ストッパー層15におけるInGaP中のAsが占めるV族原子分率が15%以下であるものである。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

トランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法

【課題】GaAs基板からHBT構造層に伝搬する転位を抑制したトランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ構造層3が形成され、高電子移動度トランジスタ構造層3上にヘテロバイポーラトランジスタ構造層4が形成されたトランジスタ素子において、GaAs基板2の転位密度が10,000/cm2以上100,000/cm2以下であり、高電子移動度トランジスタ構造層3とヘテロバイポーラトランジスタ構造層4との間に、InGaPからなるエッチングストッパ層12と、エッチングストッパ層12上に設けられたGaAsからなる安定化層21と、を設けたものである。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

1 - 20 / 192

[ Back to top ]