Fターム[5F082BC11]の内容

Fターム[5F082BC11]の下位に属するFターム

ショットキ (20)

Fターム[5F082BC11]に分類される特許

1 - 20 / 184

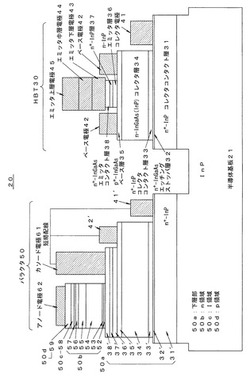

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

低減したクランプ電圧を有するESD保護デバイス

【課題】寄生容量に悪影響を与えることなく、より低いクランプ電圧が達成できるESD保護回路を提供する。

【解決手段】ESD保護回路は、第1および第2端子(T1,T2)の間にある主要なESD電流伝導経路において、複数のバイポーラトランジスタ、即ち、複数のESD電流伝導トランジスタ(q1,q2,q4)を備え、ESD電流伝導トランジスタの少なくとも1つ(q1)と並列に接続され、ESDイベントの発生時に、ESD電流伝導トランジスタの1つ又はそれ以上(q2)に駆動電流(Ib2)を伝導するために設けられた少なくとも1つの駆動トランジスタ(q3)をさらに備える。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体素子の製造方法、ESD保護素子の製造方法

【課題】半導体ウエハに厚みばらつきがある前提で、コストアップをすることなく高品質の半導体素子を提供すること。

【解決手段】第1導電型の活性層の下に第1導電型の埋込拡散層を有する半導体基板を準備するステップと、活性層と埋込拡散層の総厚を測定し、測定した総厚から前記活性層の厚さを求めるステップと、活性層に、埋込拡散層との間で電流が流れる第1導電型のコレクタ領域をイオン注入によって形成するステップと、活性層に、埋込拡散層との間で電流が流れる第2導電型のベース領域をイオン注入によって形成するステップと、ベース領域内に、ベース領域との間で電流が流れる第1導電型のエミッタ領域をイオン注入によって形成するステップとを備え、ベース領域を形成するステップは、活性層の厚さに応じてイオン加速エネルギーを変化させるステップであることを特徴とする。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

半導体装置

【課題】不要な寄生素子の影響を排除できる低容量の過渡電圧保護素子を提供する。

【解決手段】半導体基板上に第1のエピタキシャル層210を形成し、第1のエピタキシャル層の表面近傍に埋め込み層220を形成し、埋め込み層上に第2のエピタキシャル層211を形成し、第2のエピタキシャル層内に第1のディープ拡散層250を形成し、第1のディープ拡散層内にツェナーダイオードを形成し、ツェナーダイオードから離れた位置に第1のPNダイオードを形成し、ツェナーダイオードは第1の分離層240により分離されており、第1のPNダイオードは第2の分離層241で分離されており、ツェナーダイオードと第1のPNダイオードが埋め込み層を経由して逆方向に直列接続されることにより、不要な寄生素子の影響を排除でき、かつ低容量の過渡電圧保護素子を実現する。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

過電圧保護回路及び半導体集積回路

【課題】異常な過電圧から内部回路を確実に保護することができる過電圧保護回路を提供する。

【解決手段】過電圧保護回路2Aは、整流素子D10と、互いに並列に接続された第1段から第n段(nは2以上の整数)のスイッチング素子NM1〜NMnとを備える。スイッチング素子NM1〜NMnは、整流素子D10の出力端からの出力電圧が印加される第1から第nの制御端をそれぞれ有する。また、スイッチング素子NM1〜NMnの各々は、第1端子3及び第2端子4にそれぞれ接続された被制御端を有する。整流素子D10は、第1端子3から過電圧が入力されたとき、スイッチング素子NM1〜NMnをオン状態にする制御電圧を出力する。

(もっと読む)

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

半導体集積回路のESD保護素子およびそのESD保護回路

【課題】電源電圧以下の維持電圧Vhでも良好なESD保護を行う。

【解決手段】半導体集積回路のESD保護回路11は、電位端子とグランド電位間に、スナップバック動作を持つ第1のESD保護素子1としてのggMOSトランジスタと、スナップバック動作を持つESD保護素子1のスナップバック動作電圧Vt1に対して、低いブレークダウン電圧Vrを持ち、かつ高い破壊電圧Vt2を持つ第2のESD保護素子2としてのダイオードとが並列に接続されている。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

電源システム抑止方法ならびにその装置および構造

【課題】電源制御装置システム(25)の動作中に、システム(25)の動作を抑止する方法を提供する。

【解決手段】例えば、負荷(63)にシステム(25)の動作を抑止する条件を検出した場合、抑止トランジスタ(35)をオンにし、出力(48)を低に引き下げ、キャパシタ(49)を放電させる。キャパシタ(49)が初期電圧値より低い値まで放電されると、検出器40は、トランジスタ(44)をオンにし、装置(12)のトランジスタ(15)をオフにする。その結果、システム(25)は、出力(21)から供給される第2出力電流の供給を抑止し、第2出力電流よりはるかに小さい第1出力電流のみを出力(19)から供給する。制御装置(51)が動作しないため、システム(25)から負荷(63)への電圧供給が停止される。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

半導体装置

【課題】占有面積を増大させずに、電源投入開始後のチップ動作時にESD保護素子で発生するリーク電流を低減することができるESD保護素子を提供する。

【解決手段】電源ライン及び接地ラインを含む電子回路が形成された半導体基板10と、半導体基板10において電源ライン(Vdd)及び接地ライン(Vss)間に設けられ、サイリスタSCR及びサイリスタを駆動するトリガーダイオードTDを含む静電気放電保護素子とを有し、トリガーダイオードは、半導体基板10に形成されたアノード拡散層22と、アノード拡散層22から離間して半導体基板10に形成されたカソード拡散層21と、アノード拡散層22及びカソード拡散層21間において半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極17とを有し、外部電源に接続された外部端子(パッド電極27)がゲート電極17に電気的に接続されている構成とする。

(もっと読む)

1 - 20 / 184

[ Back to top ]