Fターム[5F082DA03]の内容

Fターム[5F082DA03]に分類される特許

1 - 20 / 117

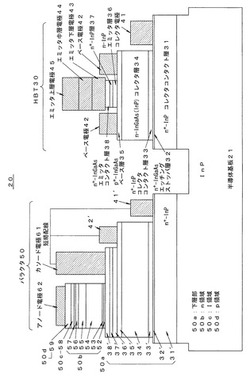

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の側壁側にサイドウォールを精度よく形成することが可能な半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】まず、SOI基板5の一方面側においてゲート電極34上及びゲート電極34の周囲の領域に第1絶縁膜40を形成する。次に、第1絶縁膜40上に積層させる構成で第1絶縁膜40とは材質の異なる第2絶縁膜42を形成する。そして、第1絶縁膜40及び第2絶縁膜42におけるゲート電極34の側壁34a側の部分を残しつつ、第2絶縁膜42よりも第1絶縁膜40のほうが、エッチング速度が遅くなるように第1絶縁膜40及び第2絶縁膜42を除去し、ゲート電極34の側壁34a側にサイドウォール45を形成する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタの耐圧低下や耐湿劣化を防ぐことができる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1上にベース電極4を形成する。ベース電極4を覆うようにレジスト膜5を形成する。レジスト膜5をマスクとした等方性エッチングにより、ベース電極4の周辺の半導体基板1を掘り込んでベースメサ溝6を形成する。ベース電極4上に絶縁膜7を形成する。絶縁膜7上に配線電極8を形成する。レジスト膜5の外周とベース電極4の外周との最小幅wは、ベースメサ溝6がベース電極4の下に入り込まないような値に設定されている。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体装置

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

増大した直線性および製造可能性を有するFETを含むBiFET

【課題】基板上に位置するBiFETにおいて、HBT性能の低下を引起すことなくFETの製造可能性増大を達成させる。

【解決手段】基板上に位置するBiFET100は、基板の上に位置するエミッタ層部分122を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分126をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFET106をさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分146はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に直接接して位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで性能向上が可能なBiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】n型の半導体基板1の表面から所定の深さに、コレクタ領域を構成するn型の不純物領域26を備える。当該不純物領域26の上方、かつ半導体基板1に形成されたシャロートレンチ分離14で挟まれた領域18にはp型のベース領域20を備える。ベース領域20には、n型の半導体膜からなるエミッタ電極が接触して設けられている。当該半導体装置は、不純物領域26がベース領域20下からシャロートレンチ分離14下まで延在し、当該シャロートレンチ分離14を貫通して不純物領域26に電気的に接続するコンタクトプラグ52を備える。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エミッタ電極の膜厚が均一であり、このために素子特性のばらつきが少ない特性が良好な半導体装置を提供する。

【解決手段】Si基板1上のN−hill層11と、N−hill層11を囲む素子分離領域であるシャロートレンチアイソレーション6に開口されたオープン領域21と、を備えたHCBT100を含む半導体装置において、オープン領域21上に面方位のないアモルファスSi膜30,31を形成する。アモルファスシリコン膜30、31を、N−hill層11がアモルファスシリコン膜30、31から露出する厚みにまでエッチングして電極とする。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】単一半導体基板上にHBTおよびFETのような異なる種類の複数デバイスを形成するに適した化合物半導体基板を提供する。

【解決手段】第1半導体110と、第1半導体上に形成された、電子捕獲中心または正孔捕獲中心を有するキャリアトラップ層130と、キャリアトラップ層上にエピタキシャル成長され、自由電子または自由正孔が移動するチャネルとして機能する第2半導体144と、第2半導体上にエピタキシャル成長したN型半導体/P型半導体/N型半導体で表される積層体、または前記第2半導体上にエピタキシャル成長したP型半導体/N型半導体/P型半導体で表される積層体を含む第3半導体160とを備える半導体基板。

(もっと読む)

半導体装置

【課題】製造後に電流増幅率hFE特性を変化させることができるバイポーラトランジスタを備えた半導体装置を提供する。

【解決手段】P型半導体層1に、N型拡散層からなるコレクタ3、P型拡散層からなるベース5、N電型拡散層からなるエミッタ7が形成されてバイポーラトランジスタが形成されている。そのバイポーラトランジスタはベース5上及びコレクタ3にゲート絶縁膜9を介してゲート電極11を備えている。コレクタ3にはコレクタ配線13が接続されている。ベース5にはベース配線15が接続されている。エミッタ7にはエミッタ配線17が接続されている。ゲート電極11にはゲート電極配線19が接続されている。配線13,15,17,19は互いに電気的に絶縁されている。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

1 - 20 / 117

[ Back to top ]