Fターム[5F083AD04]の内容

半導体メモリ (164,393) | DRAM (5,853) | 読出しトランジスタ (1,433) | 水平方向以外のチャネルを有するもの (541) | トレンチゲートトランジスタ(単孔にゲートを埋込むもの) (266)

Fターム[5F083AD04]に分類される特許

1 - 20 / 266

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

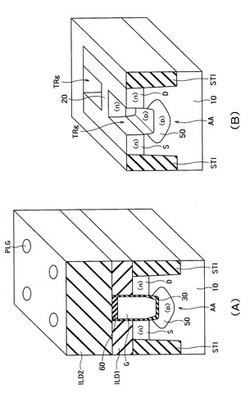

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電流―電圧特性の向上およびオン電流を増大することが可能で、高速動作に優れた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板12の主面に形成され、第1の方向に延在する複数の活性領域と、活性領域を区画する素子分離領域と、半導体基板12の主面に形成されたものであって、平面視して複数の活性領域に交差する方向に延在する複数のゲート溝と、ゲート溝のそれぞれに埋め込まれた複数のゲート電極22と、を備えた半導体装置であって、ゲート溝のそれぞれの底面には、第1の方向に延在すると共に、上面71aが半導体基板12の主面よりも低い位置に配置する一対の突起部71が形成されており、ゲート電極22は、ゲート絶縁膜21を介して突起部71の上面71aと内側面71bと外側面71cとを覆ってなる、ことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の埋め込みゲート型トランジスタが形成されたメモリセル領域と周辺回路領域を有する半導体装置の製造において、前記埋め込みゲート型トランジスタの半導体層とコンタクトプラグとの接触抵抗及び前記埋め込みゲート型トランジスタ毎の電流駆動特性のばらつきの増加を防ぐ。

【解決手段】半導体基板上に第1の半導体層と、前記第1の半導体層の下面と接する前記第1の半導体層よりも低い不純物濃度である第2の半導体層とを形成する工程と、前記第1の半導体層及び前記第2の半導体層から成る活性領域を少なくとも2つの領域に分ける溝内にゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板の主面を覆う層間絶縁膜を形成する工程と、前記層間絶縁膜を貫通して前記第1の半導体層の上面の一部を露出させるコンタクトホールに導電膜を埋め込んでコンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】RCATの電流駆動能力を向上させることが可能な半導体装置を提供する。

【解決手段】半導体基板11は、ゲート溝13を有している。拡散層12は、ゲート溝13の上部に対応する半導体基板11の表面領域に形成されている。ゲート絶縁膜14は、ゲート溝の壁面に形成されている。ゲート電極15は、ゲート溝13の内部及びゲート溝13の外部に形成されている。圧縮応力を有する膜16は、ゲート溝13の外部のゲート電極15の全面に形成されている。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接するトランジスタ間において、各々のゲート電極の電圧変化の影響が相互に及ばないようにする。

【解決手段】基板100内の素子分離領域220で囲まれた活性領域と、活性領域内に形成された埋め込みゲート電極410a、410bと、埋め込みゲート電極410a、410bの間に設けられ、かつ埋め込みゲート電極410a、410bの底部の深さまで形成された拡散層領域320を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ上の絶縁膜とキャパシタの形成されていない領域上の絶縁膜と平坦化する際に、キャパシタ上の絶縁膜を一部エッチング除去した後平坦化すると、両者の境界部に残る絶縁膜隆起部が剥がれてくぼみ等の欠陥が発生する。

【解決手段】境界部に残す絶縁膜の隆起部立ち上がり点から水平方向の距離をLr、エッチング量をHdとしたとき、アスペクト比Hd/Lrを0.6以下、好ましくは0.25以下とする。通常、Hdはキャパシタの形成されていない領域上の絶縁膜表面高さまでとし、Lrはキャパシタ高さの少なくとも4倍とする。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】埋込ワード線の高さにばらつきのない半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、複数の素子分離領域を形成すると共に、素子分離領域間に素子形成領域を形成する工程と、素子形成領域に交差する第1の方向に延在するゲート電極溝を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を介して第1導電膜を形成する工程と、ゲート電極溝内を埋め込むように第2導電膜を形成する工程と、第2導電膜上に平坦化膜を形成する工程と、第2導電膜が露出するように平坦化膜をエッチングして除去する第1のエッチング工程と、第2導電膜がゲート電極溝の下部に残留するように第2導電膜をエッチングする第2のエッチング工程と、第1導電膜が前記ゲート電極溝の下部に残留するように第1導電膜をエッチングする第3のエッチング工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】複数のサポート膜間における開口の位置ずれ発生を抑制できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に、第1の犠牲膜、第1のサポート膜、第2の犠牲膜及び第2のサポート膜を順次形成し、これらの膜を貫通するホールを形成し、ホールの内表面を覆い、かつ第2のサポート膜及び第1のサポート膜に接続される王冠型電極を形成し、王冠型電極と第2のサポート膜との接続を少なくとも一部分維持する第1のパターンで、第2のサポート膜に第1の開口を形成し、第1の開口を通じて第2の犠牲膜の一部又は全部を除去し、第1の開口を利用して第1のサポート膜に第2の開口を形成し、第2の開口を通じて第1の犠牲膜を全て除去する、ことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】アモルファスカーボン膜などの酸化によりパターン精度が劣化する材料からなるハードマスク膜上に保護膜とマスク膜の積層膜を形成し、マスク膜をダブルパターニング技術を用いてパターニングすると、保護膜も2回のエッチングに曝されて、保護膜としての機能が損なわれ、パターニングに使用する有機膜除去のアッシングの際に、ハードマスク膜が酸化されてパターン精度が劣化し、忠実なパターン転写ができなくなる。

【解決手段】マスク膜6の2回目のエッチングの際に、パターニングに用いる有機膜(反射防止膜7b、8b)をマスク膜6表面は露出するが、保護膜5表面は露出しないようにエッチングし、マスク膜6のみを選択的にパターニングすることで、その後の残存する有機膜のアッシング除去に際して、ハードマスク膜4を酸化から保護する保護膜5の機能を確保でき、パターン転写の忠実性を確保できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

1 - 20 / 266

[ Back to top ]