Fターム[5F083AD31]の内容

Fターム[5F083AD31]に分類される特許

1 - 20 / 109

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

エッチング方法、これに用いられるシリコンエッチング液、及び半導体基板製品の製造方法

【課題】多結晶シリコン及び/又はアモルファスシリコンについて、シリコン等を的確かつ高速に除去し、一方で残される電極部材等を損傷させずに維持することができるシリコンエッチング液及びこれを用いたエッチング方法、これを用いた半導体基板製品を提供する。

【解決手段】アニオン性基を有する炭素数3以上の化合物と硝酸とフッ化水素酸とを水性媒体中に含有するシリコンエッチング液を準備し、該シリコンエッチング液を多結晶シリコン及び/又はアモルファスシリコンからなるシリコン膜に適用して、キャパシタとなる凹凸形状を形成するエッチング方法。

(もっと読む)

メモリ装置

【課題】メモリセルの占有面積が小さいメモリ装置、また、メモリセルの占有面積が小さく、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】ビット線と、容量素子と、該ビット線上に設けられた溝部を有する第1の絶縁層と、一部が該溝部の底部で該ビット線と電気的に接続し、他の一部が該第1の絶縁層の上面で該容量素子の一方の電極と電気的に接する半導体層と、該半導体層と接する第2の絶縁層と、該第2の絶縁層と接するワード線と、を有する構成のメモリ装置とする。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは、ビット線をキャパシタとセルトランジスタの間に形成するため、構造が複雑であったり、回路の特性を犠牲にしたりする必要があり、集積化の面で大きな障害となっている。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極をセルトランジスタのドレインに接続する。また、セルトランジスタのソースは、ソース線に接続される。この結果、例えば、スタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線は、半導体基板上に形成された不純物領域や、ワード線に平行な配線を用いることができるので、構造が単純となる。

(もっと読む)

半導体装置

【課題】DRAM回路などのように容量を内蔵する半導体装置において、コンタクト容量およびコンタクト抵抗を増加させることなく、容量の容量値を増加させる。

【解決手段】セルコンタクトが形成されるセルコンタクト部にまで容量の形成場所を延長することで、容量値のさらなる増大が可能となる。なお、容量部、容量コンタクト部およびセルコンタクト部にまたがる容量の形成には、ALD法などによるスパッタ装置を用いることが好ましい。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したDRAMを提供する。

【解決手段】第1絶縁体101上にビット線102b、ビット線102b上に第2絶縁体103、第2絶縁体103上にストライプ状の第3絶縁体106a乃至106c等を形成し、第3絶縁体106bを覆って、半導体領域109bとゲート絶縁体110を形成する。ビット線102bと半導体領域109bは第1のコンタクトプラグ105a、105bで接続される。その後、導電性膜を形成し、これを異方性エッチングすることで、第3絶縁体106a乃至106cの側面にワード線111a乃至111dを形成し、第3絶縁体106bの頂部にキャパシタへ接続するための第2コンタクトプラグ115bを形成する。ワード線111b、111cを同期させることで、キャパシタに電荷を出入りさせる。このような構造でメモリセルの面積を4F2とできる。

(もっと読む)

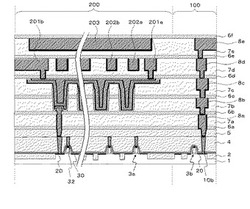

半導体メモリ装置

【課題】高度に集積化したDRAMを提供する。

【解決手段】基板201上にメモリセルアレイを駆動するための回路202を形成し、その上にビット線205を形成し、ビット線205上に半導体領域208とワード線210a、210b、キャパシタを形成する。ビット線が半導体領域208の下に位置し、ワード線210a、210b、キャパシタが半導体領域208の上に位置するため、ビット線205の配置の自由度が高まり、オープンビット線型のDRAMとすることで6F2以下、あるいはセルトランジスタの構造を特殊なものとすることで4F2以下とできる。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置及びその製造方法

【課題】低リーク電流、高容量の誘電体膜上に形成する窒化チタン電極の薄膜化を抑制する。

【解決手段】下部電極表面に形成された結晶質酸化ジルコニウムを含む誘電体膜と、誘電体膜表面に形成された窒化チタンを含む上部電極とで構成されるキャパシタを含む半導体装置であって、誘電体膜は、前記上部電極を構成する窒化チタンとの界面に非晶質膜を含む。

(もっと読む)

半導体メモリセルおよびその製造方法

【課題】ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセルの集積度を向上させながら、製造コストを低減できる半導体メモリセルおよびその製造方法を提供する。

【解決手段】ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタKKとして形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。

(もっと読む)

半導体装置の製造方法

【課題】高アスペクト比のホール内に、良好なステップカバレッジを有する均一な膜厚の窒化シリコン層を形成する。

【解決手段】ホールを形成後、1回の第1サイクルと、1回以上の第2サイクルを行う。第1サイクルでは、ホールの上部内壁上に2原子層の第1のシリコン層、ホールの下部内壁上に1原子層の第1のシリコン層を形成後、ホール上部のシリコン層の表面を1分子層の第1の酸化シリコン層とする。ホールの下部内壁上の第1のシリコン層に更に、1原子層の第2のシリコン層を形成後、窒化処理によりホールの内壁全面に第1の窒化シリコン層を形成する。第2サイクルでは、ホール上部の窒化シリコン層上に1分子層の第2の酸化シリコン層を形成後、ホール下部の第1の窒化シリコン層上に1原子層の第4のシリコン層を形成する。この後、窒化処理により、ホールの内壁全面に第2の窒化シリコン層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置10は、半導体基板1の表層に第一の方向に延在するように形成された複数の活性領域1aと、前記活性領域1aの表層から深さ方向に形成されたn型不純物拡散層15と、前記複数の活性領域1aを横切り第二の方向に延在するように形成された複数の埋め込みゲート用の溝部13a,bと、ゲート絶縁膜25a,bを介して前記活性領域1a上を跨ぐように前記埋め込みゲート用の溝部13a,bに埋め込まれたゲート電極31およびダミーゲート電極32とを構成すると共に、前記半導体基板1の面上において前記第二の方向に延在する複数のワード配線層と、を具備し、前記ダミーゲート電極32の上面32cが、前記n型不純物拡散層15と前記活性領域1aとの界面よりも下方に位置していることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】更なる微細化に対応した高集積度のDRAMを得ることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2の表層に、第1の方向Yに延在する第1の溝部3と、第2の方向Xに延在し且つ第1の溝部3よりも深くなる第2の溝部5と、第1の溝部3と第2の溝部5との交差部分において第2の溝部5よりも深くなる第3の溝部7と、第1の溝部3と第2の溝部5との間から突出されたピラー部8と、ピラー部8に形成された下部拡散層9、チャネル領域10及び上部拡散層11と、第2の溝部5の内側において第2の方向Xに延在するビット配線層と、第1の溝部3の内側においてピラー部8の側面を覆うゲート絶縁膜と、第1の溝部3の内側においてゲート絶縁膜を介してピラー部8の側面を横切るように第1の方向Yに延在するワード配線層とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】半導体装置の動作を安定化させつつ、面積効率の向上を図る。

【解決手段】半導体基板10に設けられ、メモリセルを構成する拡散層50、及びダミーセルを構成する拡散層52と、半導体基板10上に設けられた層間絶縁膜20、22と、層間絶縁膜22上に設けられ、拡散層50と重なる少なくとも1つの凹部32を有するシリンダー層絶縁膜24と、拡散層50上に設けられたコンタクトプラグ102と、拡散層52上に設けられたコンタクトプラグ104と、凹部32の側面及び底面上に設けられ、コンタクトプラグ102を介して拡散層52と接続する下部電極130と、下部電極130上、シリンダー層絶縁膜24上、及びコンタクトプラグ104上に設けられ、コンタクトプラグ104を介して拡散層52と接続する誘電体膜132と、誘電体膜132上に設けられた上部電極134と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】簡便な方法でキャパシタ容量の増大を図り、また、キャパシタと同層に形成されるコンタクトプラグの製造を容易とする。

【解決手段】メモリセル部の層間絶縁膜(10,20)にバリア膜とメタル膜の二層構造のコンタクトプラグをいったん形成し、その上に層間絶縁膜(21,22)を積層し、コンタクトプラグ上面を露出する開口を形成し、メタル膜を選択的に除去した後、残存するバリア膜と一体となったキャパシタの下部電極を形成する。周辺回路部では、上層配線31と下層配線6Bとを接続するコンタクトプラグを2段(41、42)とする。

(もっと読む)

半導体装置

【課題】ストレージキャパシタ9のストレージ電極9aの電位が変動しても、プレート電位供給線10の電位変化を抑制することができる半導体装置を提供する。

【解決手段】それぞれがトランジスタ8とストレージキャパシタ9を有する複数のメモリセルを備え、複数のメモリセルの各ストレージキャパシタ9は、プレート電位供給線10に共通に接続されている半導体装置であって、プレート電位供給線10と電源電位供給線11との間に容量素子12を設けたことを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】D−RAMのキャパシタを形成するシリンダのドライエッチ加工において、従来技術の製造方法ではアスペクト比が高いシリンダやコンタクトの形状がボーイング形状となり隣接するホール間ショートの問題やホール内に形成する電極成膜のカバレッジ異常などの問題が発生する。

【解決手段】本発明ではシリコン酸化膜4aにコンタクトホールを形成する際にボーイングが発生する部分にLow−k膜の炭化シリコン酸化膜5を挿入して積層構造とし、ドライエッチでシリコン酸化膜4aのエッチング速度に対し、炭化シリコン酸化膜5のエッチング速度が1/5〜1/10と遅い条件にすることでボーイング形状の抑制を可能にした。

(もっと読む)

1 - 20 / 109

[ Back to top ]