Fターム[5F083AD51]の内容

Fターム[5F083AD51]の下位に属するFターム

印加電圧(Vss、Vcc、Vcc/2以外) (2)

プレート電圧を供給する配線 (34)

プレート電極の形状 (174)

Fターム[5F083AD51]に分類される特許

1 - 8 / 8

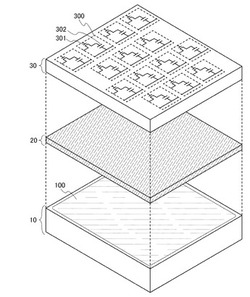

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】容量絶縁膜の絶縁性の劣化が生じにくく、かつ容量プレート電極の厚みが薄い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、互いに異なる平面面積を持つメモリセル部と補償容量部とを単一の基板上に備える。メモリセル部と補償容量部とは、同一構成の容量プレート電極を含む。容量プレート電極は、ボロンドープシリコンゲルマニウム膜と金属膜とを含む積層構造を有している。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】金属窒化膜に隣接する他の膜の特性を劣化させない温度範囲において、金属窒化膜中の塩素原子や酸素原子の残留量を低減し、金属窒化膜の耐酸化性を改善する。

【解決手段】自然酸化膜が形成され、塩素原子を含む窒化チタニウム膜が形成された基板を処理室内に搬入して基板支持部により支持する工程と、基板を基板支持部により加熱する工程と、窒素原子含有ガス及び水素原子含有ガスをガス供給部により処理室内に供給しつつ、処理室内をガス排気部により排気する工程と、処理室内に供給された窒素原子含有ガス及び水素原子含有ガスをプラズマ生成部により励起する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

ルテニウムを補助金属種と共に堆積させるための方法及び組成物

【課題】

当技術分野は、ルテニウム含有フィルムの蒸気相形成のための改善された組成物を求めている。

【解決手段】

ルテニウム堆積の速度及び程度をそのような補助金属種の不存在下でのルテニウムの堆積に比較して増大させる補助金属種と共にルテニウムを堆積させることを含む、蒸着プロセスでルテニウム含有フィルムを形成する方法。そのような方法を実施するために有用な実例となる前駆物質組成物は、ルテニウム前駆物質及びストロンチウム前駆物質を溶媒媒質中に含み、組成物中において、ルテニウム及びストロンチウムが互いに共堆積されるように、ルテニウム前駆物質及びストロンチウム前駆物質のうちの一方が他方の前駆物質の中心金属原子に配位する側鎖官能基を含む。

(もっと読む)

三元化合物の気相堆積方法

基板表面に3元化合物である窒化チタンアルミニウム材料を形成する方法に関し、プラズマ強化原子層堆積プロセスを用いて、基板をチタン前駆体ガスおよび窒素プラズマに暴露し、基板上に窒化チタンを形成し、前記窒化チタン層をプラズマに暴露して処理し、前記窒化チタン層上にアルミナ前駆体ガスを暴露して、気相堆積プロセスによってアルミニウム層を堆積し、前記プラズマ強化原子層堆積プロセスと、処理プロセスと、気相堆積プロセスと、を繰り返して、窒化チタン層とアルミニウム層とから窒化チタンアルミニウム層を形成することを特徴とする。 (もっと読む)

半導体記憶装置及びその製造方法

【課題】立体構造を持つ容量素子を有する半導体記憶装置において、上部電極に電位を与えるコンタクト部に高い歩留まりと高い信頼性とを得られるようにする。

【解決手段】半導体基板10の上に互いに間隔をおいて形成された第1のホール19a及び第2のホール19bを有する第3の層間絶縁膜19には、第1のホール19aの底面及び壁面上に下部電極が形成され、一方、第2のホールの底面及び壁面上並びに第2のホールにおけるメモリセル部Aの反対側の周辺部上にまで延びるように下部導電膜が形成されている。容量絶縁膜22は、第1のホール19a及び第2のホール19bを含め第3の層間絶縁膜19の上に形成されており、上部電極形成膜23は、容量絶縁膜22における第3の層間絶縁膜19上で且つ第2のホール19bの周辺部に形成された開口部22aを通して下部導電膜21Bと電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMキャパシタにおいて、上部電極内に発生する応力を低減することにより、容量絶縁膜の劣化を抑制する。

【解決手段】本発明の半導体装置は、第1の層間絶縁膜11内に設けられた複数の溝部12の表面を覆う下部電極13と、下部電極13の上を覆う容量絶縁膜14と、容量絶縁膜14を挟んで複数の下部電極の上方を覆う上部電極15とを備えている。上部電極15には、クラック17a、溝17bまたは凹部17cといった応力緩衝部17が設けられている。

(もっと読む)

1 - 8 / 8

[ Back to top ]