Fターム[5F083AD53]の内容

Fターム[5F083AD53]に分類される特許

1 - 20 / 34

半導体装置の製造方法

【課題】キャパシタとコンタクトパッド間のコンタクト抵抗の上昇を防ぎ、書き込み・読み出し不良を低減する、装置特性が優れた半導体装置を提供する。

【解決手段】タングステン膜8bを形成する工程と、タングステン膜8b上に窒化チタン膜からなる下部電極13を形成する工程と、酸化雰囲気下で窒化チタン膜に熱処理を行うことにより窒化チタン膜を酸化する工程と、下部電極13上に容量絶縁膜14を形成する工程と、容量絶縁膜14上に上部電極15を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を簡易に実現する、キャパシタを備える半導体装置を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10上に形成され、且つ、開口部OPを有する絶縁層20と、絶縁層20上に形成された第1キャパシタCAP1及び第2キャパシタCAP2と、を備える。絶縁層20の上面は、開口部OPの内壁面の少なくとも一部を含む第1上面と、第1上面と比較して半導体基板からより離れている第2上面と、を含む。第1キャパシタCAP1は、第1上面上に形成された第1下部電極51と、第1下部電極51上に誘電体膜60を介して形成された上部電極70と、を備える。第2キャパシタCAP2は、第2上面上に形成され第1下部電極51と電気的に分離された第2下部電極52と、第2下部電極52上に誘電体膜60を介して形成された上部電極70と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造工程の簡略化および製造時間短縮を目的とする、メモリセルと周辺回路を備える半導体装置と製造方法を提供する。

【解決手段】トランジスタ形成層30上に、内部に配線10bを備え、かつ、表面に容量パッド14a,14bを有する絶縁層32を形成する工程と、絶縁層32を層間絶縁膜16で覆い、層間絶縁膜16を貫通する第一のホール16aと、第一のホール16aよりも大きい直径を有する第二のホール16bおよび第三のホール16cを、それぞれメモリセル部と周辺回路部に同時に形成する工程と、各ホール内を覆う下部電極18と容量絶縁膜19と上部電極20と容量サポート21を形成することにより第一のホール16aを充填するとともに、第二のホール16bと第三のホール16c内側に空洞を形成する工程と、空洞内に、配線10bと容量パッド14bにそれぞれ接続するコンタクト16d,16eを形成する工程と、を具備している。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセスの工程数を少なくし得ると同時に低い接続抵抗を実現し得る構造を持つ半導体装置の製造方法を提供する。

【解決手段】この製造方法は、セルトランジスタの拡散領域206A,206C,206D,206Fに達する第1のコンタクトホールと、セルトランジスタの拡散領域206B,206Eに達するビット線コンタクトホールと、このビット線コンタクトホールに連通する配線溝とを第1の絶縁膜208Pに埋め込み形成する。また、これら第1のコンタクトホール、ビット線コンタクトホールおよび配線溝に導電性材料を埋め込むことでそれぞれ第1のコンタクトプラグ210A〜210Dとビット線コンタクト211B,211Fとを形成し、第1のコンタクトプラグ210A〜210Dを、第2の絶縁膜212に形成された開口部を介して、第3の絶縁膜214Pに形成されたキャパシタと電気的に接続する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】複数の容量部が接続された容量プレート上面とロジック部とで配線層の高さを同じにするメモリ混載の半導体装置、および製造方法を提供する。

【解決手段】半導体装置の製造方法は、ロジック部の第1領域3の第1層間層43、53に配線34を形成する工程と、配線形成後にメモリ部の第2領域2の第1層間層43、53における表面領域をエッチングする工程と、エッチングした領域に容量12用の複数のシリンダ開口部を形成する工程と、複数のシリンダ開口部に下部電極層12C、誘電体層12B及び共通上部電極12A、13を形成して、複数の容量部12を形成する工程とを具備する。複数の容量部12を形成する工程は、第1層間層43、53の上面と共通上部電極12A、13の上面とが略同一平面上になるように共通上部電極12A、13を形成する工程を備える。

(もっと読む)

半導体装置

【課題】回路を形成する領域を確保しつつ、十分な耐圧、容量を備えた容量素子を備える半導体装置を提供する。

【解決手段】半導体装置は、DRAMセルのキャパシタ上部電極19と、上部電極19の下方に形成されたキャパシタ下部電極17とを含む情報記憶部と、情報記憶部へのアクセスを制御するアクセストランジスタとを有するメモリセルと、アクセストランジスタに接続され、情報記憶部にデータの書き込み又は読み出しを行うビット線16と、アクセストランジスタのゲート電極に接続され、アクセストランジスタを制御するワード線と、キャパシタ上部電極19の上方に形成された第1金属配線21と同一層からなる上部電極23と、キャパシタ上部電極19と同一層の下部電極22とを有し、メモリセルが形成された領域外に形成された容量素子とを備える。

(もっと読む)

半導体装置

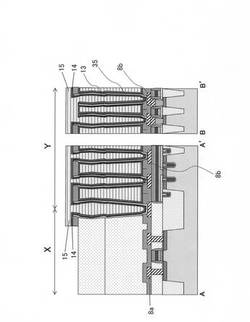

【課題】キャパシタを構成する下部電極の自立安定性が十分に高められる半導体装置を提供する。

【解決手段】キャパシタ下地層2上に、キャパシタを構成する筒状の下部電極10と、下部電極10の外壁部に、外壁部から延在して形成されたフィン17とサポート膜6を有する。フィン17は下部電極10の長手方向一部にだけ形成されている。さらに、フィン17を含む下部電極10の上端はサポート膜6に接続されており、サポート膜6からの下部電極10の剥がれが防止される。フィン17を含む下部電極10上に、容量膜、上部電極、容量プレートの埋込みサポート膜、および容量プレートを成膜する。フィン17とサポート膜6とを接続させることにより、サポート膜6と下部電極10の接続面積を増大させることができる。

(もっと読む)

メモリセルアレイ

【課題】小型化、高密度化が可能であって、かつ、既存の半導体製造技術と整合性の良いメモリセルアレイを提供する。

【解決手段】複数のメモリセル100をアレイ状に配置したメモリセルアレイ10において、メモリセル100はMOSトランジスタ110とMOSトランジスタ110の一方の拡散層112aに接続する第1電極113を有するコンタクトホール101a内に形成されたナノギャップ素子120とを有し、ナノギャップ素子120は第1導電体121と第1導電体121の上方に設けられた第2導電体122との間への所定電圧の印加により抵抗値の変化現象が生じるナノメートルオーダーの間隙を有し、ワード線WLはMOSトランジスタ110のゲート領域115と接続し、第1ビット線BL1はMOSトランジスタ110の他方の拡散層112bに接続された第2電極114と接続し、第2ビット線BL2は第2導電体122と接続していることを特徴とする。

(もっと読む)

1 - 20 / 34

[ Back to top ]