Fターム[5F083BS10]の内容

Fターム[5F083BS10]の下位に属するFターム

Fターム[5F083BS10]に分類される特許

1 - 20 / 26

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置

を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以

下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶

縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下

の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半

導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の表面に導入された不純物を、前記表面の浅い領域に高精度かつ高濃度で分布させ、不純物が半導体基板の深い領域に拡散することを防ぐことで、半導体装置の歩留まりおよび性能を向上させ、装置の微細化を容易にする。

【解決手段】N型MISトランジスタにおいて、半導体基板300に打ち込まれた炭素が、同じ領域に打ち込まれたホウ素を引き寄せる性質を利用し、ホウ素をN型の不純物として注入したハロー領域306に炭素を共注入して炭素注入層307を形成する。これにより、ホウ素が増速拡散することを防ぎ、ハロー領域306を高い精度で形成することを可能とすることで、微細化された半導体素子の短チャネル効果の発生を抑制する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域SD1及びp+型半導体領域SD2を形成してから、半導体基板1上にNi−Pt合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域SD1及びp+型半導体領域SD2とを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層13aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で、かつ、金属シリサイド層13a上に合金膜の未反応部分が残存するように、第1の熱処理を行う。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層13aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層13bを形成する。第2の熱処理の熱処理温度は580℃以上で、800℃以下とする。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

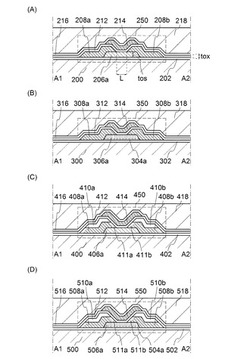

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体装置

【課題】オフ電流が小さい薄膜トランジスタによって問題なく動作することが可能な記憶素子を含む記憶装置を提供することを課題とする。

【解決手段】酸化物半導体層を有する薄膜トランジスタが少なくとも一つ設けられた記憶素子を、マトリクス状に配置した記憶装置を提供する。酸化物半導体層を有する薄膜トランジスタは、電界効果移動度が高く、且つオフ電流を小さくできるため、問題なく良好に動作させることができる。また、消費電力を低くすることもできる。このような記憶装置は、例えば酸化物半導体層を有する薄膜トランジスタが表示装置の画素に設けられている場合に、記憶装置を同一基板上に形成することができるため、特に有効である。

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供する。

【解決手段】第1の島状半導体層137の周囲上に少なくとも一部に接して第1のゲート絶縁膜187が存在し、第1のゲート絶縁膜187に第1のゲート電極178の一面が接し、第1のゲート電極178の他面に第2のゲート絶縁膜187が接し、第2のゲート絶縁膜187に少なくとも第2の半導体層141が接して、第1の島状半導体層137の上部に配置された第1の第1導電型高濃度半導体層161と、第1の島状半導体層137の下部に配置された第2の第1導電型高濃度半導体層162と、第2の半導体層141の上部に配置された第1の第2導電型高濃度半導体層154と、第2の半導体層141の下部に配置された第2の第2導電型高濃度半導体層156と、を有するインバータを用いてSRAMを形成する。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのしきい値のばらつきを抑制する。

【解決手段】半導体基板1に素子分離領域2を形成し、MISFETのしきい値調整用のチャネルドープイオン注入を行なってから、ゲート絶縁膜5a,5bおよびゲート電極GE1,GE2を形成する。それから、イオン注入によりエクステンション領域7a,7bおよびハロー領域8a,8bを形成し、更に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することにより拡散防止領域10a,10bを形成する。その後、ゲート電極GE1,GE2の側壁上にサイドウォールSWを形成してから、イオン注入により、ソース・ドレイン用のn+型半導体領域11aおよびp+型半導体領域11bを形成して、nチャネル型MISFETおよびpチャネル型MISFETが形成される。

(もっと読む)

半導体デバイスとその製造方法、および集積回路

【課題】 バンド端を制御されたVtオフセット・デバイスを提供する。

【解決手段】 バンド端を制御されたVtオフセット・デバイス、バンド端を制御されたVtオフセット・デバイスの設計構造体、及びその構造体の製造方法を開示する。構造体は、第1のバンド構造及び第1の型をもたらす第1の原子比の第1の化合物半導体のチャネルを有する第1のFETを含む。この構造体はさらに、第2のバンド構造及び第1の型をもたらす第2の原子比の第2の化合物半導体のチャネルを有する第2のFETを含む。第1の化合物半導体は第2の化合物半導体とは異なり、その結果、第1のFETは第2のバンド構造とは異なる第1のバンド構造を有し、第2のFETの閾値電圧とは異なる閾値電圧を生じる。

(もっと読む)

半導体装置

【課題】微細化が進んだ半導体装置の短チャネル効果を防ぎ、特性を向上させることができる半導体装置の提供を課題とする。

【解決手段】単結晶シリコン基板上に形成された酸化膜と、酸化膜上に形成された単結晶シリコン層と、単結晶シリコン層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極を有する半導体装置であって、単結晶シリコン層はチャネル形成領域、ソース領域、ドレイン領域を有し、チャネル形成領域には、ソース領域、ドレイン領域とは逆の導電型の不純物元素が添加され、チャネル形成領域の不純物元素が添加された領域は、上面から見て主軸がソース領域からドレイン領域にかけて伸びるフィッシュボーン形状を有し、フィッシュボーン形状は単結晶シリコン層の表面から底部にかけて形成され、チャネル形成領域の不純物元素が添加された領域は、空乏層を抑止する機能を有することを特徴としている半導体装置を提供する。

(もっと読む)

垂直型トランジスタの回路接続アーキテクチャ

【課題】半導体層の中または半導体層に隣接した領域の間を接続するための構造を提供する。

【解決手段】半導体デバイス204は半導体材料の第1の層112と、第1の層の中に形成された第1のソース/ドレイン領域116を有する第1の電界効果トランジスタ180とを含み、チャネル領域160は第1の層の上に形成され、関連する第2のソース/ドレイン領域164はチャネル領域の上に形成される。このデバイスはまた、第1の層114の中に形成された第1のソース/ドレイン領域118を有する第2の電界効果トランジスタ190を含み、チャネル領域162は第1の層の上に形成され、関連する第2のソース/ドレイン領域166はチャネル領域の上に形成される。金属を含む導電層120は、各トランジスタの第1のソース/ドレイン領域の間に置かれて、1つの第1のソース/ドレイン領域から他の第1のソース/ドレイン領域に電流を導く。

(もっと読む)

同一の能動領域内に形成されるトランジスタにおいて能動領域内に局所的に埋め込み歪誘起半導体材質を設けることによる駆動電流調節

【解決手段】

共通の能動領域内に少なくとも1つの埋め込み半導体合金を設けることによって得られる異なる歪レベルに基いて、その能動領域内に形成されるプルダウントランジスタ及びパストランジスタの駆動電流能力を調節することができ、それにより能動領域の単純化された全体的な幾何学的構造を提供することができる。従って、能動領域の単純化された構造を伴う最小のチャネル長に基きスタティックRAMセルを形成することができ、プルダウン及びパストランジスタに対する駆動電流の比を調節するためにトランジスタ幅の明白な変化が従来的に用いられている洗練されたデバイスで観察され得るような顕著な歩留まり低下を回避することができる。

(もっと読む)

半導体装置

【課題】 動作マージンを確保しつつ、微細化を可能とするSRAMセルを提供する。

【解決手段】

SRAMセルが、それぞれ、NMOSドライバとPMOSロードとが接続された第1、第2のインバータを含み、それぞれのインバータの内部ノードが他方のインバータの入力に接続されたフリップフロップ回路と、第1、第2のビット線と、第1、第2のインバータの内部ノードと第1、第2のビット線との間に接続された第1、第2のNMOSトランスファトランジスタであって、それぞれ、絶縁ゲート電極構造の両側に形成された第1、第2のn型ソース/ドレイン領域と、を含み、2つの第1のn型ソース/ドレイン領域が第1、第2のインバータの内部ノードに接続され、2つの第2のn型ソース/ドレイン領域が第1、第2のビット線に接続された第1、第2のNMOSトランスファトランジスタと、第1のn型ソース/ドレイン領域を覆って形成された圧縮応力膜と、第2のn型ソース/ドレイン領域を覆って形成された引張応力膜と、を有する。

(もっと読む)

半導体装置

【課題】CPU搭載無線タグのメモリ内のデータの書き換えを可能にした上で、CPUシステムを高速化し、無線タグの通信性能の向上を行う。

【解決手段】CPUが搭載されている無線タグにRFバッテリー付きのSRAMを搭載することで、CPUシステムの高速化による通信性能を向上させる。また、CPU搭載無線タグのメモリ内のデータの書き換えを可能にした。RFバッテリーは、アンテナ回路と、電源部と、蓄電装置と、を有する。SRAMとRFバッテリーとを組み合わせることで、SRAMに不揮発性メモリとしての機能を持たせる。

(もっと読む)

1 - 20 / 26

[ Back to top ]