Fターム[5F083BS17]の内容

半導体メモリ (164,393) | SRAM (3,190) | 駆動トランジスタ (792) | 構造 (444) | ソース/ドレイン構造 (210) | LDD(Lightly Doped Drain) (149)

Fターム[5F083BS17]に分類される特許

1 - 20 / 149

半導体装置

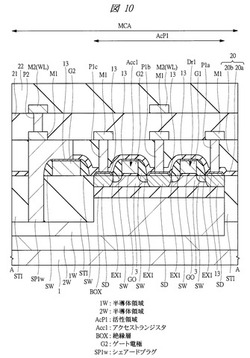

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1が配置される活性領域AcP1の下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wの底部および側部が、n型の半導体領域2Wと接するように配置し、p型の半導体領域1Wをn型の半導体領域2Wでpn分離し、アクセストランジスタAcc1のゲート電極G2とp型の半導体領域1Wを接続する。そして、この接続は、アクセストランジスタAcc1のゲート電極G2の上部からp型の半導体領域1Wの上部まで延在する一体の導電性膜であるシェアードプラグSP1wによりなされる。これにより、アクセストランジスタAcc1がオン状態の場合において、バックゲートであるp型の半導体領域1Wの電位が同時に高くなり、トランジスタのオン電流を大きくできる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置

【課題】低電圧動作が可能なSRAMをそのセル面積の増加を抑えて実現する。

【解決手段】第1方向Sに並ぶP型ウェル領域20、N型ウェル領域30、P型ウェル領域40に、第2方向Tに隣接するメモリセル1aが形成される。各メモリセル1aは、P型ウェル領域20,40に形成されたトランスファトランジスタTf1,Tf2及びドライバトランジスタDr1,Dr2、N型ウェル領域30形成されたロードトランジスタLo1,Lo2を備える。SRAM1では、第2方向Tに隣接するメモリセル1aの、互いのトランスファトランジスタTf1のゲート電極がワード線WL1に、互いのトランスファトランジスタTf2のゲート電極がワード線WL2に、それぞれ電気的に接続される。ワード線WL1はP型ウェル領域20に、ワード線WL2はP型ウェル領域40に、それぞれ電気的に接続される。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

半導体装置

【課題】その特性の向上を図ることができるSRAMのセルレイアウトを提供する。

【解決手段】第1トランジスタ(TND1)および第5トランジスタ(TNA1)が配置される一体の第1活性領域(AcP1)と、第1活性領域(AcP1)と分離され、第2トランジスタ(TND2)が配置される第2活性領域(AcP2)と、第3トランジスタ(TND3)および第6トランジスタ(TNA2)が配置される一体の第3活性領域(AcP3)と、第3活性領域(AcP3)と分離され、第4トランジスタ(TND4)が配置される第4活性領域(AcP4)と、を有するようSRAMを構成する。ドライバトランジスタを分割(TND1とTND2、TND3とTND4)し、異なる活性領域(AcP2とAcP1、AcP4とAcP3)上に配置する。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

記憶装置及び半導体装置

【課題】消費電力を抑えることができる記憶装置を提供する。

【解決手段】第1クロック信号に従って、データを含む信号の電位の極性を反転させることで、出力電位を生成する第1論理素子と、第1論理素子が生成する出力電位を保持する第2論理素子及び第3論理素子と、トランジスタを用いたスイッチング素子と、第2論理素子及び第3論理素子において保持される第1論理素子の出力電位が、スイッチング素子を介して与えられることで、データを記憶する容量素子と、を有し、第2論理素子は、第1クロック信号とは異なる系統の第2クロック信号に従って、第3論理素子の出力電位の極性を反転させることで、第2論理素子の出力電位を生成し、第3論理素子は、第2論理素子の出力電位の極性を反転させることで、第3論理素子の出力電位を生成する記憶装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルにおける配線を確実に形成することがきて、電気的な接続が良好に行われる半導体装置を提供する。

【解決手段】半導体装置におけるSRAMのメモリセルでは、アクセストランジスタT1のゲート配線部GHA1に電気的に接続されるコンタクトプラグCPS1に対して、ワード線としての第3配線M32に電気的に接続されることになるヴィアVS1が直接接続されている。また、アクセストランジスタT2のゲート配線部GHA2に電気的に接続されるコンタクトプラグCPS2に対して、ワード線としての第3配線M32に電気的に接続されることになるヴィアVS2が直接接続されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域SD1及びp+型半導体領域SD2を形成してから、半導体基板1上にNi−Pt合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域SD1及びp+型半導体領域SD2とを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層13aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で、かつ、金属シリサイド層13a上に合金膜の未反応部分が残存するように、第1の熱処理を行う。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層13aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層13bを形成する。第2の熱処理の熱処理温度は580℃以上で、800℃以下とする。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置の製造方法を提供する。

【解決手段】ゲート配線16aを形成するのと同時に形成された位置合わせマーク16fに対して位置合わせして、コンタクトホールの第1の部分パターン61a1をゲート配線の一部と重なり合うようにフォトレジスト膜に露光する工程と、活性領域11bを形成するのと同時に形成された位置合わせマーク11fに対して位置合わせして、コンタクトホールの第2の部分パターン61a2を活性領域の一部と重なり合うようにフォトレジスト膜に露光する工程と、フォトレジスト膜を現像し、第1の部分パターンと第2の部分パターンとが露光された箇所に開口部を形成する工程と、フォトレジスト膜をマスクとして絶縁膜をエッチングし、ゲート配線とソース/ドレイン拡散層20とに達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体素子および作製方法

【課題】ソフトエラー率を有意に低下させる半導体素子およびその作製方法に関する。

【解決手段】半導体基板(100)には、第1の型の不純物でドープされた第1ウェル領域(104)の下に第1の型の第1ドープ領域(102)がある。第1ウェル領域は、第1ドープ領域と電気的に接続されている。第1ウェル領域と第1ドープ領域(102)との間に分離領域(206)を形成する。分離領域は第2ウェル領域と電気接続されている。分離領域および第2ウェル領域は、第1の不純物型と反対の型の第2の不純物型でドープされている。前記方法はさらに、第1ウェル領域内および分離領域下に第2ドープ領域を形成する工程をさらに有し得る。第1の型の不純物を有する第3ドープ領域を、分離領域の上に形成することができる。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクトの接触不良を防止して、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】高密度版回路における電界効果トランジスタTr3のゲート電極G3と電界効果トランジスタTr4のゲート電極G4とのピッチは、高速版回路における電界効果トランジスタTr1のゲート電極G1と電界効果トランジスタTr2のゲート電極G2のピッチよりも小さいが、シェアードコンタクトホールSCが達する部分のゲート電極G3に切欠を設けることにより、シェアードコンタクトホールSCと不純物領域S/Dとの接触面積を広くする。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタの特性ばらつきを増大させることなく、面積が縮小可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1における第1の素子分離領域2aに囲まれた第1の活性領域1aと、第1の活性領域上に順次形成された第1のゲート絶縁膜6a、第1のゲート電極9aとを有する第1のMISトランジスタと34と、半導体基板1における第2の素子分離領域2bに囲まれた第2の活性領域1bと、第2の活性領域上に順次形成された第2のゲート絶縁膜6b、第2のゲート電極9bとを有する第2のMISトランジスタ32とを備える。第1のゲート電極9aは、第1の活性領域1aの上面上だけでなく側面上に第1のゲート絶縁膜6aを介して形成されており、第2のゲート電極9bは、第2の活性領域1bの上面上に形成されており、側面上には形成されない。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度で素子特性に優れた、SRAMを備えた半導体装置を提供する。

【解決手段】一対の駆動トランジスタと一対の負荷トランジスタと一対のアクセストランジスタを備えたSRAMセル単位を有する半導体装置であって、前記トランジスタはそれぞれ、基体平面に対して上方に突起した半導体層と、この半導体層を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体層の間に介在するゲート絶縁膜と、前記半導体層に設けられた一対のソース/ドレイン領域を有し、前記駆動トランジスタはそれぞれ、前記負荷トランジスタ及び前記アクセストランジスタの少なくとも一方の各トランジスタのチャネル幅より広いチャネル幅を有する半導体装置。

(もっと読む)

1 - 20 / 149

[ Back to top ]