Fターム[5F083BS26]の内容

Fターム[5F083BS26]の下位に属するFターム

PMOSトランジスタ (630)

TFT (117)

抵抗素子 (33)

寄生容量 (32)

寄生ダイオード

Fターム[5F083BS26]に分類される特許

21 - 40 / 73

半導体装置の製造方法及び半導体装置

【課題】半導体装置が備えるnMOSトランジスタ及びpMOSトランジスタの形成面積を縮小する。

【解決手段】半導体装置の製造方法は、基板上に環状の突起部を形成する工程と、環状の突起部に第1のn型チャネル領域を形成する工程と、環状の突起部に第1のp型チャネル領域を形成する工程と、環状の突起部に形成された第1のn型チャネル領域及び第1のp型チャネル領域を跨ぐ第1のゲート電極を形成することにより、第1のnMOSトランジスタ及び第1のpMOSトランジスタを形成する工程と、を備える。

(もっと読む)

半導体装置、電気光学装置、電子機器

【課題】ある応力がかかっても回路全体としての動作特性が変化しない薄膜の半導体素子を実現し、これによって、動作マージンが広く大型化が容易なフレキシブルな半導体装置、電気光学装置、電子機器を提供する。

【解決手段】本発明の半導体装置は、基板100上に薄膜トランジスタ8を有し、この薄膜トランジスタ8は、基板100の湾曲に対してチャネル内のキャリアの移動度が相補的に変化する第1のチャネル領域1cおよび第2のチャネル領域1cを有している。

(もっと読む)

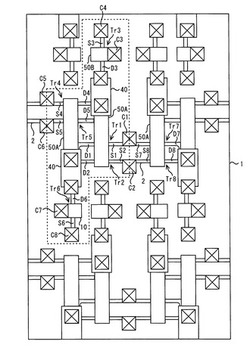

半導体記憶装置

【課題】縦型トランジスタSGTで構成されたCMOS型6T−SRAMにおいて、小さいSRAMセル面積と安定した動作マージンを実現する。

【解決手段】6個のMOSトランジスタを用いて構成されたスタティック型メモリセルにおいて、前記メモリセルを構成するMOSトランジスタは、基板上に形成され、ドレイン、ゲート、ソースが垂直方向に配置され、ゲートが柱状半導体層を取り囲む構造を有し、前記基板は第1の導電型を持つ第1の活性領域と第2の導電型を持つ第2の活性領域からなり、それらが基板表面に形成されたシリサイド層を通して互いに接続されることにより小さい面積のSRAMセルを実現する。また、基板上に配置される第1のウェルと同一の導電型を持つドレイン拡散層のそれぞれを第1のウェルと反対の導電型を持ち、第1のウェルより浅い第2のウェル及び第3のウェルで囲むことにより、基板へのリークを抑制する。

(もっと読む)

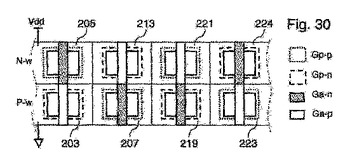

明白に異なる閾値電圧を有するトランジスタを持つSOIから製造する集積回路

本発明は、埋め込まれた絶縁材料面によって半導体基板層から隔てられた活性半導体層を含む集積回路に関する。この集積回路は、同じ型の第1および第2のトランジスタ(205、213)と、第1および第2のトランジスタの真下に配置された第1および第2の接地面とを有し、第1のトランジスタの接地面のドーピングは、第1のトランジスタのソースのドーピングと反対のドーピングであり、第1の閾値電圧を有する。第2のトランジスタの接地面のドーピングは、第2のトランジスタのソースのドーピングと同一のドーピングであり、第2の閾値電圧を有する。第1の閾値電圧は、第1のトランジスタのソースと接地面との間に印加される電位差に依存し、第2の閾値電圧は、第2のトランジスタのソースと接地面との間に印加される電位差に依存する。  (もっと読む)

(もっと読む)

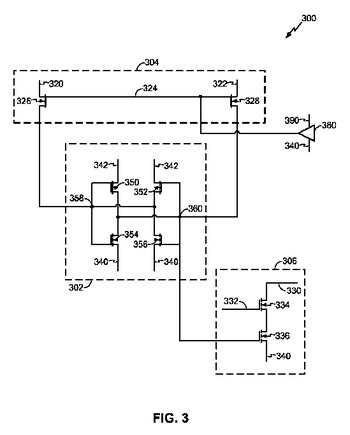

非プレーナ型トランジスタを用いた半導体装置および製造方法

【課題】より速い駆動電流およびより小さな短チャネル効果を備え、微細化されたスタティック・ランダム・アクセス・メモリ・セルを提供する。

【解決手段】スタティック・ランダム・アクセス・メモリ・セル300は、半導体基板上の1つ以上のフィンを備える2つの非プレーナ型パスゲート・トランジスタを備える。2つの非プレーナ型プルアップ・トランジスタは、半導体基板上の1つ以上のフィンを備える。2つの非プレーナ型プルダウン・トランジスタは、半導体基板上の1つ以上のフィンを備える。半導体基板上の2つのアシスト・バー314、316は、非プレーナ型プルアップ・トランジスタのフィンの一部と非プレーナ型プルダウン・トランジスタのフィンの一部とを電気的に接続する。

(もっと読む)

デュアル技術トランジスタを用いた低リーク高性能スタティックランダムアクセスメモリセル

メモリセルは、記憶素子、記憶素子に結合した書込み回路、および記憶素子に結合した読出し回路を具備する。記憶素子の少なくとも一部、および書込み回路の少なくとも一部は、厚い機能性ゲート酸化膜を用いて作られており、読出し回路の少なくとも一部は、薄い機能性ゲート酸化膜を用いて作られている。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧の絶対値が互いに異なる複数のMISトランジスタが用いられる場合において、しきい値電圧の絶対値が大きい方のMISトランジスタの駆動電流の低下を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】第2のnMISトランジスタT2nのしきい値電圧は、第1のnMISトランジスタT1nのしきい値電圧よりも大きく、第2のnMISトランジスタT2nが有する第2のnMIS高誘電率膜H2nにおけるランタン原子濃度およびマグネシウム原子濃度の和は、第1のnMISトランジスタT1nが有する第1のnMIS高誘電率膜H1nにおけるランタン原子濃度およびマグネシウム原子濃度の和よりも小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧のばらつきが小さい記憶素子部と、低消費電力で高速な論理素子部を有する半導体装置を可能にする。

【解決手段】記憶素子部12と論理素子部13とに素子分離領域14で分離された半導体層11の記憶素子部12の第1面S1側に第1ゲート電極23を有する第1電界効果トランジスタ21と、記憶素子部12の第2面S2側に第2ゲート電極33を有し、第1電界効果トランジスタ21とソース・ドレイン領域を共通とする第2電界効果トランジスタ31と、論理素子部13の第1面S1側に第3ゲート電極43を有する第3電界効果トランジスタ41と、第1面S1側に形成された第1絶縁膜51と、第2面S2側に形成された第2絶縁膜61を有し、第1、第2電界効果トランジスタ21、31は完全空乏型の電界効果トランジスタであり、第1、第2ゲート電極23、33は電気的に接続されている。

(もっと読む)

同軸のトランジスタ構造

【課題】 本発明は基板上での同軸トランジスタを開示する。

【解決手段】同軸構造のMOSFETであって、チップ或いは基板(Wafer Bonding)を積層し、軸心貫通孔により貫通し接続してより高い集積度及びラッチ効果のない同軸全対称のCMOSFETの集積回路を形成することができる。

(もっと読む)

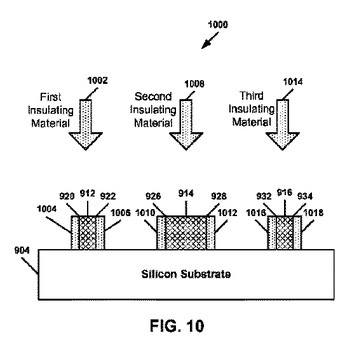

フィン電界効果トランジスタ(フィンFET)デバイスの製造方法

フィン電界効果トランジスタ(フィンFET)を用いた半導体の製造方法が開示される。特定の実施形態の方法は、第一の幅によって離隔された第一の側壁及び第二の側壁を有する第一のダミー構造体をシリコン基板上に堆積させるステップを含む。また、本方法は、第一のダミー構造体を堆積させるのと同時に第二のダミー構造体をシリコン基板上に堆積させるステップも含む。第二のダミー構造体は、第二の幅によって離隔された第三の側壁及び第四の側壁を有する。第二の幅は第一の幅よりも実質的に大きい。第一のダミー構造体を用いて略第一の幅によって離隔された第一の対のフィンを形成する。第二のダミー構造体を用いて略第二の幅によって離隔された第二の対のフィンを形成する。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】小型で動作信頼性の高い半導体記憶装置を提供することを目的とする。

【解決手段】第1、第2のインバータをクロスカップル接続させて形成されるインバータ対と、フロントゲートとバックゲートを有し前記バックゲートが前記第1のインバータの出力端子と前記第2のインバータの入力端子が接続する第1のノードに接続される第1のトランスファートランジスタと、前記フロントゲートと前記バックゲートを有し前記バックゲートが前記第2のインバータの出力端子と前記第1のインバータの入力端子が接続する第2のノードに接続される第2のトランスファートランジスタと、前記第2のノードにゲートが接続されるドライバトランジスタと、前記フロントゲートと前記バックゲートを有し前記バックゲートが前記第2のノードに接続され、電流経路の一端を前記ドライバトランジスタの電流経路一端に接続される読み出しトランジスタとを備える。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

ゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セルを製造するための方法

【解決手段】

ゲート型横型サイリスタベースメモリデバイス(gltram)を製造するための方法が提供される。半導体層(406)内の第1の伝導性タイプの第1、第2、第3及び第4のウエル領域(463,471,486,493)を含む半導体層(406)が設けられる。第1のゲート構造(465/408)は第1のウエル領域(463)上にあり、第2のゲート構造(475/408)は第2のウエル領域(471)上にあり、第3のゲート構造(485/408)は第3のウエル領域(486)上にあり且つ第2のゲート構造(475/408)と一体であり、第4のゲート構造(495/408)は第4のウエル領域(493)上に配置される。第1のゲート構造(465/408)の第1の側壁(414)及び第2乃至第4のゲート構造(475/408,485/408,495/408)の側壁(412,413,416,417,418,419)に隣接して側壁スペーサ(469)が形成される。また、第1のウエル領域(463)の部分(468)及び第1のゲート構造(465/408)の部分を覆う絶縁スペーサブロック(467)が形成される。絶縁スペーサブロック(467)は第1のゲート構造(465/408)の第2の側壁(415)に隣接する。第1のゲート構造(465/408)に隣接して第1のソース領域(472)が形成され、第1及び第2のゲート構造(465/408,475/408)の間に共通ドレイン/カソード領域(474/464)が形成され、第3のゲート構造(485/408)に隣接して第2のソース領域(482)が形成され、第3及び第4のゲート構造(485/408,495/408)の間に共通ドレイン/ソース領域(484/492)が形成され、第4のゲート構造(495/408)に隣接してドレイン領域(494)が形成される。第1のゲート構造(465/408)に隣接する絶縁スペーサブロック(467)の下で第1のウエル領域(463)内に延在する第1のベース領域(468)が形成され、第1のベース領域(468)に隣接する第1のウエル領域(463)内に延在するアノード領域(466)が第1のウエル領域(463)内に形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細で精度が高く、歩留まりが向上した半導体装置を提供する。

【解決手段】半導体装置は、第1トランジスタ2と第2トランジスタ5とを具備する。第1トランジスタ2は、半導体基板100上に第1ゲート絶縁膜51を介して形成された第1ゲート電極21と第1ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第2トランジスタ5は、半導体基板100上に第2ゲート絶縁膜51を介して形成された第2ゲート電極22と第2ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第1ゲート電極21及び第2ゲート電極22は、第1共通ソース・ドレイン領域30のコンタクトである第1ノード電極41の両側壁に設けられている。

(もっと読む)

半導体装置

【課題】ラッチアップの発生を防止しつつ、構造の微細化が可能な半導体装置を提供する。

【解決手段】相補型電界効果型トランジスタを含む半導体装置において、寄生的に形成されるバイポーラトランジスタのエミッタ電極となるp型不純物拡散領域5aと、電源供給線14と電気的に接続されているn型不純物拡散領域3とを、n型不純物を有する高融点金属シリサイドからなる接続配線40により接続する。

(もっと読む)

半導体装置、およびその製造方法

【課題】隣接するゲート電極間の距離が小さい場合であっても、応力膜によりチャネル領域に効果的に応力を発生させて電荷移動度を向上させることのできる半導体装置、およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、素子分離領域を有する半導体基板と、前記半導体基板上に各々ゲート絶縁膜を介して略並列に形成された複数のゲート電極と、前記半導体基板内の前記複数のゲート電極下の領域に各々形成された複数のチャネル領域と、前記半導体基板内の前記複数のチャネル領域を挟んだ領域に形成されたソース・ドレイン領域と、前記半導体基板および前記複数のゲート電極上を覆うように形成された第1の応力膜と、前記複数のゲート電極間の領域に形成された空隙内の少なくとも一部に形成された第2の応力膜と、を有する。

(もっと読む)

半導体装置

【課題】複数のトランジスタにより構成されるSRAMセルを有し、SRAMセル内の素子領域の幅や形状が略均一な半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成された所定の方向に長さ方向を有する素子領域と、前記素子領域内にそれぞれソース・ドレイン領域および前記所定の方向に略平行なチャネル方向を有するチャネル領域を有し、前記所定の方向と略垂直な方向にそれぞれゲート電極を有する複数のトランジスタと、それぞれが複数の前記トランジスタを含み、アレイ配置された複数のSRAMセルと、前記所定の方向に略垂直な方向に隣接する前記SRAMセル同士の最外側の前記素子領域の間に形成された、前記所定方向に略平行な長さ方向を有し、前記素子領域と同じ材料からなるダミー領域と、を備える。

(もっと読む)

半導体装置の製造方法および半導体記憶装置の製造方法

【課題】セルサイズを縮小することのできるSRAMを提供する。

【解決手段】駆動MISFETおよび転送MISFETの上部には、縦型MISFET

が形成されている。縦型MISFETは、下部半導体層(ドレイン)57、中間半導体層

58、上部半導体層(ソース)59を積層した四角柱状の積層体(P1、P2)と、この積層体(P1、P2)の側壁にゲート絶縁膜63を介して形成されたゲート電極66とによって構成されている。縦型MISFETは、下部半導体層57がドレインを構成し、中間半導体層58が基板(チャネル領域)を構成し、上部半導体層59がソースを構成している。下部半導体層57、中間半導体層58、上部半導体層59の夫々は、シリコン膜で構成され、下部半導体層57および上部半導体層59はp型にドープされ、p型シリコン膜で構成される。

(もっと読む)

半導体装置

【課題】フィン領域の寸法管理が容易なダブルゲート型FinFETを有する半導体装置を提供する。

【解決手段】半導体基板上に直線状に形成された突起状の半導体層からなるフィン領域AA1−1、AA1−2と、フィン領域の側面上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、フィン領域AA1−1、AA1−2と交差するように配置されたゲート電極GC1−1と、ゲート電極下のフィン領域の側面に形成されるチャネル領域を挟むように、フィン領域内に形成されたソース領域及びドレイン領域と、フィン領域AA1−1、AA1−2上に形成されたコンタクト材とを有する。コンタクト材が接続されたフィン領域上のコンタクト領域C1−2は、チャネル領域のチャネル長方向に延伸して配置されたフィン領域と、チャネル長方向と異なる方向に曲がって配置されたフィン領域とに跨っている。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元トランジスタでメモリセルを構成する際に問題となるチャネル部のフローティングを防止でき、高集積化可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】第1基柱2にチャネル部5と、チャネル部5の上下に形成された拡散層6,7と、チャネル部5の周りにゲート絶縁膜を介して形成されたゲート電極8とを備えた3次元トランジスタ1が、導電型の第2基柱3を囲むようにウェル領域上に複数配置され、複数個の3次元トランジスタ1が1つの第2基柱3を共有して、各々のチャネル部5がチャネル連結部4によって第2基柱3に接続されていることを特徴とする。また、6個からなる3次元トランジスタ1が、1個の第2基柱3を共有することができる。

(もっと読む)

21 - 40 / 73

[ Back to top ]