Fターム[5F083BS26]の内容

Fターム[5F083BS26]の下位に属するFターム

PMOSトランジスタ (630)

TFT (117)

抵抗素子 (33)

寄生容量 (32)

寄生ダイオード

Fターム[5F083BS26]に分類される特許

41 - 60 / 73

電界効果トランジスタ

【課題】ソフトエラー耐性の高いMOSトランジスタを提供する。

【解決手段】埋め込み絶縁膜からなるSTI2により素子分離されたトランジスタ10、20形成領域のソース・ドレイン領域4、5の直下に、ソース・ドレイン領域4、5と同一導電型の不純物領域からなるバリア層7を設ける。このバリア層7は、STI2より浅い位置に、周辺が埋め込み絶縁膜2の側面に接するように設けられる。トランジスタ10、20形成領域の周囲及び底面がSTI2及びバリア層7により囲まれるから、α線入射時のトランジスタ10、20形成領域の電圧変動が、隣接する素子へ及ぼす影響が抑制される。また、バリア層7上面が正孔又は電子の障壁となり、不純物領域7以深に生成した正孔又は電子を透過しないので、α線入射時のノイズが小さい。

(もっと読む)

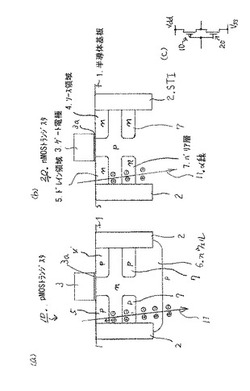

半導体装置

【課題】FinFETを用いた半導体回路の駆動特性を改善できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に配置され、1つのインバータ21Aを構成するn型FinFET N1とp型FinFET P1を具備し、n型及びp型FinFET N1,P1のそれぞれは、アクティブ領域としてのフィン部AA−n,AA−pと、ゲート絶縁膜を介して、フィン部のうちチャネル領域2,5と立体交差するゲート電極G1とを有するとともに、フィン部のうちチャネル領域2,5を挟んだ一端側及び他端側にそれぞれコンタクト領域3,6が設けられ、インバータ回路21の出力ノードとなるp型FinFET P1のコンタクト領域3のフィン幅W1は、n型FinFET N1のチャネル領域5のフィン幅W3よりも広い。

(もっと読む)

半導体装置

【課題】フローティング本体効果が得られる装置または本体領域が分離された装置を提供する。

【解決手段】SOI装置10はシリコン基板12に支持されたシリコン酸化物絶縁体層14を含む。本体領域22、58はシリコン酸化物絶縁体層14上に配置され、本体領域22は第1の導電型によって特徴づけられる。ソース、ドレイン領域18、20は第2の型によって特徴づけられる。SOI層14上方の本体領域近傍には遷移領域36、38、46、60が配置され、この遷移領域の導電型は、本体領域におけるフローティング本体効果を抑制するためには第1の導電型になるように、また本体領域を分離するためには第2の導電型になるように形成する。

(もっと読む)

垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法

【課題】垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法が開示される。

【解決手段】アクセス素子及びこれを形成する方法において、アクセス素子は、下部ソース/ドレイン領域と上部ソース/ドレイン領域を分離する垂直方向のチャンネル、チャンネル上に具備されるゲート絶縁膜、ゲート絶縁膜を横切って前記チャンネルを連結する一体型ゲート電極/連結ラインを含み、一体型ゲート電極/連結ラインはゲート絶縁膜と隣接するように具備され、下部ソース/ドレインの一部と少なくともオーバーレイされるディセンディングリップ領域を含むことができる。

(もっと読む)

半導体装置

【課題】CPU搭載無線タグのメモリ内のデータの書き換えを可能にした上で、CPUシステムを高速化し、無線タグの通信性能の向上を行う。

【解決手段】CPUが搭載されている無線タグにRFバッテリー付きのSRAMを搭載することで、CPUシステムの高速化による通信性能を向上させる。また、CPU搭載無線タグのメモリ内のデータの書き換えを可能にした。RFバッテリーは、アンテナ回路と、電源部と、蓄電装置と、を有する。SRAMとRFバッテリーとを組み合わせることで、SRAMに不揮発性メモリとしての機能を持たせる。

(もっと読む)

異なる垂直寸法のフィンを有するトリプル・ゲート・フィンFETおよびダブル・ゲート・フィンFET

【課題】異なる垂直寸法のフィンを有するトリプル・ゲート・フィンFETおよびダブル・ゲート・フィン・FETを含む半導体構造体と、半導体構造体の製造方法とを提供する。

【解決手段】垂直寸法を小さくすることが望まれる選ばれた半導体フィン13’の底部部分33にゲルマニウムを含む注入化学種が注入される。注入化学種を有する選ばれた半導体フィン13’の底部部分33は、注入化学種が存在しない半導体材料、すなわちその半導体フィンの上部部分23と、注入化学種が存在しない他の半導体フィン13との半導体材料に対して選択的にエッチングされる。従って、結果として、同じ半導体基板上に、完全な垂直寸法フィンを有しオン電流が高いFinFETと、垂直寸法が小さくなりオン電流が低いフィンFETとが得られる。注入化学種の深さを調節することによって、選ばれたフィンFETの中の半導体フィンの垂直寸法を調節することができる。

(もっと読む)

半導体集積回路

【課題】 信頼性高く不揮発記憶を書き込めるようにする。非記憶と不揮発記憶の両方、一時記憶(揮発記憶)と不揮発記憶の両方を一つの回路で行い得るようにする。

【解決手段】 前段回路の情報を状態検地強調回路Aを介して本段回路に書き込む。制御信号V selectがL、即ち/V selectがHの時、回路Aでは小電圧のVcc0とVss0が選択され、これが前段回路に印加される。この時、本段回路のn-Tr2のゲート-p型基板端子間には0V以上Vcc0-Vss0以下の電位しか印加されないのでオフとオンの判別が可能な程度にチャネル抵抗は変化するが十分な不揮発記憶書き込みを行うほどではない。V selectがH、即ち/V selectがLに変わると、回路Aでは大電圧のVcc3とVss3が選択され、これが前段回路に印加される。V selectがHになる直前のVnの論理がHならば、n-Tr2には不揮発オン状態の書込が行われ、p-Tr2には不揮発オフ状態の書込が行われる。

(もっと読む)

半導体集積回路装置

【課題】従来の半導体集積回路装置では、十分なソフトエラー耐性を得ることが困難であった。

【解決手段】本発明にかかる半導体集積回路装置は、環状に形成されたゲート電極と、ゲート電極の内側に形成されるドレイン拡散層と、ゲート電極の外側に形成されるソース拡散層とを有する第1、第2の電界効果トランジスタと、同導電型の第1、第2の電界効果トランジスタのソース拡散層のそれぞれに接するように配置され、ソース拡散層とは異なる導電型の半導体で形成される基板電位拡散層又はウェル電位拡散層と、を有し、同導電型の第1、第2の電界効果トランジスタのゲート電極には、それぞれ異なる信号が入力され、同導電型の第1、第2の電界効果トランジスタが配列される第1の方向において第1、第2の電界効果トランジスタの間には素子分離絶縁膜が存在しないことを特徴とするものである。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、高速・低消費電力で、且つ高集積化できる構成を有する半導体装置を提供することを目的とする。

【解決手段】本発明は、シリコン基板上にBOX層9及びSOI層10が積層されたSOI基板に形成される半導体装置である。そして、本発明は、SOI層10に形成されたボディ領域8にゲート電極3が巻きついたFIN型のトランジスタと、素子分離に部分分離と完全分離を併用して分離され、SOI層10に形成されたプレーナ型のトランジスタとを備える。

(もっと読む)

半導体記憶装置

【課題】SNMを向上でき、安定動作に有利な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、一対のインバータを構成する第1、第2駆動トランジスタN3、N4を備えたSRAMセル10と、前記第1、第2駆動トランジスタの電流経路の一端に接地電圧よりも低いかまたは高い値の電圧を印加する回路11とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】支持体領域の第1半導体層を十分にウエットエッチングできるようにした半導体装置の製造方法を提供する。

【解決手段】SBSI法を用いて半導体装置を製造する方法であって、支持体領域210は、第1支持体領域211と、第1支持体領域と直交する第2支持体領域212と、第1支持体領域211と第2支持体領域212との交差領域220から第1支持体領域211の長手方向に突出した第1突出領域213と、交差領域220から第2支持体領域212の長手方向に突出した第2突出領域214とを有し、支持体保持領域230は、第1突出領域213と平面視で重なり且つ交差領域220から離れた位置と、第2突出領域214と平面視で重なり且つ交差領域220から離れた位置とに設けられている。このような構成であれば、交差領域240の隅付近に隙間240が生じ、その隙間240にSiGe層の側面を露出する開口面を形成することができる。

(もっと読む)

半導体装置

【課題】バックゲート型のフィンFETを使いながらも十分なSNMを得ることのできるSRAMセルを有する半導体装置を提供する。

【解決手段】複数のフィンフィールドエフェクトトランジスタで構成され、前記複数のフィンフィールドエフェクトトランジスタの中の少なくとも1つの前記トランジスタが、第1ゲート電極と第2ゲート電極を持ち、前記第1ゲート電極の電位を制御してチャネルを形成し、前記第2ゲート電極の電位を制御してデータの書き込み時に閾値電圧を低下させるセパレートゲート型のダブルゲートフィールドエフェクトトランジスタであるSRAMセルを有する半導体装置による。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置は、微細な素子を形成する場合、微細なピッチを有するパターンのマスクを複数用い、それぞれのマスクに対して、高精度な位置合わせと高精度かつ高精細な露光とを行うため、製造コストが高く、製造工程に多くの時間を必要とする問題がある。

【解決手段】本発明にかかる半導体装置は、ソース、ドレイン、ゲートとからなる素子を有する半導体装置であって、素子は、基板上に互いに分離して形成され、それぞれがソース又はドレインとなる第1、第2の領域と、一部が第1、第2の領域の対向する面に挟まれ、基板に埋め込まれて形成されるゲート電極とを有し、ゲート電極はゲート幅方向に、第1、第2の領域のゲート幅方向の長さよりも長く、第1、第2の領域に挟まれない第3の領域を有するものである。

(もっと読む)

逆T型チャネルトランジスタを製造する方法

逆T型電界効果トランジスタ(10)を製造する方法を提供する。該方法は、基板(12)上に水平活性化領域(14)及び垂直活性化領域(16)を製造することを含む。該方法は更に、垂直活性化領域の第1の側及び垂直活性化領域の第2の側に側壁スペーサ(22)を形成することを更に有する。該方法は更に、側壁スペーサで被覆されていない水平活性化領域の一部を除去することを含む。該方法は更に側壁スペーサを除去することを含む。該方法は更に、水平活性化領域の少なくとも第1の部分及び垂直活性化領域の少なくとも第1の部分の上にゲート誘電体(26)を形成することを含む。該方法は更に、ゲート誘電体の上にゲート電極(28)を形成することを含む。該方法は更に、水平活性化領域の少なくとも第2の部分及び垂直活性化領域の少なくとも第2の部分の上にソース領域(30)及びドレイン領域(32)を形成することを含む。  (もっと読む)

(もっと読む)

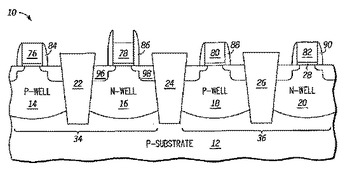

低減されたゲートドーピングを用いる半導体構造体及び同構造体を形成する方法

半導体構造体10は記憶領域34と論理領域36とを有する基板12を含む。第一のp型デバイスは記憶領域34に形成され、第二のp型デバイスは論理領域36に形成される。第一のp型デバイスの半導体ゲートの少なくとも一部は第二のp型デバイスの半導体ゲートの少なくとも一部よりもより低いp型ドーパント濃度を有する。第一及び第二のp型デバイスの半導体ゲートの各々は、ゼロではないp型ドーパント濃度を有する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの駆動力を調整する。

【解決手段】SRAMアクセス領域SAにおけるN型のMISトランジスタの上に、圧縮応力含有絶縁膜50および引っ張り応力含有絶縁膜51を形成する。一方、SRAMドライブ領域SDにおけるN型のMISトランジスタの上に、引っ張り応力含有絶縁膜51を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 カーボンナノチューブ(CNT)トランジスタを用いる半導体装置のレイアウト面積を縮小する。

【解決手段】 半導体装置は、第1の電極103と、第1の層間絶縁膜104を挟み第1の電極に対向する第2の電極106と、第1及び第2の電極間を貫通する第1のCNT部108と、第1の層間絶縁膜104と第1のCNT部108との間に介在する第1のゲート絶縁膜107と、第1の層間絶縁膜104中に形成され且つ第1のゲート絶縁膜107に接する第1のゲート電極105とを備える。更に、第2の層間絶縁膜114を挟み第2の電極と対向する第3の電極116と、各々第1のものと同様に構成された第2のゲート絶縁膜117、第2のCNT部118及び第2のゲート電極115を備える。各々の電極、ゲート絶縁膜、CNT部、ゲート電極により、垂直に配置された第1及び第2の電界効果トランジスタ151及び152が構成されている。

(もっと読む)

半導体装置

【課題】シャロー・トレンチ・アイソレーション構造により形成された素子分離膜から生じる物理的な応力に起因した半導体装置の電流駆動能力の変動が緩和され、本来の電流駆動能力を発揮可能な半導体装置を得ること。

【解決手段】第1および第2の領域を有する半導体基板と、前記半導体基板の表層に形成される溝と、前記溝に埋め込まれた素子分離絶縁膜と、前記半導体基板の表層に形成され、前記素子分離絶縁膜によって規定される活性領域と、を備え、前記素子分離絶縁膜の表面の高さが前記第1の領域と第2の領域とで異なり、いずれか一方の領域の素子分離絶縁膜の高さが前記半導体基板の表面よりも低いことを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の金属配線と半導体層との接合部の接触抵抗を低減させる。

【解決手段】タングステン等のようなメタルを主配線材料とする中間導電層42、43の上面を覆うように、窒化タングステン等からなる第1導体層48aと、タングステンシリサイド等からなる第2導体層48bとを下層から順に堆積した後、その第2導体層48bに、例えばホウ素(B)等のような不純物を導入する。その後、第1、第2導体層48a、48bをパターニングして導体層48を形成後、その導体層48に接するように、SRAMの負荷MISFET用のソースおよびドレイン用の半導体領域を形成する多結晶シリコン等からなる下部半導体層を形成する。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定にデータの書込/読出を行なうことのできるスタティック型半導体記憶装置を実現する。

【解決手段】メモリセル列毎に、セル電源線(PVL0−PVLn)を配設し、対応の列のビット線(BL0,/BL0−BLn,/BLn)の電圧レベルに従ってセル電源線のインピーダンスまたは電圧レベルを調整する。データ書込時、選択列のビット線電位に従ってセル電源線をフローティング状態として、その電圧レベルを変更し、選択されたメモリセルのラッチ能力を低減して、高速でデータを書込む。

(もっと読む)

41 - 60 / 73

[ Back to top ]