Fターム[5F083BS26]の内容

Fターム[5F083BS26]の下位に属するFターム

PMOSトランジスタ (630)

TFT (117)

抵抗素子 (33)

寄生容量 (32)

寄生ダイオード

Fターム[5F083BS26]に分類される特許

61 - 73 / 73

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の性能を向上させることが可能な技術を提供する。

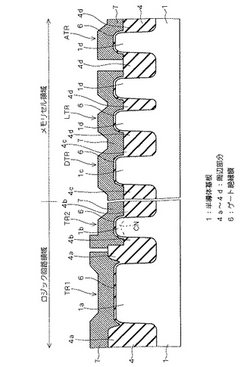

【解決手段】ロジック回路領域及びメモリセル領域における半導体基板には素子分離絶縁膜4によって活性領域1c,1bがそれぞれ区画されている。活性領域1b,1cにはMOSトランジスタTR2及びドライバトランジスタDTRがそれぞれ形成されている。上面視上において、活性領域1bのゲート幅方向の長さは活性領域1cのそれ以下である。素子分離絶縁膜4では、活性領域1bの周辺に位置する周辺部分4bの上面が活性領域1bの上面よりも下方に位置し、活性領域1cの周辺に位置する周辺部分4cの上面が活性領域1cの上面よりも下方に位置している。素子分離絶縁膜4の上面よりも上方に位置する、活性領域1b,1cの上面及びゲート幅方向の両側面にはゲート絶縁膜6を介してゲート電極7が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界効果型トランジスタを積層することを可能としつつ、電界効果型トランジスタが配置される半導体層を絶縁体上に安価に形成する。

【解決手段】絶縁層4を介して積層された半導体層3、5にVDD配線およびVSS配線をそれぞれ形成するとともに、1対のトランスファーゲートをそれぞれ形成し、さらにCMOSインバータIV1、IV2をそれぞれ構成するPチャンネル電界効果型トランジスタおよびNチャンネル電界効果型トランジスタを配置することにより、SRAMを構成する。

(もっと読む)

電界効果トランジスタとその製造方法、及び半導体装置

【課題】ソフトエラーレートを向上させる電界効果トランジスタを提供すること

【解決手段】本発明による電界効果トランジスタ1は、第1の空洞51を有する基板10と、ゲート電極40と、拡散層60とを備える。ゲート電極40及び拡散層60は、基板10の表面に平行な面XYにおいて、第1の空洞51を囲むように形成される。チャネル領域70は、第1の空洞51の側面に位置し、基板10の表面に対して略垂直に形成される。

(もっと読む)

積層型デカップリングキャパシタを有する半導体装置

【課題】積層型デカップリングキャパシタを有する半導体装置を提供することにある。

【解決手段】互いに異なった層に形成されたトランジスタを有する半導体装置において、前記記トランジスタを積層して製造する場合に使用される絶縁膜と前記絶縁膜を境界にして上下部層に存在する導電層を用いて形成され、第1,2ライン間に互いに並列連結されたデカップリングキャパシタからなる積層型キャパシタクラスタを複数個備える。

(もっと読む)

半導体装置、半導体記憶装置および半導体装置の製造方法

【課題】 ゲートからソースへの漏洩電流を伴うことなく、しきい値電圧を可変させるとともに、素子面積の増大を抑制する。

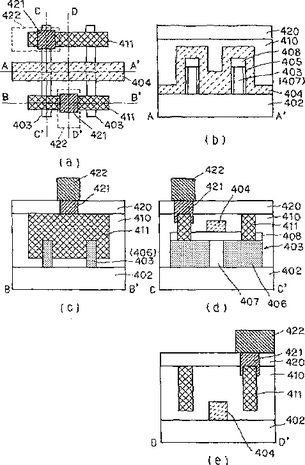

【解決手段】 半導体基板101上には絶縁層102が形成され、絶縁層102上には半導体層103が形成され、さらに、半導体層103上には絶縁層104が形成され、絶縁層104上には半導体層105が形成され、半導体層105上には、ゲート絶縁膜106を介してゲート電極107が形成され、ゲート電極107の側方には、ソース層109およびドレイン層110が形成され、ゲート電極107は、配線層を介して半導体層103に接続されている。

(もっと読む)

半導体装置

【課題】本発明は、半導体材料を有効活用して、MOS型半導体装置を小型化し、高速化、低消費電力化、高集積化に適したMOS型半導体装置を提供する。

【解決手段】ゲート電極に加える電圧により半導体層のチャネル領域を流れる電荷を制御する電界効果型半導体装置にあって、積層形成される2層のチャネル領域と、2層のチャネル領域の各層間を隔てる電気的分離層と、2層のチャネル領域に生じる異種の電荷を実質的に同時に制御するゲート電極とを有する。

(もっと読む)

DRAMセル用の分離領域を有する半導体構造及び製造方法

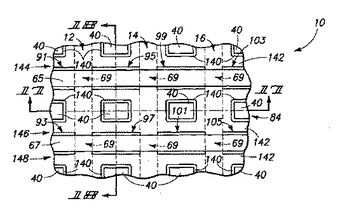

本発明は、垂直に延びるピラー(80,82)を含む半導体構造、及び、そのような構造を形成する方法を含む。垂直に延びるピラーは、トランジスタデバイス(80,95)内に組み込まれることができ、トランジスタデバイスの垂直に延びるチャネル領域を含むことができる。トランジスタデバイスは、集積回路内に組み込まれることができ、ある態様では、たとえば、ダイナミックランダムアクセスメモリ(DRAM)構造などのメモリ構造に組み込まれる。  (もっと読む)

(もっと読む)

半導体装置並びにその配置及び製造方法

【課題】半導体装置及びその装置の配置及び製造方法を提供する。

【解決手段】複数のワードライン選択信号と複数のカラム選択信号に応答してアクセスされる複数のメモリセルを備えたメモリセルアレイ、ロウアドレスをデコーディングして複数のワードライン選択信号を発生するロウデコーダ、及びカラムアドレスをデコーディングして複数のカラム選択信号を発生するカラムデコーダを備える。ロウ及びカラムデコーダは、複数のインバータ及び複数のNANDゲートを備える。複数のインバータそれぞれは、少なくとも一つの第1プルアップトランジスタ及び第1プルダウントランジスタを備る。複数のNANDゲートそれぞれは、少なくとも2個の第2プルアップトランジスタ及び少なくとも2個の第2プルダウントランジスタを備える。第1及び第2プルアップトランジスタ及び第1及び第2プルダウントランジスタは、少なくとも2層に積層して配置され。

(もっと読む)

半導体装置

【課題】 信頼性の高い半導体装置を実現するために、寄生容量の大きな半導体装置を提供する。

【解決手段】 半導体装置は、第1方向に延在する突出部1bを有する半導体基板1を含む。ゲート絶縁膜11は、突出部の上面上および第1方向に沿う側面上に配設される。ゲート電極12は、第1部分12aと第2部分12bを有する。第1部分は、突出部と交差し、且つ突出部の上面上のゲート絶縁膜上に配設される。第2部分は、突出部の側面上のゲート絶縁膜上に配設され、且つ第1方向における長さが第1部分の第1方向における長さより長い。1対のソース/ドレイン領域13が、ゲート電極の第1部分の下方の領域を挟むように突出部の表面に形成される。

(もっと読む)

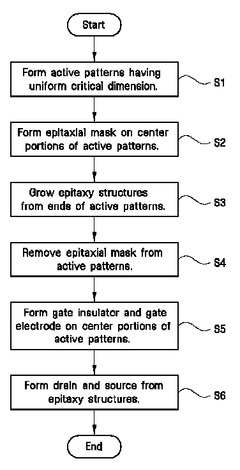

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

ノード・キャパシタンスを増加した半導体メモリ・デバイス

【課題】 ノード・キャパシタンスを増加した半導体メモリ・デバイスを提供することにある。

【解決手段】 集積回路半導体メモリ・デバイス(100)は、ゲートから基板へのキャパシタンスを増加し、それにより、ソフト・エラー率を低減するために、ストレージ・トランジスタのゲートの下に基板(112)の一部分(130)には存在しないBOX層として特徴付けられた第1の誘電体層(116)を有する。第1の誘電体層とは異なる特性を有する第2の誘電体層(132)は、基板のその部分(130)を少なくとも部分的に覆う。このデバイスは、フィン(122)と、ゲートとフィンとの間のゲート誘電体層(124、126)とを含むFinFETデバイスにすることができ、第2の誘電体層はゲート誘電体層より漏れが少ない。

(もっと読む)

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

61 - 73 / 73

[ Back to top ]