Fターム[5F083BS26]の内容

Fターム[5F083BS26]の下位に属するFターム

PMOSトランジスタ (630)

TFT (117)

抵抗素子 (33)

寄生容量 (32)

寄生ダイオード

Fターム[5F083BS26]に分類される特許

1 - 20 / 73

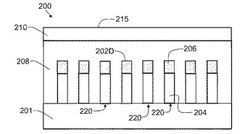

FinFETを形成する方法およびFinFET構造

【課題】 ゲートの平面性が改善されたFinFETおよび形成方法を提供する。

【解決手段】 不要なフィンを除去する前にフィンのパターン上にゲートが配置される。リソグラフィ技法またはエッチング技法あるいはその両方の組み合わせを使用して、不要なフィンを除去することができる。残りのフィンの全部または一部を併合することができる。

(もっと読む)

リレーデバイスを有するメモリ要素

【課題】メモリ要素有する集積回路を提供すること。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜とゲート絶縁膜との界面において、電子の界面散乱を抑制することで、電気的特性に優れたトランジスタを提供する。

【解決手段】基板上に酸化物半導体膜を形成し、酸化物半導体膜上に酸化物半導体以外の半導体膜を形成した後、酸化物半導体膜と該半導体膜との界面において、酸化物半導体膜中の酸素原子と半導体膜中の原子とを結合させる。これにより、酸化物半導体膜と該半導体膜との界面において構造を連続させることができる。また、酸化物半導体膜から脱離した酸素が、該半導体膜に拡散することで、該半導体膜は酸化されるため、絶縁膜とすることができる。このようにして形成されたゲート絶縁膜を用いることで、酸化物半導体膜とゲート絶縁膜との界面において電子の界面散乱が抑制され、電気的特性に優れたトランジスタを作製できる。

(もっと読む)

トンネルトランジスタ、トランジスタを含む論理ゲート、論理ゲートを使用するスタティックランダムアクセスメモリ、およびトンネルトランジスタの製造方法

【課題】第1、第2ゲートを有するトンネルトランジスタで、第1、第2のゲート間の電圧の差がより小さい場合にしようできるトンネルトランジスタを提供する。

【解決手段】ドレイン2、ソース4およびドレイン2とソース4との間で電流を制御するための少なくとも第1ゲート6とを含み、第1および第2のゲート誘電体材料7、11の第1側9、13が、それぞれ第1および第2の半導体部分14、15に実質的に沿って、実質的に接続して配置されたトンネルトランジスタ1。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と該酸化物半導体膜と接する下地となる膜との界面の電子状態が良好なトランジスタ。

【解決手段】下地となる膜は酸化物半導体膜と同様の原子配列を有し、下地となる膜と酸化物半導体膜とが接している面において、面内の下地膜の最隣接原子間距離と酸化物半導体の格子定数の差を、下地となる膜の同面内における最隣接原子間距離で除した値は0.15以下、好ましくは0.12以下、さらに好ましくは0.10以下、さらに好ましくは0.08以下とする。例えば、立方晶系の結晶構造を有し(111)面に配向する安定化ジルコニアを含む下地となる膜上に酸化物半導体膜を成膜することで、下地となる膜の直上においても結晶化度の高い結晶領域を有する酸化物半導体膜が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体装置

【課題】不揮発性メモリを提供する。

【解決手段】一般的なSRAMと同様の回路構成を有し、該SRAMの記憶保持部と電源電位線の間にオフ電流の小さいトランジスタを配することで、記憶保持部からの電荷の漏れが防止された半導体装置(不揮発性メモリ)とする。ここで、記憶保持部からの電荷の漏れを防止するためのオフ電流の小さいトランジスタとしては、酸化物半導体膜により設けられたトランジスタを用いることが好ましい。このような構成はシフトレジスタにも適用することができ、消費電力の小さいシフトレジスタを得ることができる。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体素子および作製方法

【課題】ソフトエラー率を有意に低下させる半導体素子およびその作製方法に関する。

【解決手段】半導体基板(100)には、第1の型の不純物でドープされた第1ウェル領域(104)の下に第1の型の第1ドープ領域(102)がある。第1ウェル領域は、第1ドープ領域と電気的に接続されている。第1ウェル領域と第1ドープ領域(102)との間に分離領域(206)を形成する。分離領域は第2ウェル領域と電気接続されている。分離領域および第2ウェル領域は、第1の不純物型と反対の型の第2の不純物型でドープされている。前記方法はさらに、第1ウェル領域内および分離領域下に第2ドープ領域を形成する工程をさらに有し得る。第1の型の不純物を有する第3ドープ領域を、分離領域の上に形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクトの接触不良を防止して、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】高密度版回路における電界効果トランジスタTr3のゲート電極G3と電界効果トランジスタTr4のゲート電極G4とのピッチは、高速版回路における電界効果トランジスタTr1のゲート電極G1と電界効果トランジスタTr2のゲート電極G2のピッチよりも小さいが、シェアードコンタクトホールSCが達する部分のゲート電極G3に切欠を設けることにより、シェアードコンタクトホールSCと不純物領域S/Dとの接触面積を広くする。

(もっと読む)

スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

半導体装置

【課題】特性のばらつきが少ないトランジスタを用いた消費電力の少ないSRAMセルを有する半導体装置を提供する。

【解決手段】一実施の形態による半導体装置は、半導体基板上に形成されたSRAMセルを有する。第1および第2のロードトランジスタの前記n型ソース領域、前記第1および第2のドライバトランジスタの前記n型ドレイン領域、ならびに前記第1および第2のトランスファトランジスタの前記n型ソース領域および前記n型ドレイン領域は、前記第1および第2のロードトランジスタの前記p型ドレイン領域ならびに前記第1および第2のドライバトランジスタの前記p型ソース領域のうちの任意の2つの領域の間以外の領域に位置する。

(もっと読む)

SRAMメモリセル

【課題】現存のデバイスの欠点を取り除き、さらにSRAM型メモリセルの体積を減少させる。

【解決手段】SRAM型メモリセルであって、絶縁層によってベース基板から隔離された半導体材料の薄膜を含む絶縁基板上の半導体と、2個のアクセストランジスタT1,T4と、2個の伝導トランジスタT2,T5と、2個の充電トランジスタT3,T6とを含み、メモリセルは、トランジスタT1−T6のそれぞれが、チャネルの下方でベース基板内に形成されたバックコントロールゲートBG1,BG2を有し、トランジスタの敷居電圧を調整するようにバイアスをかけられ、第1のバックゲートラインはアクセストランジスタT1,T4に接続し、第2のバックゲートラインは伝導トランジスタT2,T5および充電トランジスタT3,T6に接続し、各々の電位はセル制御動作の型に応じて調整される。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

半導体装置

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲む第1のゲート電極と、第1のゲート電極の周囲を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲を取り囲む第1の筒状半導体層と、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第1の筒状半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第1の筒状半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有するインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

1 - 20 / 73

[ Back to top ]