Fターム[5F083BS29]の内容

Fターム[5F083BS29]の下位に属するFターム

トップゲート型 (25)

ダブルゲート型(ゲートを複数有するTFT) (9)

ボトムゲート型 (3)

オフセットゲート (3)

チャネル構造 (12)

Fターム[5F083BS29]に分類される特許

1 - 20 / 65

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

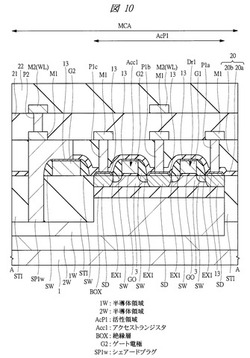

【解決手段】SRAMを構成するアクセストランジスタAcc1が配置される活性領域AcP1の下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wの底部および側部が、n型の半導体領域2Wと接するように配置し、p型の半導体領域1Wをn型の半導体領域2Wでpn分離し、アクセストランジスタAcc1のゲート電極G2とp型の半導体領域1Wを接続する。そして、この接続は、アクセストランジスタAcc1のゲート電極G2の上部からp型の半導体領域1Wの上部まで延在する一体の導電性膜であるシェアードプラグSP1wによりなされる。これにより、アクセストランジスタAcc1がオン状態の場合において、バックゲートであるp型の半導体領域1Wの電位が同時に高くなり、トランジスタのオン電流を大きくできる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

記憶装置及び半導体装置

【課題】消費電力を抑えることができる記憶装置を提供する。

【解決手段】第1クロック信号に従って、データを含む信号の電位の極性を反転させることで、出力電位を生成する第1論理素子と、第1論理素子が生成する出力電位を保持する第2論理素子及び第3論理素子と、トランジスタを用いたスイッチング素子と、第2論理素子及び第3論理素子において保持される第1論理素子の出力電位が、スイッチング素子を介して与えられることで、データを記憶する容量素子と、を有し、第2論理素子は、第1クロック信号とは異なる系統の第2クロック信号に従って、第3論理素子の出力電位の極性を反転させることで、第2論理素子の出力電位を生成し、第3論理素子は、第2論理素子の出力電位の極性を反転させることで、第3論理素子の出力電位を生成する記憶装置。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

SRAM装置

【課題】低消費電力でより安定して動作することが可能なSRAM装置を提供する。

【解決手段】SRAM装置100は、非反転出力端子Qおよび反転出力端子/Qを有するフリップフロップ回路FFを備える。非反転出力端子と第1のビット線bitとの間に、非反転出力端子側から第1のビット線側への方向に電流が流れる第1のトンネルトランジスタT1を備える。非反転出力端子と第1のビット線との間で、第1のビット線側から非反転出力端子側への方向に電流が流れる第2のトンネルトランジスタT2を備える。反転出力端子と第2のビット線bitbとの間に、反転出力端子側から第2のビット線側への方向に電流が流れる第3のトンネルトランジスタt3を備える。反転出力端子と第2のビット線との間で、第2のビット線側から反転出力端子側への方向に電流が流れる第4のトンネルトランジスタt4を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

記憶素子および信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、アモルファスシリコン、ポリシリコン、微結晶シリコン、あるいは酸化物半導体等の化合物半導体をチャネル形成領域に含み、そのチャネル長が最小加工線幅の10倍以上あるいは、1μm以上であるトランジスタを用いる。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

プログラム及び半導体装置

【課題】消費電力の低下が可能な半導体装置及びメモリ回路、並びにこれらの動作方法を

提案することを課題とする。

【解決手段】演算回路と制御回路とを具備する演算処理回路と、ROMとRAMとを具備

するメモリ回路とを有し、演算処理回路とメモリ回路は、アドレスバス及びデータバスを

介して接続され、ROMは、演算処理回路を用いて実行される機械語プログラムのデータ

が格納されており、RAMは、複数のバンクを有し、機械語プログラムが実行した際の処

理データが、複数のスタックに分割されて複数のバンクに格納され、複数のバンクに格納

される複数のスタックにおいて、機械語プログラム終了まで使用されないスタックが省か

れ、連続したスタックが同一のバンクに書き込まれるように、機械語プログラムに基づい

て演算処理回路が動作する。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

1 - 20 / 65

[ Back to top ]