Fターム[5F083BS30]の内容

Fターム[5F083BS30]に分類される特許

1 - 20 / 25

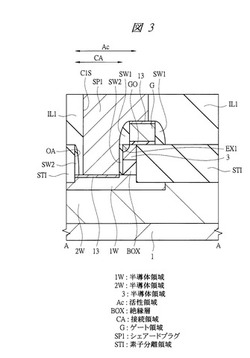

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置

【課題】低電圧動作が可能なSRAMをそのセル面積の増加を抑えて実現する。

【解決手段】第1方向Sに並ぶP型ウェル領域20、N型ウェル領域30、P型ウェル領域40に、第2方向Tに隣接するメモリセル1aが形成される。各メモリセル1aは、P型ウェル領域20,40に形成されたトランスファトランジスタTf1,Tf2及びドライバトランジスタDr1,Dr2、N型ウェル領域30形成されたロードトランジスタLo1,Lo2を備える。SRAM1では、第2方向Tに隣接するメモリセル1aの、互いのトランスファトランジスタTf1のゲート電極がワード線WL1に、互いのトランスファトランジスタTf2のゲート電極がワード線WL2に、それぞれ電気的に接続される。ワード線WL1はP型ウェル領域20に、ワード線WL2はP型ウェル領域40に、それぞれ電気的に接続される。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】オフ電流が小さい薄膜トランジスタによって問題なく動作することが可能な記憶素子を含む記憶装置を提供することを課題とする。

【解決手段】酸化物半導体層を有する薄膜トランジスタが少なくとも一つ設けられた記憶素子を、マトリクス状に配置した記憶装置を提供する。酸化物半導体層を有する薄膜トランジスタは、電界効果移動度が高く、且つオフ電流を小さくできるため、問題なく良好に動作させることができる。また、消費電力を低くすることもできる。このような記憶装置は、例えば酸化物半導体層を有する薄膜トランジスタが表示装置の画素に設けられている場合に、記憶装置を同一基板上に形成することができるため、特に有効である。

(もっと読む)

SOI構造シングルイベント耐性のNAND素子、及びNOR素子

【課題】高いシングルイベント耐性を有するNAND素子、NOR素子を提供する。

【解決手段】チャネルが並列に接続された第1のpチャネルMOSトランジスタ及び第2のpチャネルMOSトランジスタと、チャネルが直列に接続された第1のnチャネルMOSトランジスタ及び第2のnチャネルMOSトランジスタと、が第1の電圧源側に接続されたノードから第2の電圧源側に接続されたノードに向かって直列にSOI構造の基板上で接続され、それらのトランジスタのそれぞれに対して、それとゲート同士が相互に接続された同じ導電型のチャネルのMOSトランジスタがチャネルが直列に更に接続された二重化構造を有する。

(もっと読む)

炭素ナノチューブ薄膜を利用したSRAM

【課題】炭素ナノチューブ(CNT:Carbon NanoTube)薄膜を利用したSRAMを提供する。

【解決手段】少なくとも第1CNTトランジスタを備える第1CNTインバータと、少なくとも第2CNTトランジスタを備え、第1CNTインバータに連結された第2CNTインバータと、少なくとも第1CNTインバータに連結された第1スイッチングトランジスタと、少なくとも第2CNTインバータに連結された第2スイッチングトランジスタと、を備えるSRAMである。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】バリッドビットにおける無効化処理において、電源投入時に無効化処理を行うことができる半導体記憶装置を提供する。

【解決手段】第1のトランジスタと、第2のトランジスタと、を有する第1のインバータ回路と、入力部が前記第1のインバータ回路の出力部に接続され、出力部が前記第1のインバータの入力部に接続され、第3のトランジスタと、第4のトランジスタと、を有する第2のインバータ回路と、を含む初期化用メモリセルを有し、第3のトランジスタのしきい値電圧の絶対値は、第1のトランジスタのしきい値電圧の絶対値より低い構成とする。

(もっと読む)

半導体装置

【課題】nチャネルMISトランジスタとpチャネルMISトランジスタとが接続するドレイン領域において、トランジスタ特性を悪化させる不具合が生じないCMOSデバイスを含む半導体装置を提供する。

【解決手段】基板11上の半導体領域に形成されたソース領域18Aと、ドレイン領域17Aとを有するnチャネルMISトランジスタと、半導体領域に形成されたソース領域18Bと、ドレイン領域17Bと有するpチャネルMISトランジスタとを具備する。ドレイン領域17Aと17Bとが接続するように配置されると共に、同一の材料で形成され、ソース領域18A,18Bの少なくともいずれかがドレイン領域17A,17Bと異なる材料で形成されている。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にする。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリに供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまたは書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにすることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込みにおいて、消費電流を一定にできる。

(もっと読む)

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

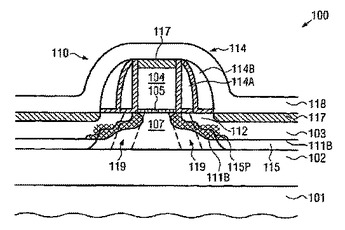

ボディポテンシャルが低減したSOIトランジスタとその製造法

炭素、フッ素などの原子種(111B)をドレイン及びソース領域(115、206)とボディ領域(107、207)とに導入することで、SOIトランジスタ(110、210M)の接合部のリークが著しく増加し、これにより、蓄積した少数電荷キャリアに対してリークパス(119、219A)が強化される。これにより、ボディポテンシャルの変動が著しく減り、その結果、最新のSOIデバイス(100)の全体のパフォーマンスが向上する。具体的な実施形態では、このメカニズムは、スタティックRAM領域(250M)などのしきい値電圧にセンシティブなデバイス領域に選択的に適用することができる。  (もっと読む)

(もっと読む)

シリコン−ゲルマニウム立体構造CMOS上の局所配線の製造方法

【課題】シリコン−ゲルマニウム立体構造CMOSにおいて、シリコンCMOS素子とゲルマニウムCMOS素子との間の局所配線を容易に形成する。

【解決手段】シリコンCMOS素子を有するシリコン基板を準備し(12)、該素子の上部に絶縁層を形成する(14)。上記絶縁層を部分的に開口し(16)、その上にゲルマニウム薄膜を形成する(18)。アニール処理により、上記薄膜のゲルマニウムを流動化する(24)。これにより、開口部に上記ゲルマニウムが流れ込み、該ゲルマニウムと上記シリコン基板および上記シリコンCMOS素子との間に接点が形成される。さらに冷却することで、上記ゲルマニウムがLPE成長により結晶化される(26)。そして、単結晶のゲルマニウム上にゲルマニウムCMOS素子を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ボディコンタクト構造を採らなくても、パスゲートリークの発生を防止できるようにした半導体装置及びその製造方法を提供する。

【解決手段】複数のメモリセル50からなるSRAMを有する半導体装置であって、メモリセル50を構成するパスゲートトランジスタQ5,Q6は(シリコン基板に直接形成された)バルクトランジスタであり、それ以外のトランジスタQ1〜Q4は(シリコン基板に部分的に形成されたSOI構造のSi層に形成された)SOIトランジスタである。このような構成であれば、パスゲートトランジスタQ5,Q6の基板電位を例えばGNDに固定することができ、パスゲートトランジスタQ5,Q6のチャネル領域下部における電荷の蓄積を防止することができる。

(もっと読む)

半導体装置

【課題】半導体装置に搭載された不揮発性記憶装置に格納された情報を読み出す時、アドレス信号などを入力し、センスアンプなどを用いて情報を読み出す。このとき所定の時間を要するので、その遅れを考慮した半導体装置の設計が必要である。また、センスアンプは消費電流が膨大である。さらに、読み出しビット数が決められているので、1ビットのみ読み出す場合にも、他の不要な情報も読み出す必要がある。

【解決手段】電気的に導通または絶縁する手段を有する電気素子と、リセット素子と、ラッチ素子と、から構成される記憶素子により、不揮発性記憶回路を構成する。記憶素子では、無線チップのリセット時に、電気素子が電気的に絶縁か導通かにより、異なる情報をラッチ素子に格納する。このような構成とすることで、不揮発性記憶装置を搭載した低消費電力の無線チップを安価に提供することができる。

(もっと読む)

積層メモリセル

【課題】高集積SRAMに好適な積層メモリセルを提供する。

【解決手段】高集積SRAMに好適な積層メモリセルにおいて、第1層に形成された第1,2プルダウントランジスタと、前記第1層の上部に位置した第2層に形成され、前記第1,2プルダウントランジスタとそれぞれ連結されてインバータラッチを形成する第1,2プルアップトランジスタと、前記第2プルダウントランジスタのゲートとビットラインとの間に接続され、前記第1層または第2層の上部に位置した第3層に形成されるパストランジスタと、を備える。

(もっと読む)

改善されたセル安定性及び性能のためのハイブリッド・バルク−SOI6T−SRAMセル

【課題】 改善されたセル安定性及び性能を示すハイブリッド・バルクSOI 6T STRAMセルを提供すること。

【解決手段】 本発明は、同じ結晶配向又は異なる結晶配向を有するSOI領域及びバルク−Si領域を含む基板と、バルク−Si領域からSOI領域を分離する分離領域と、SOI領域内に配置された少なくとも1つの第1デバイス及びバルク−Si領域内に配置された少なくとも1つの第2デバイスとを含む、6T−SRAM半導体構造体を提供する。SOI領域は、絶縁層の上にシリコン層を有する。バルク−Si領域はさらに、第2デバイスの下にあるウェル領域と、浮遊体効果を安定化させる、ウェル領域へのコンタクトとを含む。ウェル・コンタクトはまた、バルク−Si領域内のFETの閾値電圧を制御して、SOI領域のFET及びバルク−Si領域のFETの組み合わせから構築されたSRAMセルのパワー及び性能を最適化するためにも用いられる。

(もっと読む)

集積回路に関する応力下でのインターレイヤー誘電体

ロジック(16)と、ロジックとは異なりSRAMアレイに関するインターレイヤー誘電体(ILD)(42,40)を処理することにより改善された性能を備えた静的ランダムアクセスメモリ(SRAM)とを有する集積回路(10)を提供する。Nチャネルロジック(20)及びSRAMトランジスタ(24,26)は、非圧縮応力を備えたILD(40)を有し、Pチャネル論理トランジスタ(22)ILD(42)は圧縮応力を有し、PチャネルSRAMトランジスタ(26)は圧縮であるが、Pチャネル論理トランジスタ(22)よりも小さく、緩和されても良く、又は引っ張りでも良い。PチャネルSRAMトランジスタ(26)に関する集積回路(10)に関して、Pチャネル論理トランジスタ(22)よりも低い移動度を有することは有益である。低い移動度を備えたPチャネルSRAMトランジスタ(26)は、良好な書き込み時間または低電圧での書き込みマージンのいずれかで、より良好な書き込み性能を生じる。 (もっと読む)

1 - 20 / 25

[ Back to top ]