Fターム[5F083BS38]の内容

Fターム[5F083BS38]に分類される特許

1 - 20 / 32

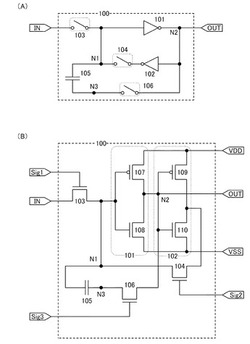

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧でもSNMと書き込みマージンを両立させたSRAMを備える。

【解決手段】SRAMは、複数列に対応して設けられた複数のセル電源線、電源電圧を供給する電源線、及び前記複数のセル電源線にそれぞれ対応して設けられ、各々はその対応するメモリセル電源線と前記電源線との間を電気的に接続する複数の電源回路を含む。メモリセルの各々は、第1及び第2のPチャネル型トランジスタと、第1ないし第4のNチャネル型トランジスタと第1及び第2の記憶ノードとを有するCMOSラッチ回路で構成される。電源回路は、第1の状態時にはその接続するセル電源線に第1の電圧を供給し、第2の状態時にはその接続するセル電源線に前記第1の電圧よりも低い第2の電圧を供給する、

(もっと読む)

記憶素子、信号処理回路および記憶素子の駆動方法

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を位相反転素子の入力あるいは出力に接続し、他方の電極をスイッチング素子に接続する。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

論理回路とそれを使用するメモリ

【課題】

低い電源電圧でも動作可能な論理回路を提供する。

【解決手段】

論理回路は,電源電圧側に接続された第1導電型の第1のMOSFETと,基準電圧側に接続されゲートに入力信号が供給される第1導電型の第2のMOSFETと,第1,第2のMOSFETの電流端子の接続ノードに接続された出力端子と,第1のMOSFETのゲートとソース間に設けられたカップリングキャパシタと,第1のMOSFETのゲートと電源電圧との間に設けられた抵抗とを有する。

(もっと読む)

半導体記憶装置

【課題】低電圧動作させた場合においても、メモリセルのサイズを低減させつつ、安定動作を実現するとともに、セルトランジスタのばらつきによる影響を低減する。

【解決手段】第1および第2のPMOSのソースは第1の電源線、第1のPMOSのドレインは第1のノード、第2のPMOSのドレインは第2のノード、第1および第2のNMOSのソースは第2の電源線、第1のNMOSのドレインは第1のノード、第1のノードは、第2のPMOSのゲートと第2のNMOSのゲート、第2のノードは、第1のPMOSのゲートと第1のNMOSのゲート、第1のトランジスタのゲートは、第1の信号線、ソースは第1のノード、ドレインは第2のノード、第2のトランジスタのゲートは、第2のノード、ソースは第3のノード、ドレインは第2の信号線、第3のトランジスタのゲートは、第3の信号線、ソースは第4の信号線、ドレインは第3のノードに接続される。

(もっと読む)

半導体装置

【課題】ソフトエラー耐性の大きいSRAM(半導体記憶装置)を提供する。

【解決手段】横長型セル(3分割されたウェルがワード線の延在方向に並び、ビット線方向よりもワード線方向に長いメモリセル)上に、第1と第2ドライバMOSトランジスタN1,N2と、第1ロードMOSトランジスタP1,P2と、第1と第2アクセスNMOSトランジスタN3,N4とを設けたフルCMOSSRAMにおいて、記憶ノードとなる埋め込み配線5D,5Gは、ポリシリコン配線3C,3Bの長手方向と交差する方向に延びる傾斜部50D,50Gを有する。

(もっと読む)

半導体記憶装置

【課題】極めて簡素な構成で製造工程及び製造コストの増加を招くことなく記憶ノードの容量を大幅に増加させ、更なる微細化の要請にも充分応えることを可能とする。

【解決手段】各インバータIV1,IV2の記憶ノードSN1,SN2と電気的に接続されるように、各記憶ノードSN1,SN2の上層部分にそれぞれ導電層CL1,CL2を配置する。当該上層部分やその隣接層部分にはVDD層及びVSS層が配置されており、導電層CL1,CL2とVDD層及びVSS層との間、及び導電層CL1,CL2同士で容量結合して寄生容量が生じる。この構成により、記憶ノードSN1,SN2の容量が増加することになる。

(もっと読む)

半導体記憶装置

【課題】メモリセル面積を増大させることなく、配線間のカップリングノイズを低減可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、マルチポートメモリを有しており、行列状に配置された複数のメモリセルMCと、第1ポート13aに接続された複数の第1のワード線WLA0〜WLAnと、第2ポート13bに接続された複数の第2のワード線WLB0〜WLBnとを備えている。複数の第1のワード線WLA0〜WLAnの各々と複数の第2のワード線WLB0〜WLBnの各々とが平面レイアウトにおいて交互に配置されている。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置、例えば、SRAMのメモリセルのソフトエラーを低減させた高性能の半導体集積回路装置を提供する。

【解決手段】それぞれのゲート電極とドレインとが交差接続された一対のnチャネル型MISFETを有するSRAMメモリセルの、交差接続部の配線MD2の表面を酸化シリコン膜21の表面より突出した形状とし、この配線MD2上に、容量絶縁膜となる窒化シリコン膜23と、上部電極24を形成する。この配線MD2、窒化シリコン膜23および上部電極24とで容量Cを形成することができ、α線によるソフトエラーを低減することができる。また、配線MD2側壁にも容量を形成することができるため、容量の増加を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMセルにおける放射線損傷による不具合を防止する。

【解決手段】

第2、第3層間絶縁膜103、104を両側面とし、第1層間絶縁膜102の主面102aを底面とする開口111が構成されている。開口111の内側面には、ノード電極である下部電極105が形成されている。下部電極105は、キャパシタの下部電極として機能すると同時に、SRAMセルのノード配線としても機能する。第3層間絶縁膜104の主面104a及び開口111内側面の下部電極105上には容量絶縁膜106が形成されている。開口111の内部及び開口111周囲の第3層間絶縁膜104上には上部電極107が形成されている。埋め込まれた上部電極107は、開口111の周囲の第3層間絶縁膜104上にも形成され、キャパシタの上部電極として機能する。開口111の間口部分より上に形成される上部電極107の幅L1は、開口111の幅L2よりも大きい。

(もっと読む)

半導体記憶装置および半導体集積回路装置

【課題】SRAMセルのダイナミックスタビリティを考慮して、メモリセルの安定性をさらに増大させる。

【解決手段】フラッシュメモリセルのフローティングゲート(FG)およびコントロールゲート(CG)を製造する工程を利用して、容量素子(C1,C2)を、記憶ノード(SN,/SN)に接続する。すなわち、SRAMセルの負荷トランジスタ(PT1,PT2)およびドライバトランジスタ(NT1,NT2)のゲート電極を、フローティングゲートと同一層の配線で形成し、コントロールゲートと同一の配線層の配線を、負荷およびドライバトランジスタのゲート電極と整列して配置するキャパシタ電極として形成する。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】SRAMの蓄積ノード間容量と、アナログ容量を有する素子とを単一の基板上に形成した半導体集積回路装置の性能の向上を図る。

【解決手段】メモリセル形成領域(SRAM)の一対のnチャネル型MISFET上の酸化シリコン膜21中にプラグP1を形成し、酸化シリコン膜21およびプラグP1の上部に、一対のnチャネル型MISFETのそれぞれのゲート電極とドレインとを接続する局所配線LIc(M0c)を形成した後、さらに、この上部に、容量絶縁膜23および上部電極24を形成し、また、アナログ容量形成領域(Analog Capacitor)の酸化シリコン膜21およびこの膜中のプラグP1上に、メモリセル形成領域に形成される前記局所配線、容量絶縁膜および上部電極と同一工程で、局所配線LIc(M0c)、容量絶縁膜23および上部電極24を形成する。

(もっと読む)

ソフトエラー率の計算方法、プログラム、半導体集積回路の設計方法及び設計装置、並びに半導体集積回路

【課題】SRAM又は記憶回路素子のソフトエラー率(SER)を製品設計段階で簡単に見積もる方法を提供する。

【解決手段】MISFETで構成される記憶回路又は情報保持回路の情報記憶ノード拡散層面積とソフトエラー率(SER)との関係を複数の情報記憶ノード電圧Vnをパラメータとして測定した測定結果を使用し(S1)、同一情報記憶ノード電圧VnにおけるSERの情報記憶ノード面積依存性を表す第1の数式を導出する(S2)。そして、測定結果から同一情報記憶ノード面積ScにおけるSERの情報記憶ノード電圧依存性の関係を第1の数式に代入して第2の数式を導出する(S3)。求めたい記憶回路又は情報保持回路の情報記憶ノード面積及び情報記憶ノード電圧を第2の数式に代入すれば、そのSERを計算することができる(S4)。

(もっと読む)

半導体記憶装置及び半導体記憶装置の動作方法

【課題】従来の半導体記憶装置では、半導体記憶装置の動作速度を満足しつつ、高いSER耐性を実現することは難しかった。

【解決手段】一対の記憶ノードと、この記憶ノードに一端が接続された容量と、この容量の他端に接続されるとともに、半導体記憶装置が所定の速度以上で動作する場合には、容量の他端の接続状態を変更するスイッチ部と、を備える。このように、半導体記憶装置の動作状態に応じて、容量の他端の接続状態を変更することで、記憶ノードに接続される容量が半導体記憶装置の動作速度に与える影響を抑えることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を減少しつつ、2つの配線層間を電気的に接続すること。

【解決手段】2つの配線11C、11D間の下層部にて、数珠繋ぎ形状に形成されるとともに、2つの配線11C、11Dを電気的に接続するコンタクトプラグ9cを備える。2つの配線11C、11Dは、互いに離間して同一の層に形成されている。コンタクトプラグ9cは、配線4bに接続されるコンタクトプラグ9bと、ソース/ドレイン領域6に接続されるコンタクトプラグ9aと同時に形成される。

(もっと読む)

半導体集積回路装置

【課題】 半導体基板上に形成されるSRAMのキャパシタ容量を増大することを可能にした半導体集積回路装置を提供する。

【解決手段】 半導体基板100上に形成されるSRAMに接続される下層配線で構成される下部容量電極H1と、下層配線の上面及び側面を覆うように形成される容量絶縁膜131と、容量絶縁膜131上に形成される上部容量電極132とでキャパシタを構成し、下部容量電極132は下層配線で構成されるノード配線N1,N2はもとより、下層接地配線UGNDL又は下層電源配線UVDDLの少なくとも一方を含む。電源配線や接地配線を利用してキャパシタC1〜C4を構成するので、ノード配線N1,N2のみでキャパシタC1,C2を構成する場合に比較してキャパシタ容量を増大し、α線等に対するソフトエラー耐性を向上する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置、例えば、SRAMのメモリセルのソフトエラーを低減させた高性能の半導体集積回路装置を提供する。

【解決手段】それぞれのゲート電極とドレインとが交差接続された一対のnチャネル型MISFETを有するSRAMメモリセルの、交差接続部の配線MD2の表面を酸化シリコン膜21の表面より突出した形状とし、この配線MD2上に、容量絶縁膜となる窒化シリコン膜23と、上部電極24を形成する。この配線MD2、窒化シリコン膜23および上部電極24とで容量Cを形成することができ、α線によるソフトエラーを低減することができる。また、配線MD2側壁にも容量を形成することができるため、容量の増加を図ることができる。

(もっと読む)

半導体集積回路装置

【課題】SRAMのメモリセルの蓄積ノード容量を増やしてソフトエラー耐性を向上させる。

【解決手段】6個のMISFETでメモリセルを構成した完全CMOS型のSRAMにおいて、メモリセルの駆動用MISFETQd1,Qd2、転送用MISFETQt1,Qt2および負荷用MISFETQp1,Qp2のそれぞれのゲート電極6,10a,10bを構成する第1導電層の上層に形成した高融点金属シリサイド層でCMOSインバータの相互の入出力端子間を接続する一対の局所配線L1,L2を形成し、この局所配線L1,L2の上層に形成した基準電圧線20を局所配線L1,L2と重なるように配置して蓄積ノード容量素子を形成する。局所配線L1,L2の一方は、この蓄積ノード容量素子の一方の電極を構成する。

(もっと読む)

1 - 20 / 32

[ Back to top ]