Fターム[5F083BS46]の内容

Fターム[5F083BS46]の下位に属するFターム

転送トランジスタと駆動トランジスタの接続 (57)

駆動トランジスタと負荷素子との接続配線 (117)

Fターム[5F083BS46]に分類される特許

1 - 20 / 74

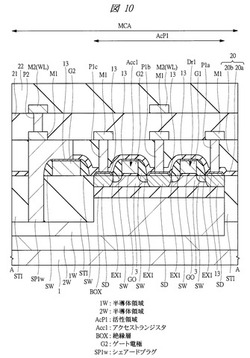

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1が配置される活性領域AcP1の下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wの底部および側部が、n型の半導体領域2Wと接するように配置し、p型の半導体領域1Wをn型の半導体領域2Wでpn分離し、アクセストランジスタAcc1のゲート電極G2とp型の半導体領域1Wを接続する。そして、この接続は、アクセストランジスタAcc1のゲート電極G2の上部からp型の半導体領域1Wの上部まで延在する一体の導電性膜であるシェアードプラグSP1wによりなされる。これにより、アクセストランジスタAcc1がオン状態の場合において、バックゲートであるp型の半導体領域1Wの電位が同時に高くなり、トランジスタのオン電流を大きくできる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

メモリセル

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

プログラム及び半導体装置

【課題】消費電力の低下が可能な半導体装置及びメモリ回路、並びにこれらの動作方法を

提案することを課題とする。

【解決手段】演算回路と制御回路とを具備する演算処理回路と、ROMとRAMとを具備

するメモリ回路とを有し、演算処理回路とメモリ回路は、アドレスバス及びデータバスを

介して接続され、ROMは、演算処理回路を用いて実行される機械語プログラムのデータ

が格納されており、RAMは、複数のバンクを有し、機械語プログラムが実行した際の処

理データが、複数のスタックに分割されて複数のバンクに格納され、複数のバンクに格納

される複数のスタックにおいて、機械語プログラム終了まで使用されないスタックが省か

れ、連続したスタックが同一のバンクに書き込まれるように、機械語プログラムに基づい

て演算処理回路が動作する。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度で素子特性に優れた、SRAMを備えた半導体装置を提供する。

【解決手段】一対の駆動トランジスタと一対の負荷トランジスタと一対のアクセストランジスタを備えたSRAMセル単位を有する半導体装置であって、前記トランジスタはそれぞれ、基体平面に対して上方に突起した半導体層と、この半導体層を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体層の間に介在するゲート絶縁膜と、前記半導体層に設けられた一対のソース/ドレイン領域を有し、前記駆動トランジスタはそれぞれ、前記負荷トランジスタ及び前記アクセストランジスタの少なくとも一方の各トランジスタのチャネル幅より広いチャネル幅を有する半導体装置。

(もっと読む)

半導体装置

【課題】CMOSインバータを含むメモリセルにおいて、リーク電流によるゲート配線の制約やデザインルールの制約を起因とするメモリセルの面積の増大を抑える。

【解決手段】第1のインバータIV1と第2のインバータIV2を含むメモリセル1Aの第1の金属層として、第1の配線FL1及び第2の配線FL2が配置されている。第1の配線FL1は、第1のインバータIV1の2つのドレインDと第2のインバータIV2の第2のゲート配線GL2と接続している。第2の配線FL2は、第2のインバータIV2の2つのドレインDと第1のインバータIV1の第1のゲート配線GL1と接続している。第1の配線FL1は第2のゲート配線GL2と重畳し、第2の配線FL2は第1のゲート配線GL1と重畳して配置される。第1の金属層よりも上層には、第2の金属層と、その上層の第3の金属層が配置されている。

(もっと読む)

SRAM

【課題】配線不良が生じ難いSRAM。

【解決手段】第1方向に平行に延設された第1、第2ゲート電極と、第1ゲート電極と直交して第1負荷トランジスタを構成する第1拡散領域及び第1の駆動トランジスタを構成する第2拡散領域と、第2拡散領域と直交して第1アクセストランジスタを構成する第3ゲート電極と、第1拡散領域と第2ゲート電極との第1共通コンタクトと、第1及び第3ゲート電極間の第2拡散領域に形成された第1拡散領域コンタクトと、第3ゲート電極に接続された第1ゲートコンタクトと、第1共通コンタクトと第1拡散領域コンタクトとを接続する第1配線と、第1ゲートコンタクトに接続された第2配線と、を備えたSRAM。第1共通コンタクトと第1ゲートコンタクトとが階段状の2層構造を有し、第1及び第2配線はいずれも第1方向を長手方向とする矩形形状を有し、第1の方向の一直線上に並べて配置されている。

(もっと読む)

SRAM

【課題】微細かつリーク電流が抑制されたSRAM。

【解決手段】第1の負荷トランジスタLT1を構成する第1のゲート電極G1bと、第1のゲート電極G1bの長手方向の延長上に、これと離間して延設され、第1の駆動トランジスタDT1を構成する第2のゲート電極G1aと、第1のゲート電極G1bと平行に延設され、第2の負荷トランジスタLT2を構成する第3のゲート電極G1bと、第3のゲート電極G1bと交差して形成され、第2の負荷トランジスタLT2を構成する第1のP型拡散領域PD21と、第1のゲート電極G1b及び第2のゲート電極G1a及び第1のP型拡散領域PD21に跨って形成された第1の共通コンタクトSC2と、を備えるSRAM。第1のP型拡散領域PD21は、第1のゲート電極G1bと第2のゲート電極G1aとの間隙領域近傍まで延設され、かつ、当該間隙領域には形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と拡散層に接続する共通コンタクトにおけるリークを防ぐ。

【解決手段】半導体装置は、拡散層が形成された基板と、基板上に形成されたゲート電極と、基板上にゲート電極よりも高い位置まで形成された第1絶縁層と、拡散層に電気的に接続され、第1絶縁層を貫通する第1コンタクトと、ゲート電極と電気的に接続された第2コンタクトと、第1絶縁層の上に形成された第2絶縁層とを備える。第1コンタクトと第2コンタクトとは第1絶縁層の上面以上の高さにおいて電気的に接続する。ゲート電極上と拡散層上は異なるコンタクトで形成されているため、ゲート電極のサイドウォールが減少することなく、リークを防ぐことができる。

(もっと読む)

設計規則違反を低減するために多重露光及び遮断マスクの手法を用いる半導体デバイス製造

【解決手段】

半導体デバイス(400)を製造する方法は、半導体材質(402)の層及び半導体材質(402)の層の上の絶縁材質(404)の層を備える基板上に、ハードマスク材質(408)の層が絶縁材質(404)の層の上になるように、ハードマスク材質(408)の層を形成することによって開始する。多重露光フォトリソグラフィ手順が実行されて、ハードマスク材質(408)の層の上にフォトレジスト特徴部の結合されたパターンが作製され、またフォトレジスト特徴部の結合されたパターンを用いてハードマスク材質内に凹部線パターンが作製される。方法は、凹部線パターン(422)の指定された区画をフォトレジスト特徴部の遮断パターン(442)で覆い、そして溝(452)のパターンを絶縁材質(404)内に形成することによって継続し、ここで溝(452)のパターンは、フォトレジスト特徴部の遮断パターン(442)及びハードマスク材質(408)によって規定される。その後、電気伝導材質(472)が溝(452)内に堆積させられて、半導体デバイスのための導電線がもたらされる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィーのプロセスマージンを確保すると共に、ゲート電極とコンタクトプラグとの短絡が生じにくい半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、層間絶縁膜114の上に第1の下部開口部115aを有する第1のマスク層115を形成する工程と、第1のマスク層115の上に第1の下部開口部115aを通して層間絶縁膜114を露出する第1の上部開口部116aを有する第2のマスク層116を形成する工程とを備えている。第1の下部開口部115aは、隣接するゲート電極102同士の間に形成され、ゲート電極102と平行な方向に延びる長辺と、ゲート電極102と交差する方向に延びる短辺とを有する平面方形状である。第1の上部開口部116aは、各辺の長さが第1の下部開口部115aの短辺よりも長い平面方形状である。

(もっと読む)

半導体装置及びその製造方法

【課題】読み出しマージンの大きなSRAMセルを提供する。

【解決手段】第1インバータ回路と、出力ノードが前記第1インバータ回路の入力ノードに接続され、入力ノードが前記第1インバータ回路の出力ノードに接続された、第2インバータ回路と、ソース及びドレインの一方が前記第1インバータ回路の出力ノードに接続され、他方がビット線に接続された、第1アクセストランジスタとを具備する。前記第1インバータ回路は、第1トランジスタを含む。前記第1アクセストランジスタ及び前記第1トランジスタのそれぞれは、基板上に形成され、前記基板面に対して垂直に延びる半導体柱と、前記半導体柱を前記基板面に平行な方向で取り囲むように形成され、前記半導体柱にチャネル領域を形成させる、ゲート電極と、前記半導体柱の下端部又は上端部にそれぞれ接続されるソース及びドレインとを備える。前記第1トランジスタの電流駆動力は、前記第1アクセストランジスタのそれよりも高い。

(もっと読む)

重イオン・アップセット硬化浮遊ボディSRAMセル

【課題】ソフトエラーに耐えるSOICMOSSRAMを提供する。

【解決手段】シリコン−オン−絶縁物MOSFETトランジスタを有するCMOSメモリ素子。トランジスタのボディが電源に接続されておらず、その代わりに電気的浮遊を許容するように、MOSFETトランジスタの少なくとも一つが構成されている。重イオン放射によって生じるエラーに対する増加した免疫を備えた開示されたメモリ素子の実施態様。

(もっと読む)

1 - 20 / 74

[ Back to top ]