Fターム[5F083BS47]の内容

Fターム[5F083BS47]に分類される特許

1 - 20 / 57

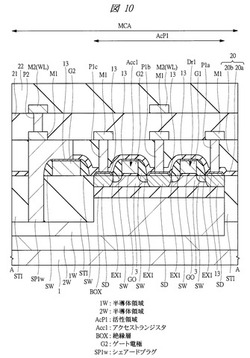

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1が配置される活性領域AcP1の下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wの底部および側部が、n型の半導体領域2Wと接するように配置し、p型の半導体領域1Wをn型の半導体領域2Wでpn分離し、アクセストランジスタAcc1のゲート電極G2とp型の半導体領域1Wを接続する。そして、この接続は、アクセストランジスタAcc1のゲート電極G2の上部からp型の半導体領域1Wの上部まで延在する一体の導電性膜であるシェアードプラグSP1wによりなされる。これにより、アクセストランジスタAcc1がオン状態の場合において、バックゲートであるp型の半導体領域1Wの電位が同時に高くなり、トランジスタのオン電流を大きくできる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体集積回路装置

【課題】本発明は、従来のSRAMメモリセルでは、Pウエル領域の基板へのコンタクトをとるために、拡散層の形を鍵状に曲げる必要があった。このため、対称性が悪く微細化が困難であるという問題があった。

【解決手段】SRAMセルを構成するインバータが形成されたPウエル領域PW1、PW2が2つに分割されてNウエル領域NW1の両側に配置され、トランジスタを形成する拡散層に曲がりがなく、配置方向が、ウエル境界線やビット線に平行に走るように形成される。アレイの途中には、基板への電源を供給するための領域が、メモリセル32ローあるいは、64ロー毎に、ワード線と平行に形成される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクトの接触不良を防止して、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】高密度版回路における電界効果トランジスタTr3のゲート電極G3と電界効果トランジスタTr4のゲート電極G4とのピッチは、高速版回路における電界効果トランジスタTr1のゲート電極G1と電界効果トランジスタTr2のゲート電極G2のピッチよりも小さいが、シェアードコンタクトホールSCが達する部分のゲート電極G3に切欠を設けることにより、シェアードコンタクトホールSCと不純物領域S/Dとの接触面積を広くする。

(もっと読む)

スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定かつ高速に動作する半導体記憶装置を実現する。

【解決手段】メモリセル列ごとにアレイ電源線(ARVD)およびダウン電源線(DWVD)を配置する。ダウン電源線は、読出し時に接地に結合され、書込み時にフローティング状態とされる。書込み時、選択列のアレイ電源線への電源電圧の供給を停止するとともに該アレイ電源線を対応のダウン電源線に接続する。電源系統を複雑化することなく、低電源電圧下においても安定にデータの書込/読出を行うことのできる半導体記憶装置を実現することができる。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

マスタスライス方式メモリセル

【課題】複数種類の回路構成をマスタスライス方式で対応可能なメモリセル専用のマスタスライス方式メモリセルを提供すること。

【解決手段】メモリユニットが2行2列に配置されてメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第3拡散層を備え、各拡散層で並列接続のトランジスタが構成される。第1および第2ワード線は第1〜第3拡散層の両端部外方に配置される。第1〜第3拡散層の第1コンタクト層とゲート層の第2コンタクト層との間、第1コンタクト層と第1/第2ワード線との間に、行方向に沿って第1のメタル配線領域が確保される。第1のメタル配線領域には、第2または第3メタル層の何れかが配線可能である。第1及び第2拡散層、第2及び第3拡散層の間には、列方向に沿って第2のメタル配線領域が確保される。第2のメタル配線領域には第3メタル層が配線可能である。

(もっと読む)

半導体セル構造物、上記半導体セル構造物を含む半導体装置、及び上記半導体装置を含む半導体モジュール

【課題】所定の整列関係を有する単位セルを含む半導体セル構造物を提供すること。

【解決手段】単位セルは、活性領域14、18、24、28、ゲートパターン32、34、36、38、ダミーパターン42、44、46、48、及び導電パターン94を有する。ゲートパターン32、34、36、38は活性領域14、18、24、28と交差する。ダミーパターン42、44、46、48は単位セルを電気的に接続する。選択された単位セル内のダミーパターン42、44、46、48は、選択された単位セル内のゲートパターン32、34、36、38との間に対角的に配置される。導電パターン94はダミーパターン42、44、46、48と電気的に接続する。これにより、半導体セル構造物は、行及び列に沿って互い突出しない単位セルを有することができる。上述した半導体セル構造物は半導体装置及び半導体モジュールに配置される。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置

【課題】SRAMを有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に形成された6つのnチャネル型トランジスタQNA1,QNA2,QNA3,QNA4,QND1,QND2と、2つのpチャネル型トランジスタQPL1,QPL2とによって構成されるメモリセルMC1を有する半導体装置である。シリコン基板1上には、行方向に見て、順に、第1pウェルPW1、第1nウェルNW1、第2pウェルPW2、第2nウェルNW2、および、第3pウェルPW3が配置されている。第1および第2正相アクセストランジスタQNA1,QNA2は第1pウェルPW1に配置され、第1および第2ドライバトランジスタQND1,QND2は第2pウェルPW2に配置され、第1および第2逆相アクセストランジスタQNA3,QNA4は第3pウェルPW3に配置されている。

(もっと読む)

半導体装置の製造方法、フラッシュメモリの製造方法、およびスタティックランダムアクセスメモリの製造方法ならびにフラッシュメモリ

【課題】同一のレジストパターンにより、ドライエッチングおよびウエットエッチングを連続的に行なう際に、変質したレジスト表面層を剥がれなくするように改良された、半導体装置の製造方法を提供することを主要な目的とする。

【解決手段】半導体基板1の上に、絶縁膜2と導電層3を順次形成する。導電層3の上にレジストパターン4を形成する。レジストパターン4をマスクに用いて、導電層3をドライエッチングする。レジストパターン4の表層部を一部削る。レジストパターン4をマスクに用いて、絶縁膜2をウエットエッチングする。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】回路構成を複雑化することなくソフトエラー低減化を図ったメモリセル構造を有する半導体記憶装置を得る。

【解決手段】NMOSトランジスタN1及びPMOSトランジスタP1によるインバータI1(出力部が記憶端子Na)とNMOSトランジスタN2及びPMOSトランジスタP2によるインバータI2(出力部が記憶端子Nb)とが交叉接続され、さらにNMOSトランジスタN3及びN4が記憶端子Na及びNbにそれぞれ接続される。記憶端子Naに一方電極が接続されるNMOSトランジスタN1及びN3はPウエル領域PW0及びPW1に分けて形成されるともに、記憶端子Nbに一方電極が接続されるNMOSトランジスタN2及びN4はPウエル領域PW1及びPW0に分けて形成される。Pウエル領域PW0及びPW1はNウエル領域NWを挟んで各々反対側に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置

【課題】CAMにおけるメモリセル面積の縮小化を図る。

【解決手段】データ線(D0,D1)を第1記憶部(MA)及び第2記憶部(MB)とで共有し、また、第1比較データ線(CD0)に結合された第1トランジスタ(MC0)と、第1記憶部の記憶ノードに結合された第2トランジスタ(MCA)とを直列接続して第1比較回路(11)を形成し、第2比較データ線(CD1)に結合された第3トランジスタ(MC1)と、上記第2記憶部の記憶ノードに結合された第4トランジスタ(MCB)とを直列接続して第2比較回路(12)を形成することは、拡散層や配線層のレイアウトにおける対称性を向上させ、メモリセルをその中心を通る中心線に対して線対称となるレイアウトの容易化を達成する。それにより製造プロセス条件を最適化し易くなり、製造プロセスのばらつきが低減されてメモリセルの微細化が達成される。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

1 - 20 / 57

[ Back to top ]