Fターム[5F083CR11]の内容

半導体メモリ (164,393) | ROM(EPROM、EEPROMを除く) (635) | PROM(Programmable ROM) (484)

Fターム[5F083CR11]の下位に属するFターム

ヒューズROM (99)

PN接合破壊型ROM (22)

絶縁膜破壊型ROM (178)

抵抗値変化型ROM (100)

電気的手段によらないで書き込むもの (50)

Fターム[5F083CR11]に分類される特許

1 - 20 / 35

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく

、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトラ

ンジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジ

スタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の

端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導

体記憶装置である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルを微細化しても、抵抗変化動作に十分な電流を流すことが可能なダイオードを備える抵抗変化型の不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、X方向に延在する第1配線13と、Y方向に延在する第2配線20と、第1配線13と第2配線20との交点に設けられたメモリセル10とを具備する。メモリセル10は、第1配線13上に設けられ一端を第1配線13に接続されたダイオード15と、ダイオード15上方に設けられ一端をダイオード15に直列接続され、他端を第2配線20に接続され、抵抗値の変化で情報を記憶する抵抗変化部19とを備えている。ダイオード15は、第1導電型の第1半導体層13と、第2導電型で、第1半導体層13の内部に伸びている第2半導体層14とを含んでいる。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】簡単な構成で、複数の積層チップパッケージを積層し互いに電気的に接続することを可能にし、所望の数の半導体チップを含むパッケージを低コストで実現する。

【解決手段】積層チップパッケージ1Sは、本体2を備え、本体2は、主要部分2Mと、主要部分2Mの上面、下面に配置された複数の第1の端子4、第2の端子5を有している。主要部分2Mは、2つの階層部分10S1,10S2と、これらを貫通する複数の貫通電極Tを含んでいる。複数の貫通電極Tは、複数の端子4,5に電気的に接続されている。各階層部分は、第1の面と第2の面を有する半導体チップと、複数の表面電極を含んでいる。階層部分10S1,10S2は、第2の面同士が対向するように接合されている。端子4は階層部分10S1の表面電極を用いて構成され、端子5は階層部分10S2の表面電極を用いて構成されている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】パッケージの端子数の増加と、ベースチップのI/O領域の増加を抑制する構造体を提供する。

【解決手段】複数の外部導出配線と、マスクROM領域、内部バス、複数のバス接続端子、および複数の外部接続端子を有する半導体集積回路基板と、この半導体集積回路基板上に積層され、複数のROM接続端子を持つプログラマブルROM15と、を備えた半導体集積回路装置において、複数の外部導出配線の一部、半導体集積回路基板、プログラマブルROM15、複数の外部接続端子と複数の外部導出配線との電気的接続、および複数のバス接続端子と複数のROM接続端子との電気的接続のそれぞれが同一半導体パッケージ内に封止されている。

(もっと読む)

記憶素子および記憶装置

【課題】複数の記憶素子の初期状態もしくは消去状態の抵抗値のバラツキを低減すると共に、複数回の書き込み・消去動作に対して書き込み・消去時の抵抗値を保持することが可能な記憶素子および記憶装置を提供する。

【解決手段】記憶層20に、酸化ガドリニウム(Gd−O)よりなる第1高抵抗層22Aと、酸化アルミニウム(Al−O)または酸化シリコン(Si−O)よりなる第2高抵抗層22Bとを設ける。第1高抵抗層22Aに存在する欠陥を第2高抵抗層22Bにより補完し、構造の均一性を向上させ、複数の記憶素子1の初期状態または消去状態の抵抗値のバラツキを低減する。書き込み・消去動作を繰り返し行った場合に、欠陥の増殖を抑え、複数回の書き込み・消去動作に対する抵抗値保持特性を向上させる。

(もっと読む)

半導体記憶装置

【課題】メモリセルの集積度が高く製造コストが低い1回書込型の半導体記憶装置を提供する。

【解決手段】1回書込型の半導体記憶装置において、シリコン基板上に積層体が設けられている。この積層体においては、それぞれ複数の層間絶縁膜及び電極膜WLが交互に積層され、積層方向に延びる貫通ホール17が形成されている。貫通ホール17の内面上には、膜厚が4nm以上である電極側絶縁膜25と、電荷蓄積膜26と、膜厚が4nm以上である半導体側絶縁膜27とがこの順に積層されており、貫通ホール17の内部にはシリコンピラーSPが埋設されている。電極側絶縁膜25及び半導体側絶縁膜27は共にシリコン酸化物からなり、電極側絶縁膜25の膜厚は半導体側絶縁膜27の膜厚よりも薄い。

(もっと読む)

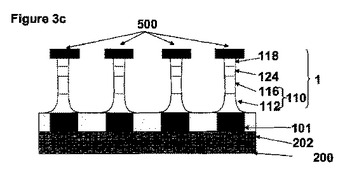

丸いコーナーを有する複数の柱を備えるクロスポイント形不揮発性メモリ装置およびその製造方法

不揮発性メモリ装置が複数の柱(1)を備え、複数の柱のそれぞれは、ステアリング素子(110)および記憶素子(118)を含む不揮発性メモリセルを備え、複数の柱のそれぞれのトップコーナーまたはボトムコーナーの少なくとも一方が丸くされる。不揮発性メモリ装置を製作する方法が、装置層のスタックを形成すること、およびこのスタックをパターン形成して複数の柱を形成することを含み、複数の柱のそれぞれは、ステアリング素子および記憶素子を含む不揮発性メモリセルを備え、複数の柱のそれぞれのトップコーナーまたはボトムコーナーの少なくとも一方が丸くされる。  (もっと読む)

(もっと読む)

不揮発性半導体メモリ装置

【課題】複数のOTPを備え、アクセス速度を改善した擬似MTPの機能を有する不揮発性半導体メモリ装置を提供する。

【解決手段】不揮発性半導体メモリ装置100sは、記憶領域132sと、セレクトデコーダ131sと、セレクトアドレス処理部12sとを備え、記憶領域132sがnビット幅(n>1)の記憶素子をm+1個有し、セレクトデコーダ131sが記憶領域132sのうちいずれか1つの記憶素子に記憶されるセレクトアドレスに応じて、他のm個の記憶素子のいずれか1つを選択し、セレクトアドレス処理部12sが、記憶領域132sにデータを書き込むとき、セレクトアドレスを更新して、更新したセレクトアドレスをセレクトデコーダ131sに出力する。

(もっと読む)

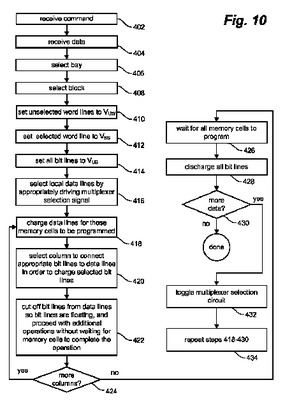

不揮発性メモリの連続的なプログラミング

不揮発性記憶素子は、信号ドライバを第1の不揮発性記憶素子に接続された第1の制御線に接続し、信号ドライバが第1の制御線に接続されている間に信号ドライバを用いて第1の制御線を充電し、第1の制御線が信号ドライバから充電された状態を維持している間に信号ドライバを第1の制御線から切断し、信号ドライバを第2の不揮発性記憶素子に接続された第2の制御線に接続し、信号ドライバが第2の制御線に接続されている間に信号ドライバを用いて第2の制御線を充電し、信号ドライバを第2の制御線から切断する。制御線を充電するステップは、不揮発性記憶素子の各々に、プログラム処理を起こさせる。信号ドライバを第1の制御線から切断するステップ、信号ドライバを第1の制御線に接続するステップ、および第2の制御線を充電するステップは、第1の不揮発性記憶素子のプログラム処理の完了を待たずに行われる。  (もっと読む)

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】標準ロジックのCMOSプロセスで不揮発性メモリを実現し、メモリセルの面積を最小限にすると共に、OTPおよびMTPを実現する。

【解決手段】トランジスタ形成部3を上下方向に配置し、トランジスタ形成部3の左側にメタル配線12を配置しドレインと接続する。また、ソースに接続されるメタル配線13を左右方向に配置する。またトランジスタ形成部3の左側にn型ウェル2を配置し、このn型ウェル2の表面とトランジスタのゲート領域部(符号4で示す領域)とに対向するようにフローティングゲート9を左右方向に配置し、フローティングゲート9に電位を付与するコントロールゲート配線19も左右方向に配置する。そして、ドレインDとコントロールゲートCGとソースSに印加する信号を制御することにより、このメモリセルをOTPまたはMTPとして動作させる。

(もっと読む)

半導体記憶装置の製造方法および半導体記憶装置

【課題】ROMを形成する強誘電体メモリのダイナミック/スタティック・インプリント現象に対するデータ読み出しマージンを改善することのできる半導体記憶装置の製造方法および半導体記憶装置を提供する。

【解決手段】ROMを形成する強誘電体メモリに対し、ROMデータと逆極性のデータを書き込みを行って(工程S01)、所定時間のベーク処理を実行し(工程S02)、その後、ROMデータを書き込む(工程S03)。

(もっと読む)

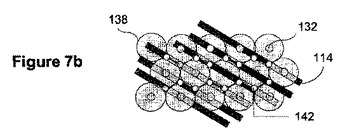

三角形二次元相補的柱パターニング

半導体デバイスを作る方法は、基板上に少なくとも1つのデバイス層を形成することと、デバイス層上に複数の相隔たる第1のフィーチャを形成することであって、それぞれ3つの隣接する第1のフィーチャは正三角形を形成することと、第1のフィーチャ上にサイドウォールスペーサを形成することと、複数の充填フィーチャによりサイドウォールスペーサ間の空間を充填することと、サイドウォールスペーサを選択的に除去することと、少なくとも複数の充填フィーチャをマスクとして使用して少なくとも1つのデバイス層をエッチングすることとを含む。デバイスは、基板上に位置する複数の底部電極と、複数の底部電極上で相隔たる複数の柱と、複数の柱と接触する複数の頂部電極とを備える。それぞれ3つの隣接する柱は正三角形を形成し、それぞれの柱は半導体デバイスをなす。複数の柱は、第1の形状を有する複数の第1の柱と、第1の形状とは異なる第2の形状を有する第2の柱とを含む。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】電気的に書き換えが不可能な不揮発性メモリを内蔵した半導体集積回路において、データの更新、不揮発性メモリの再利用を可能にする。

【解決手段】不揮発性メモリを複数のブロックに分割して、ブロックを使い捨てにする形で、不揮発性メモリのデータの更新、不揮発性メモリの再利用を可能にしたものである。即ち、あるブロックの第1のフラグがデータ「1」の場合には、当該ブロックはすでにデータが書き込まれ、再書き込みが不能であるとブロック選択回路13によって判定される。データを更新したい場合には、残りのブロックがブロック選択回路13によって選択され、そのブロックに更新されたデータが書き込まれる。この時、そのブロックの第2のフラグをデータ「1」に設定する。こうして、次々とデータを更新していき、あるブロックに最終的な更新データが書き込まれた場合に、そのブロックの第2のフラグをデータ「1」に設定する。

(もっと読む)

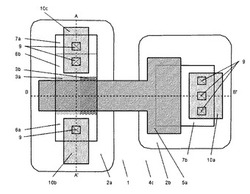

2つの結合された層を用いたプログラマブルROM及び動作方法

3D集積素子(10)として実施された読み出し専用メモリは、第1の層(10’)、第2の層(10’’)及び該第1の層を該第2の層に結合する結合層間接続(28、30、32、34、36、38)を有する。2つの層の間の物理的結合は、読み出し専用メモリのプログラミングを実施する。層はウエハ形式又はダイ形式であってもよい。第1の層は、機能能動素子(26、27、46、48、49)及び少なくとも1つの未プログラミング能動素子(40、41、42、43)を有する。第2の層は、少なくとも1つの未プログラミング能動素子に関連付けられる少なくとも導電性経路(16、17)を有する。結合層間接続は、少なくとも1つの未プログラミング能動素子をプログラミングするために及び導電性経路をプログラミング済み能動素子に提供するために、少なくとも1つの結合されたプログラマブル層間接続(32、34、36、38)を有する。従って、2つの層は、プログラミングされたROMを形成する。2つの層を結合することにより他の種類のプログラマブル記憶素子が実施されてもよい。  (もっと読む)

(もっと読む)

積層メモリ装置

【課題】積層メモリ装置を提供する。

【解決手段】積層メモリ装置において、2つ以上のメモリ部と、メモリ部間に形成されたものであり、デコーダを有する能動回路部とを備える積層メモリ装置である。

(もっと読む)

記憶装置及びその作製方法、半導体装置

【課題】記憶装置の作製工程を簡略化することにより製造コストを低減し、より安価な記憶装置を提供することを課題とする。

【解決手段】電極として機能する二つの導電層(金属層)を接触させ、界面領域を腐食(酸化ともいう)させることにより、電気抵抗が高い領域を形成する。該高抵抗領域は、異種金属を接触させた場合に、イオン化傾向が大きい金属が腐食しやすくなるという性質を利用して形成するものである。これにより、電極間に絶縁層や半導体層を別途設けることなく、記憶素子を作製することができる。つまり、製造工程を簡略化して製造コストを低減した記憶装置を提供することができる。

(もっと読む)

半導体集積回路装置及び半導体集積回路装置の製造方法

【課題】製造過程において半導体記憶素子の書き込みテストを行うことができる半導体集積回路を提供する。

【解決手段】光照射によりデータの記憶状態が変化するPROM22が形成された基板10と、基板10のPROM22が形成された面側に形成された多層配線構造70と、を備え、多層配線構造70に、PROM22が形成されたPROM領域20に対向する位置に透光性材料により形成され、多層配線構造70の外部からPROM22への光導入路とされる透光領域80と、透光領域80の周囲に、複数層の遮光性材料により連続的に形成された遮光領域30と、透光領域80からみて遮光領域30を介して外側に形成され、PROM22の記憶状態を操作するためのPAD部60と、を備えた。

(もっと読む)

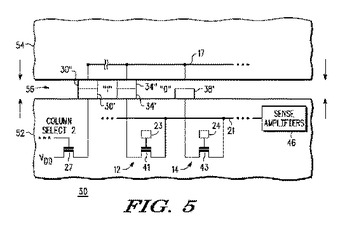

低電圧、低キャパシタンスのフラッシュメモリアレイ

【課題】メモリセルを読み出すときは低キャパシタンスで、比較的低電圧で使用可能な構造のフラッシュメモリアレイを提供する。

【解決手段】p型フラッシュメモリアレイで、プログラミングビットライン及び読み出しビットラインが別個に提供される。プログラミングビットラインは、そのビットラインに接続したメモリセル内のフローティングゲートトランジスタをプログラムするときにのみ使用され、読み出しビットラインは、メモリ回路動作中に、そのビットラインに接続した選択メモリセル内のフローティングゲートトランジスタの状態を読み出すときにのみ使用される。プログラミング中及びメモリアレイ動作中に低電圧で使用可能な構造であり、従来の比較的低電圧のp型フラッシュメモリ構造で、メモリセルの読み出し中に各ビットラインに関連して可変し予測不可能であったキャパシタンスを排除するような構造である。

(もっと読む)

1 - 20 / 35

[ Back to top ]