Fターム[5F083CR17]の内容

半導体メモリ (164,393) | ROM(EPROM、EEPROMを除く) (635) | PROM(Programmable ROM) (484) | 電気的手段によらないで書き込むもの (50) | レーザービームの照射による書き込み (43)

Fターム[5F083CR17]に分類される特許

1 - 20 / 43

半導体装置

【課題】コイル状のアンテナ部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給することが困難になっていた。

【解決手段】記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電力化を図ることができる。また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、スペースを有効に利用することができる。従って、半導体装置の小型化を実現することができる。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

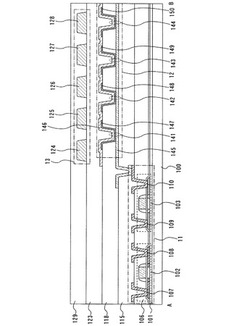

半導体記憶装置

【課題】DRAMの回路規模や信号伝搬時間を抑制する。

【解決手段】半導体記憶装置には、不良なメモリセルのアドレスを記憶するためのヒューズ素子120が配列されるヒューズ領域116が形成される。ヒューズ領域116のまわりにはガードリング118が形成され、ガードリング118はパッシベーション膜124によって覆われる。ただし、ヒューズ領域116の上のパッシベーション膜124には開口部126が設けられる。ガードリング118は、第1層128の第1リング134、第2層130の第2リング136および第3層132の第3リング138とそれらを接続する第1接続リング142、第2接続リング144を含む。ここで、第2リング136の下に第1リング134の非形成領域が確保されるように、第1リング134を第2リング136の内側に配置する。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

半導体装置

【課題】製造時以外にデータの書き込みが可能であり、書き換えによる偽造を防止可能な半導体装置を提供することを目的とする。さらに、本発明は、単純な構造の有機メモリから構成される安価な半導体装置の提供を課題とする。

【解決手段】有機化合物層を有する有機素子にトランジスタを並列または直列に接続したメモリセルを構成し、そのメモリセルを直列または並列に接続することによって、NAND型メモリまたはNOR型メモリを構成する。

前記有機素子は電流または電圧の印加、光の照射などで不可逆的にその電気特性を変化さ

せることができる。

(もっと読む)

半導体集積回路および電子機器

【課題】不揮発性記憶素子にフューズ素子を用いた半導体集積回路において、目的とするデータと、検査データとしての目的とするデータの論理否定データとを記憶し、フューズ素子の不可逆性を利用することで、記憶回路と検証回路の回路規模をあまり大きくすることなく、またデータ検証の処理時間の増大を招くことなく、記憶データの信頼性と正真性を保証する。

【解決手段】記憶すべき情報を示す特定データを不可逆的に記憶する不揮発性記憶回路100aを有する半導体集積回路100において、該不揮発性記憶回路100aを、該特定データの非反転データを記憶する第1の記憶回路101と、該特定データの反転データを記憶する第2の記憶回路102とを有する構成とした。

(もっと読む)

通信システム及び通信方法

【課題】不揮発性であって、作製工程が簡単であり、追記が可能な記憶回路およびアンテ

ナを有する半導体装置及びその作製方法の提供を課題とし、さらに不本意な無線チップの

情報の書き換え防止や、無線チップ自体の偽造防止を図り、無線チップのセキュリティの

確保を課題とする。

【解決手段】無線通信信号により情報確認が可能なICタグであり、且つ、ICタグのメ

モリ(書き換え不可能なメモリ)の情報確認が光学読み取り装置でも可能とすることを特

徴とする。本発明のICタグのメモリには情報確認が光学読み取り装置で可能な識別面を

有している。

(もっと読む)

半導体装置

【課題】本発明は、安価な半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、相変化メモリと、電磁波を交流の電気信号に変換するアンテナと、アンテナから供給される交流の電気信号を基に電源電位を生成し、生成した電源電位を相変化メモリに供給する電源回路を有する。相変化メモリは、第1の方向に延在するビット線、第1の方向と垂直な第2の方向に延在するワード線及びビット線とワード線の間に設けられた相変化層を有する。

(もっと読む)

半導体装置の作製方法

【課題】不揮発性であって、作成が簡単であり、追記が可能な記憶回路を有する半導体装

置及びその作製方法の提供を課題とする。

【解決手段】一対の導電層間に有機化合物層が挟まれた単純な構造の記憶素子を有する半

導体装置及びその作製方法を提供する。また、不揮発性であり、作製が簡単であり、追記

が可能な記憶回路を有する半導体装置及びその作製方法を提供する。絶縁層上に設けられ

た複数の電界効果トランジスタと、複数の電界効果トランジスタ上に設けられた複数の記

憶素子とを有する。複数の電界効果トランジスタは、単結晶半導体層をチャネル部とした

電界効果トランジスタである。複数の記憶素子の各々は、第1の導電層と、有機化合物層

と、第2の導電層が順に積層された素子である。

(もっと読む)

半導体装置

【課題】製造時以外にデータの書き込みが可能であり、書き換えによる偽造を防止可能な半導体装置を提供することを目的とする。さらに、本発明は、単純な構造のメモリから構成される安価な半導体装置の提供を課題とする。

【解決手段】単結晶半導体基板上に形成された電界効果トランジスタと、電界効果トラン

ジスタの上に設けられた第1の導電層と、第1の導電層上に設けられた有機化合物層と、

有機化合物層上に設けられた第2の導電層とを有し、第1の導電層と有機化合物と前記第

2の導電層とで記憶素子を構成する。また、上記構成において、アンテナを具備すること

によって、非接触でデータの送受信が可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】アンチヒューズ素子セットAFSETに含まれるデコーダ回路の数を抑制する。

【解決手段】アンチヒューズ素子セットAFSETのビット記憶回路BMは、プログラム電圧が印加されたときに絶縁状態から導通状態へ変化する2つのアンチヒューズ素子AFを含む。この2つのアンチヒューズ素子AFの論理状態により、1ビット分のデータを表現する。2つのアンチヒューズ素子AFは、1つのデコーダ回路160により一元的に制御される。データ記録に際しては、デコーダ回路160は2つのアンチヒューズ素子AFを同時にプログラム電圧ライン16a、16bと接続することにより、2つのアンチヒューズ素子AFを同時に絶縁破壊する。

(もっと読む)

半導体装置及びその製造方法

【課題】不良アドレス1ビット分を一対のアンチヒューズ素子に記憶させる半導体装置において、一方のアンチヒューズ素子のみが不良品である場合であっても、不良品として検出できるようにする。

【解決手段】半導体装置10は、それぞれハイレベル及びローレベルのうちのいずれか一方にある一対のアンチヒューズ素子51A,51Bと、これらのうちの少なくとも一方がハイレベルにある場合と、両方がローレベルにある場合とで異なる論理情報を出力するオア回路56と、これらの論理状態が互いに異なる場合と、互いに同一である場合とで異なる論理情報を出力するエクスクルーシブオア回路58とを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】高集積化が容易で製造コストが増加しないヒューズ回路を有する半導体装置の構造及びその製造方法、並びに、このようなヒューズの切断に適したレーザ装置を提供する。

【解決手段】下地基板10上に形成されたブロック層12と、ブロック層12上に形成された絶縁膜14と、絶縁膜14上に形成されたヒューズ22とにより半導体装置を構成する。ヒューズ22の下層部にブロック層12を設けることにより、レーザアブレーションによりヒューズを切断し、且つ、ブロック層12によってレーザアブレーションを制御性よく停止することができる。

(もっと読む)

半導体装置

【課題】簡単な構成で多機能化を図った記憶回路を有する半導体装置を提供する。

【解決手段】複数のメモリセルのそれぞれは、第1と第2記憶ノードに交差接続された入力と出力がそれぞれ接続された第1と第2インバータ回路と、第1と第2記憶ノードと第1と第2入出力端子との間にそれぞれ設けられた第1、第2スイッチMOSFETと、第1記憶ノードと第3記憶ノードの間に設けられた第3スイッチMOSFETとを有する。第1と第2記憶ノードは、第1と第2入出力端子からの第1記憶情報が書き込み/読み出し可能にされる。第3記憶ノードは、第2記憶情報に対応して電源電圧又は接地電位が定常的に供給される。第3記憶ノードの記憶情報は、第3スイッチMOSFETをオン状態にして第1、第2記憶ノードに伝えられる。第1、第2スイッチMOSFETを介して第1と第2端子から読み出し可能にされる。

(もっと読む)

半導体装置、半導体集積回路装置及び半導体装置の電気的特性の調整方法

【課題】互いに独立した複数の回路を搭載した半導体装置において、回路毎に適切な電気的特性の調整を行うことができる半導体装置及び半導体装置の電気的特性の調整方法の提供。

【解決手段】互いに独立した第1の回路10及び第2の回路を有し、前記第1の回路10はパッケージング前に電気的特性が調整され、前記第2の回路20はパッケージング後に電気的特性が調整される半導体装置60であって、前記第1の回路10は、レーザー切断により抵抗値が調整されるレーザーヒューズ30を有し、前記第2の回路20は、電気的溶断により抵抗値が調整される電気溶断式抵抗調整手段を有することを特徴とする。

(もっと読む)

トンネル障壁を有する記憶装置並びにこの記憶装置内での情報の書込みおよび読出し方法

本発明は、トンネル障壁を有する抵抗型記憶装置を提供する。トンネル障壁は、メモリ材料と接触しており、このメモリ材料は、書込み信号によって変化するメモリ特性を有する。トンネル障壁のパラメータへのトンネル抵抗の指数的な関係に基づいて、メモリ特性の変化はトンネル抵抗に強く介入し、そのことで、メモリ材料中に格納された情報を読み出すことができる。例えば固体電解質(イオン伝導体)が記憶層として適しており、そのイオンは、書込み信号によって、トンネル障壁との境界面に相対して移動することができる。しかしながら記憶層は、書込み信号によって、例えばこのトンネル障壁内に存在する金属膜の移動によってそのトンネル抵抗が変化する別のトンネル障壁などでもあり得る。本発明は、記憶装置内での情報の格納方法および読出し方法をも提供する。  (もっと読む)

(もっと読む)

円偏光発光性ナノ微粒子

【課題】円偏光発光特性を示す化合物半導体ナノ微粒子を提供する。

【解決手段】籠状タンパク質であるフェリチンのコア内で調整したCdSが高い円偏光発光(CPL)を示す。また、この円偏光発光(CPL)の波長は、レーザ照射により調整することができ、これによりバイオナノテクノロジー分野における化合物半導体のナノ微粒子の利用として、WORM(Write-Once Read-Many times)メモリの創成など利用可能となる。なお、籠状タンパク質は、空洞が形成されたタンパク質であり、アポフェリチンなどのフェリチンタンパク質ファミリーやその組み換え体を用いることができる。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ配線部の開口工程において、ヒューズ配線にダメージを与えて誤切断してしまうことを防ぐ。

【解決手段】ヒューズ配線6上の開口部17下にて、SiCN膜からなる保護膜11とプラズマCVD法によって成膜された窒化シリコン膜または酸化シリコン膜からなる保護膜18とが積層された構造を形成することにより、ヒューズ配線6上のシード膜23およびバリア導電膜22をウエットエッチングする際の洗浄液のヒューズ配線6への浸入を保護膜18にて防ぐ。

(もっと読む)

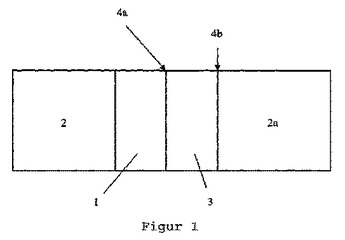

半導体装置、及びその製造方法

【課題】素子パターン寸法が微細化されたときでも、ヒューズ層を適切に、かつ、容易に切断することができ、生産性を向上させることが可能な半導体装置、及びその製造方法を提供する。

【解決手段】絶縁膜2と、絶縁膜2上で所定の間隔をおいて互いに平行に形成されるとともに、レーザー光が照射されることによって切断可能に各々構成された複数のヒューズ層4を備えた半導体集積回路装置(半導体装置)1であって、絶縁膜2において、複数の各ヒューズ層4における、レーザー光が照射される照射部分の少なくとも下方に凹部2bを形成し、この凹部2bを跨ぐように、複数の各ヒューズ層4を形成するとともに、当該凹部2bの上方に、凹部2bの形状に応じた凹み4dを各ヒューズ層4に形成する。

(もっと読む)

1 - 20 / 43

[ Back to top ]