Fターム[5F083EP02]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | FGを有するもの (3,098)

Fターム[5F083EP02]の下位に属するFターム

Fターム[5F083EP02]に分類される特許

1 - 20 / 2,151

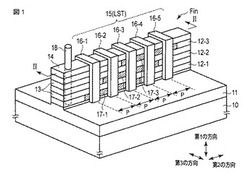

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物を低減する。また、酸化物半導体膜の被形成面近傍の結晶性を向上させる。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】シリコンを含む下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも酸化物半導体膜と重畳する領域に設けられたゲート電極と、酸化物半導体膜に電気的に接続されたソース電極、及びドレイン電極と、を有し、酸化物半導体膜は、下地絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度で分布する領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

(もっと読む)

半導体装置の製造方法および半導体装置

【目的】配線間のコンタクト配置において配線間距離をより小さく形成する。

【構成】実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、第1と第2の配線を覆うように形成される。第2の絶縁膜は、第1と第2の制御ゲート線間の所定位置で第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】パンチスルーを抑制しつつ、セレクトゲート電極からのフリンジ電界を低減する。

【解決手段】空隙AG1は、制御ゲート電極8およびセレクトゲート電極12下に潜るようにしてトレンチ2に沿って連続して形成され、セレクトゲートトランジスタのドレイン領域間に達している。そして、セレクトゲートトランジスタのドレイン領域間において、空隙AG1が埋め戻し絶縁膜RBにて埋め戻されている。

(もっと読む)

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

不揮発性メモリーセル

【課題】種々の回路ブロックを単一の集積回路(IC)に集約するために、不揮発性メモリーブロックをロジック機能ブロックにまとめる。

【解決手段】結合素子と第一のセレクトトランジスターを有している。結合素子は第一の伝導領域において形成されている。第一のセレクトトランジスターは、第一の浮遊ゲートトランジスターおよび第二のセレクトトランジスターに直列的に接続されており、それらは全て第二の伝導領域に形成されている。結合素子の電極および第一の浮遊ゲートトランジスターのゲートは、モノリシックに形成された浮遊ゲートである。第二の伝導領域は第一の伝導領域と第三の伝導領域の間に形成され、第一の伝導領域、第二の伝導領域、および第三の伝導領域は、ウェルである。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気的特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】チャネル形成領域、及びチャネル形成領域を挟む低抵抗領域を含む酸化物半導体膜、ゲート絶縁膜、及び上面及び側面を覆う酸化アルミニウム膜を含む絶縁膜が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び酸化アルミニウム膜を含む絶縁膜の上面及び側面の一部に接して設けられる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜近傍の酸化物半導体膜に含まれる不純物元素濃度を低減する。また、ゲート絶縁膜近傍の酸化物半導体膜の結晶性を向上させる。また、当該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極、及びドレイン電極と、酸化物半導体膜、ソース電極、及びドレイン電極上に形成されたシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記酸化物半導体膜と重畳する領域に設けられたゲート電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度である領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体記憶装置

【課題】動作の安定性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、複数のメモリセルと、複数のワード線と、複数のビット線と、複数の選択トランジスタと、配線層と、を備える。複数のメモリセルは、第1方向及び第1方向と直交する第2方向にそれぞれ配置される。複数のワード線は、それぞれ第1方向に延在して設けられる。複数のビット線は、それぞれ第2方向に延在し、第1方向及び第2方向と直交する第3方向に複数のワード線と離間して設けられる。複数の選択トランジスタは、複数のストリングにそれぞれ設けられる。配線層は、選択トランジスタのソースと同電位に設けられる。配線層は、第3方向にみて複数のワード線とそれぞれ重なる複数の第1重複部分を有する。配線層のパターンが繰り返される単位領域において、複数の第1重複部分のそれぞれの面積は同じである。

(もっと読む)

半導体装置の製造方法

【課題】デバイス特性の向上を図る。

【解決手段】本実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法においては、半導体層10上に、トンネル絶縁膜11を形成する。トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜12を形成する。第1導電膜、トンネル絶縁膜、および半導体層を加工することにより、溝15を形成する。溝内の下部側に、第1犠牲膜17を埋め込む。溝内の第1犠牲膜上に、その上面がトンネル絶縁膜の上面よりも高く、第1導電膜の上面よりも低くなるように、第1犠牲膜よりも高密度な第2犠牲膜18を形成する。第1導電膜上および第2犠牲膜上に、絶縁膜19を形成する。絶縁膜上に制御ゲート電極となる第2導電膜WLを形成する。第2導電膜を加工することにより、第2犠牲膜を露出する。第1犠牲膜および第2犠牲膜を除去する。

(もっと読む)

半導体装置、メモリカード、データ処理システムおよび半導体装置の製造方法

【課題】歩留まりや信頼性の低下を招くことなく、隣接セルのフローティング・ゲート間の結合容量を小さくすることができ、隣接セルの書き込み情報の影響を小さくした状態でフローティング・ゲートの電位を制御することが可能なNAND型フラッシュメモリを提供する。

【解決手段】一導電型の半導体材料層表面のチャネル領域上方に第2の絶縁膜12を介して形成されたゲート電極部と、ゲート電極部の上方に前記ゲート電極部と一体形成されたキャパシタ電極部と含むフローティング・ゲート13と、キャパシタ電極部の側面を囲むように第1の絶縁膜12を介して形成されたコントロールゲート10となる第1の電極と、を有する。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

窒化シリコン膜の成膜方法、不揮発性記憶装置の製造方法

【課題】面内方向での膜厚の均一性に優れ、電荷保持特性に優れた窒化シリコン膜の成膜方法、及び窒化シリコン膜を備えた不揮発性記憶装置の製造方法を提供する。

【解決手段】半導体基板上に第2の窒化シリコン膜を形成する工程と、第2の窒化シリコン膜上に第2の窒化シリコン膜よりも光学吸収係数が大きくかつ光学吸収係数kが0.60〜1.26の第1の窒化シリコン膜を、ステップ成膜法により形成する工程と、を有する窒化シリコン膜の成膜方法。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

1 - 20 / 2,151

[ Back to top ]