Fターム[5F083EP47]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 絶縁膜 (4,144) | ゲート絶縁膜 (1,132)

Fターム[5F083EP47]の下位に属するFターム

Fターム[5F083EP47]に分類される特許

1 - 9 / 9

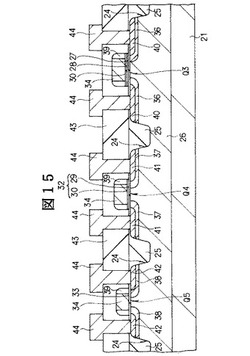

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが異なる複数種類の電界効果トランジスタを有する半導体集積回路装置の信頼性を高める。

【解決手段】第1の電界効果トランジスタQ3及び第2の電界効果トランジスタQ4は埋込絶縁膜25によって分離され、ゲート絶縁膜31,32は各々熱酸化膜27、30と堆積膜27,28,29が積層され、第1の電界効果トランジスタの熱酸化膜は第2の電界効果トランジスタの熱酸化膜より厚く、各トランジスタの堆積膜は、各々各トランジスタの熱酸化膜よりも厚く構成され、第1の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ端部と埋込絶縁膜との間に第1の電界効果トランジスタの堆積膜が設けられ、第2の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ前記端部と埋込絶縁膜との間に第2の電界効果トランジスタの堆積膜が設けられる。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】ビット線方向のセル間干渉を解消する不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1と、半導体基板1を複数の素子領域に分離する素子分離絶縁膜2と、半導体基板1の素子領域上に形成されたトンネル絶縁膜3と、トンネル絶縁膜3上に形成されたフローティングゲート電極4と、積層絶縁膜5を介して、フローティングゲート電極4上及びチャネル幅方向に隣接するフローティングゲート電極4間に形成された第1コントロールゲート電極6と、半導体基板1の素子領域のチャネル幅方向に面する側面に形成されたアシスト絶縁膜7と、アシスト絶縁膜7を介して、複数の素子領域間に形成された第2コントロールゲート電極8と、を備えている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】電荷蓄積膜を備える半導体記憶装置に関し、電荷蓄積膜の電荷保持特性を向上させる。

【解決手段】ビット線とワード線とを有する半導体記憶装置(101)は、基板(111)と、前記基板上に形成された第1のゲート絶縁膜(121)と、前記第1のゲート絶縁膜上に形成された電荷蓄積膜(122)と、前記電荷蓄積膜上に形成された第2のゲート絶縁膜(123)と、前記第2のゲート絶縁膜上に形成されたゲート電極(124)とを備え、前記電荷蓄積膜のビット線方向の幅が、前記ゲート電極のビット線方向の幅よりも狭くなっている、又は、前記電荷蓄積膜のワード線方向の幅が、前記第1のゲート絶縁膜下の前記基板内に形成されるチャネル領域のチャネル幅よりも狭くなっている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】耐圧が改善され、信頼性が向上した不揮発性半導体メモリ及びその製造方法を与える。

【解決手段】半導体記憶装置は、半導体基板11上に形成され、オキシナイトライド化された第1ゲート絶縁膜14aを含む第1トランジスタと、半導体基板11上に形成された第2ゲート絶縁膜14bと、第2ゲート絶縁膜14b上の少なくとも一部に形成されたバリア膜20を含む第2トランジスタとを備え、前記第2ゲート絶縁膜は、前記第1ゲート絶縁膜より窒素原子濃度が低いことを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】不揮発性メモリトランジスタの電荷保持特性を向上させる。

【解決手段】半導体基板と導電膜の間には、第1絶縁膜、電荷トラップ膜、第2絶縁膜が形成されている。電荷トラップ膜は水素濃度が低い上部領域と、水素濃度が高い下部領域を有する窒化シリコン膜でなる。このような窒化シリコン膜は、化学気相成長法により、水素を15atomic%以上含む窒化シリコン膜を形成し、その上部を窒化することで形成される。この窒化処理は、窒素ガスのプラズマ中に生成された窒素ラジカルで窒化シリコン膜を窒化することで行われる。

(もっと読む)

ハイブリッドマルチビット不揮発性メモリ素子及びその動作方法

【課題】ハイブリッドマルチビット不揮発性メモリ素子を提供する。

【解決手段】第1方式でデータを保存できる第1ストレージノードを備えている第1メモリ部と、第1メモリ部とは異なる第2方式でデータを保存できる第2ストレージノードを備えている第2メモリ部とを備える不揮発性メモリ素子である。第1メモリ部及び第2メモリ部は、ソース及びドレインを共有して2ビット以上のマルチビット動作が可能である。

(もっと読む)

SONOS記憶セル及びその形成方法

【課題】 SONOS記憶セル及びその形成方法を提供する。

【解決手段】 このセルは少なくとも一つの側壁を有する陥没された領域が配置された基板及び第1絶縁膜を介在して陥没された領域を満たすトラップ貯蔵パターンを含む。基板の上部面及びトラップ貯蔵パターンの上部面上に第2絶縁膜を介在して制御ゲート電極が配置される。制御ゲート電極両側の基板内に第1及び第2ソース/ドレイン領域が配置される。トラップ貯蔵パターンの上部面は平ら(flat)であり、少なくとも基板の上部面と同一の高さである。

(もっと読む)

密集したメモリゲートを有するNANDフラッシュメモリ及び製作方法

【課題】 半導体メモリ素子、NANDフラッシュメモリとその製作方法を提供する。

【解決手段】 メモリゲート及び電荷蓄積層を有するセルが密集し、隣接セル内のメモリゲートが互いに部分的に重なるか又は互いに自己整列するNANDフラッシュメモリセルアレイ及び製造方法。メモリセルは、ビット線拡散部と共通ソース拡散部の間で列状に配置され、電荷蓄積層は、セル内のメモリゲートの下に位置決めされる。プログラミングは、負電荷を電荷蓄積ゲートに蓄積させるためにシリコン基板から電荷蓄積ゲートまでのホットエレクトロン注入、又は正電荷を電荷蓄積ゲートに蓄積させるためにシリコン基板から電荷蓄積ゲートまでのホットホール注入により行われる。消去は、プログラミング方法により電荷蓄積ゲートからシリコン基板まで又はその逆のチャンネルトンネリングにより行われる。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート酸化膜を作り分ける際に半導体装置に施されるエッチング回数を削減することで、エッチング処理による半導体装置や半導体基板自体に与える悪影響を低減できる半導体装置の製造方法を提供する。

【解決手段】 フラッシュメモリ部、低電圧高駆動性能トランジスタ部及び高耐圧性能トランジスタ部を形成する領域A,B,CにSi基板1を区分けし、領域Aに酸化膜4及びこれを被覆するフローティングゲート5を形成し、領域A,B,Cを被覆するようにONO膜6を形成し、領域A,Bにフォトレジスト7を施して領域Cを被覆するONO膜6をエッチングし、この領域Cにゲート酸化膜8を形成し、領域A,Cにフォトレジスト7aを施して領域Bを被覆するONO膜をエッチングし、この領域Bにゲート酸化膜9を形成する。

(もっと読む)

1 - 9 / 9

[ Back to top ]