Fターム[5F083ER00]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790)

Fターム[5F083ER00]の下位に属するFターム

キャリア制御 (6,786)

Fターム[5F083ER00]に分類される特許

1 - 4 / 4

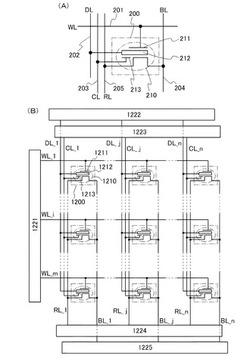

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、該記憶ゲートを絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1及び第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された読み出し信号線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

メモリ書込用電源回路

【課題】昇圧の際の消費電流を削減する。

【解決手段】チャージポンプ回路14が、クロックジェネレータ12から出力されたクロック信号CLK、CLKBに同期して動作し、電源電圧Vccを昇圧した昇圧電圧Vppを出力し、昇圧電圧の電圧値がリミッタ回路16に設定された設定電圧値Vtnを超えた場合に、リミッタ回路16が導通して昇圧電圧Vppが設定電圧値Vtnを超えないように制限し、電流検出回路18が、リミッタ回路16を流れる電流Vppiが設定電流値を超えている期間、クロック信号CLK、CLKBの出力を停止するためのローレベルの停止信号CLKENをクロックジェネレータ12へ出力する。

(もっと読む)

半導体集積回路装置

【課題】少バイト単位の書き込みを実現するメモリアレイ構成において、ディスターブ回数を緩和しながらメモリゲートドライバ数を削減する。

【解決手段】メモリアレイ11は、複数のサブアレイ17、MGトランスファ18、SLドライバ19、およびCGドライバ20から構成されている。サブアレイ17は、複数のメモリゲート線、コントロールゲート線、ソース線、およびビット線BLを有し、これら各線の交差する部分にメモリセルMCがそれぞれ配置される。コントロールゲート線、CGドライバ20、ソース線、およびSLドライバ19は、サブアレイ17に共通に設置されるが、メモリゲート線とMGバッファ回路21とは、サブアレイ17毎に設置される。これにより、メモリアレイ11の回路規模を増大させることなく、書き込み単位を少なくし、ディスターブによる影響を減少させる。

(もっと読む)

情報記録再生装置

【課題】高記録密度及び低消費電力の不揮発の情報記録再生装置を提供する。

【解決手段】本発明の例に関わる情報記録再生装置は、記録層と、前記記録層に電圧を印加して前記記録層に相変化を発生させて情報を記録する手段とを具備し、前記記録層は、少なくとも、化学式1:AxMyX4 (0.1≦x≦2.2、1.5≦y≦2)で表されるスピネル構造を有する第1化合物を含むように構成されることを特徴とする。但し、Aは、Zn, Cd, Hgのグループから選択される少なくとも1種類の元素であり、Mは、Cr, Mo, W, Mn, Reのグループから選択される少なくとも1種類の遷移元素であり、Xは、Oである。

(もっと読む)

1 - 4 / 4

[ Back to top ]