Fターム[5F083ER06]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236) | ソース側から注入 (122)

Fターム[5F083ER06]に分類される特許

1 - 20 / 122

半導体装置

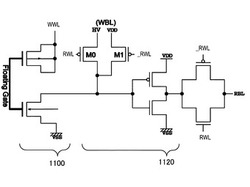

【課題】外部からの回路構成情報の呼び出し処理を不要にして、電源投入後すぐに動作できる半導体装置を提供する。

【解決手段】半導体装置は、ワード線とデータ線とが交差する位置にそれぞれ配置された複数の不揮発メモリセル1100を有する。不揮発メモリセル1100の出力にはインバータ回路が接続され、さらに不揮発メモリセルの出力とWBL(Write Bit Line)との間に第1トランジスタM1と、第1トランジスタよりも抵抗が低い第2トランジスタM2とを備える。インバータ回路の出力とRBL(Read Bit Line)との間にはトランスファーゲートを備える。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】柱状のチャネル層となる半導体層に沿って、複数の浮遊ゲート型の不揮発性メモリセルが積層された構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、柱状の半導体膜131の側面にトンネル誘電体膜141、浮遊ゲート電極膜142、ゲート間絶縁膜143および制御ゲート電極膜144を備えるメモリセルMCが半導体膜131の延在方向に複数設けられるメモリセル列を、半導体基板101上に略垂直に複数配置した不揮発性半導体記憶装置が提供される。ここで、浮遊ゲート電極膜142と制御ゲート電極膜143は、柱状の半導体膜131の全周のうち特定の方向の側面にのみ形成されている。

(もっと読む)

半導体メモリおよびその製造方法

【課題】素子分離トレンチ内の絶縁膜のエッチングとアライメントトレンチ内の絶縁膜のエッチングとを、1つのマスクを用いて同時に行える構造の半導体メモリを提供する。

【解決手段】シリコン基板2には、メモリセル領域70およびアライメントマーク領域80が設定されている。メモリセル領域70には、シリコン基板2の表層部に、アクティブ領域30を分離する素子分離トレンチ21が形成されている。アライメントマーク領域80には、シリコン基板2の表層部に、マスク合わせのためのアライメントトレンチ82が形成されている。素子分離トレンチ21内には、素子分離トレンチ21間のアクティブ領域30が突出するように、絶縁物(酸化膜)23が素子分離トレンチ21の深さ方向途中まで埋め込まれている。一方、アライメントトレンチ82内には、絶縁物23がアライメントトレンチ82の深さ方向途中まで埋め込まれている。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを、有するメモリセルアレイと、ウェルに印加するための出力電圧を出力する出力端子と、入力電圧を昇圧して設定された電圧を出力端子に出力する第1のポンプ回路と、入力電圧を昇圧して設定された電圧を出力端子に出力し、第1のポンプ回路よりも高い電圧を出力可能な第2のポンプ回路と、第1のポンプ回路または第2のポンプ回路の少なくとも何れか一方を昇圧動作させるためのアシスト信号を出力するポンプ切替検知回路と、出力電圧の目標電圧を設定するための設定値に基づいて、第1のポンプ回路および第2のポンプ回路の目標電圧を設定する消去パルス制御回路と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】不揮発性メモリのメモリセルは、p型ウエルPWの上部に絶縁膜3を介して形成された制御ゲート電極CGと、p型ウエルPWの上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGとp型ウエルPWとの間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されかつ内部に電荷蓄積部を有する絶縁膜5とを有している。メモリゲート電極MGは、ノンドープのシリコン膜6aと不純物を導入したシリコン膜6bとの積層膜により形成されている。シリコン膜6bの不純物濃度を高くすることでメモリゲート電極MGの抵抗を低くして不揮発性メモリの動作速度を向上させ、シリコン膜6aの不純物濃度を低くすることで、不揮発性メモリのデータ保持特性を向上させることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】ホットキャリア注入によって書き換えを行うスプリットゲート型MONOSメモリにおいて、リテンション特性を向上させる。

【解決手段】メモリセルM00の選択ゲート電極は選択ゲート線SG0に接続され、メモリゲート電極はメモリゲート線MG0に接続される。また、ドレイン領域はビット線BL0に接続され、ソース領域はソース線SL0に接続される。さらに、メモリセルM00が形成されたp型ウエル領域にはウエル線WL0が接続される。メモリセルM00に書き込みを行うときは、ウエル線WL0を通じてp型ウエル領域に負電圧を印加しながら、ソースサイド注入方式による書込みを行う。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させ、製造歩留りを向上させる。

【解決手段】メモリセル30が複数アレイ状に配置され、X方向に並ぶメモリセル30の選択ゲート電極8は選択ゲート線9によって接続され、メモリゲート電極13はメモリゲート線14によって接続される。ソース領域20を介して隣接するメモリセル30のメモリゲート電極13にそれぞれ接続されたメモリゲート線14同士は電気的に接続されていない。選択ゲート線9は、X方向に延在する第1の部分9aと、一端が第1の部分9aに接続してY方向に延在する第2の部分9bを有している。メモリゲート線14は、選択ゲート線9の側壁上に絶縁膜を介して形成され、選択ゲート線9の第2の部分9b上から素子分離領域上にかけてX方向に延在するコンタクト部14aを有し、コンタクト部14a上に形成されたコンタクトホール23dを埋めるプラグを介して配線に接続される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】共通ゲートを有する複数のトランジスタセルをアレー状に配置する構成を持つ不揮発性半導体集積回路装置において、STI領域のパターニング工程でのパターンの変形を防ぐ製造方法を提供する。

【解決手段】半導体メモリ等のメモリセルアレー等の露光において、矩形形状のSTI溝領域エッチング用単位開口を行列状に配置したSTI溝領域エッチング用単位開口群をネガ型レジスト膜28上に露光するに際して、列方向に延びる第1の線状開口群を有する第1の光学マスクを用いた第1の露光ステップと、行方向に延びる第2の線状開口群を有する第2の光学マスクを用いた第2の露光ステップとを含む多重露光を適用する。直行する2方向において、それぞれの方向に対してマスクを用いて露光を行うことで、矩形形状48の端部における近接効果を回避することができ、矩形形状48の端部が丸みを帯びるのを回避することができる。

(もっと読む)

フラッシュメモリ

【課題】不揮発性メモリセルに複数の閾値電圧を記憶し、前記閾値電圧をワード線に印加した複数のワード線選択レベル電圧を用いて読み出すフラッシュメモリの温度補償回路を単純化する。

【解決手段】基準電圧を発生する電源回路を有し、前記複数のワード線選択レベル電圧を発生する複数の電圧発生回路を、比較器と、チャージポンプ回路と、複数の拡散抵抗素子を直列に接続した分圧回路で構成し、前記基準電圧を前記比較器の負側入力端子に接続し、前記比較器の出力端子を前記チャージポンプ回路の入力端子に接続し、前記チャージポンプで昇圧した出力電圧を前記ワード線と前記分圧回路に接続し、前記分圧回路から引き出した分圧電圧を前記比較器の正側入力端子に接続し、前記複数の電圧発生回路の前記分圧電圧の温度による電圧変化率(温度勾配)を等しくし、前記電源回路が前記温度勾配を有する前記基準電圧を発生する。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート型メモリセルを有する半導体装置の信頼性を向上させる。主要な目的の1つは、制御ゲート電極の表面に形成されているシリサイド層と、メモリゲート電極の表面に形成されているシリサイド層との接触による短絡不良を防止する技術を提供することにある。他の主要な目的は、メモリゲート電極と制御ゲート電極との間の絶縁耐性を保持する技術を提供することにある。

【解決手段】制御ゲート電極8の一方の側壁に形成された積層ゲート絶縁膜9とメモリゲート電極10との間には、酸化シリコン膜や窒化シリコン膜などからなる側壁絶縁膜11が形成されており、メモリゲート電極10は、この側壁絶縁膜11と積層ゲート絶縁膜9とによって制御ゲート電極8と電気的に分離されている。

(もっと読む)

不揮発性半導体集積回路装置

【課題】不揮発性半導体集積回路装置のチップサイズを縮小させる。

【解決手段】シリコン基板上に隣り合って配置された第1および第2ゲート電極とそれらの側方下部のシリコン基板に形成された一対のソース・ドレイン領域とを有し、第2ゲート電極とシリコン基板との間に配置された第2ゲート絶縁膜に電荷を蓄えることで情報を記憶するメモリセルにおいて、メモリセルの消去動作時には、消去非選択セルの第1ゲート電極に正電圧を印加する。

(もっと読む)

半導体装置およびその製造方法

【課題】動作速度が速く、かつ書き換え可能な回数が多くい不揮発性メモリセルと、高い信頼性を有する不揮発性メモリセルとを有する半導体装置を提供する。

【解決手段】メモリゲート電極11a、11bがコントロールゲート電極5a、5bのサイドウォール形状に形成されたスプリットゲート型の不揮発性メモリにおいて、メモリゲート長La、Lbの異なるメモリセルを同一チップ内に混載することにより、動作速度が速く書き換え可能回数の多いメモリと信頼性のあるメモリとを有するメモリチップを安価に製造することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリで発生するディスターブを抑制して、半導体装置の信頼性を向上することができる技術を提供する。

【解決手段】半導体基板1S上に、第1電位障壁膜EB1と電荷蓄積膜ECと第2電位障壁膜EB2からなる積層絶縁膜を介してメモリゲート電極MGが形成されている。そして、このメモリゲート電極MGの両側の側壁に酸化シリコン膜OX3を介して補助ゲート電極AG1、AG2が形成されている。補助ゲート電極AG1、AG2の直下にある半導体基板1S内には浅いn型低濃度不純物拡散領域EX1が形成されている。このように構成されているメモリセルの書き込み動作時において、非選択セルの補助ゲート電極AG1、AG2に負電圧を印加する。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを備える半導体装置において、不揮発性メモリを構成するメモリセルの加工精度を向上することができる技術を提供する。

【解決手段】ポリシリコン膜PF1とダミーゲート電極DMY1を覆うようにポリシリコン膜PF2を形成する。このとき、ポリシリコン膜PF2は、段差DIFおよびギャップ溝GAPの形状を反映して形成される。特に、ギャップ溝GAPを覆うポリシリコン膜PF2には凹部CONが形成される。続いて、ポリシリコン膜PF2上に反射防止膜BARCを形成する。このとき、流動性の高い反射防止膜BARCは、段差DIFの高い領域から低い領域に流出するが、凹部CONに充分な反射防止膜BARCが蓄積されているので、流出する反射防止膜BARCを補充するように凹部CONから反射防止膜BARCが供給される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、駆動力の低下を抑えて、信頼度を向上させることのできる技術を提供する。

【解決手段】メモリセルMC1をp型の導電性を示す導電膜からなる選択ゲート電極CGを有する選択用pMIS(Qpc)とp型の導電性を示す導電膜からなるメモリゲート電極MGを有するメモリ用pMIS(Qpm)とから構成し、書込み時には半導体基板1側からホットエレクトロンを電荷蓄積層CSLへ注入し、消去時にはメモリゲート電極MGからホットホールを電荷蓄積層CSLへ注入する。

(もっと読む)

半導体記憶装置

【課題】メモリウィンドウが大きく信頼性の高い半導体記憶装置を提供することを課題とする。

【解決手段】表面が絶縁体からなる支持基板の上に設けられた半導体層と、前記半導体層内に設けられた、第1の導電型の2つの拡散層領域と、前記2つの拡散層領域の間の前記半導体層内に位置するチャネルと、前記チャネルの上に設けられたゲート絶縁膜と、前記ゲート絶縁膜の上に設けられたゲート電極と、を有し、前記ゲート絶縁膜は、電荷蓄積機能を有し、前記ゲート電極は、その少なくとも一部がリング状平面構造をなし、前記2つの拡散層領域の一方が、前記リング状平面構造の内側に存在し、他方が前記リング状平面構造の外側に存在することを特徴とする半導体記憶装置により上記課題を解決する。

(もっと読む)

1 - 20 / 122

[ Back to top ]