Fターム[5F083ER13]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子放出 (1,246)

Fターム[5F083ER13]の下位に属するFターム

トンネル放出 (407)

ドレイン側へ放出 (115)

ソース側へ放出 (92)

CGへ放出 (79)

CG以外のゲートへ放出 (25)

チャネルへ放出 (411)

ソース/ドレインを除く拡散領域へ放出 (2)

Fターム[5F083ER13]に分類される特許

1 - 20 / 115

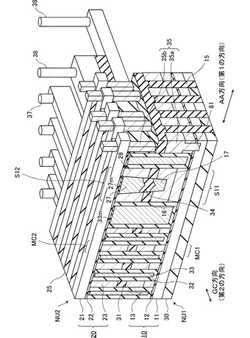

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、コントロールゲートとフローティングゲートとの間のカップリング容量比を増大させることができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。第1の絶縁膜は、半導体基板上に形成されている。フローティングゲートは、第1の絶縁膜上に設けられた第1のフローティングゲート部分、第1のフローティングゲート部分上に設けられた中間絶縁膜、および、中間絶縁膜上に設けられた第2のフローティングゲート部分を含み、電荷を蓄積可能に構成されている。第2の絶縁膜は、フローティングゲートの上面および側面に設けられている。コントロールゲートは、第2の絶縁膜を介してフローティングゲートの上面および側面に対向し、フローティングゲートの電圧を制御する。フローティングゲートの側面において中間絶縁膜が第1および第2のフローティングゲート部分に対して窪んでいる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

半導体装置の作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置の製造方法

【目的】幅寸法が異なるワード線に対する書き込み電圧の設定の適正化を図ることが可能な半導体装置の製造方法を提供することを目的とする。

【構成】実施形態の半導体装置の製造方法は、線幅の異なる複数のワード線の組が繰り返し配置された半導体記憶装置における全ページのそれぞれの書き込み電圧を取得する工程と、すべての組における前記複数のワード線のうちの第1のワード線に対応するページの書き込み電圧の第1の平均値を演算する工程と、すべての組における前記複数のワード線のうちの、前記第1のワード線と隣り合う第2のワード線に対応するページの書き込み電圧の第2の平均値を演算する工程と、各組の第1のワード線に対応するページに対する書き込み電圧を前記第1の平均値に設定し、各組の第2のワード線に対応するページに対する書き込み電圧を前記第2の平均値に設定する工程と、を備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

1 - 20 / 115

[ Back to top ]