Fターム[5F083FR01]の内容

Fターム[5F083FR01]の下位に属するFターム

Fターム[5F083FR01]に分類される特許

1 - 20 / 352

ニッケル酸ランタン膜形成用組成物及びその製造方法、ニッケル酸ランタン膜の製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、並びに液体噴射装置の製造方法

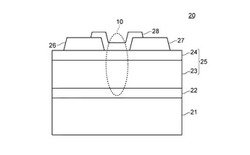

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

衝撃検知・記録装置

【課題】無電源で加わった衝撃を検知し、記録することができ、しかも小型化を図り得る衝撃検知・記録装置を提供する。

【解決手段】衝撃検知・記録装置1は、衝撃による機械的エネルギーを電気エネルギーに変換し出力する圧電素子4を有する衝撃センサ2に並列に強誘電体メモリ3が接続されており、強誘電体メモリ3が、強誘電体層を介して対向する第1,第2の電極を有し、強誘電体メモリ3が衝撃が加わった際に圧電素子が変位する部分以外の衝撃センサ部分に一体化されている。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

マンガン酸化物、マンガン酸化物を備える強誘電体メモリ素子、および強誘電体メモリ装置

【課題】主成分として有害物質鉛元素を含まずに、強誘電性を示しかつ外部磁場によって分極の大きさを制御可能な新規なマンガン酸化物、およびそのメモリへの利用を提供する。

【解決手段】マンガン酸化物は、ペロブスカイト構造を有する、式(1)Sr1−xBaxMnO3(1≧x>0.4)・・・(1)で表されるマンガン酸化物である。単位格子1の対称中心には磁性イオンであるMnイオン3が存在する。単位格子1の対称中心をMnサイトとする。単位格子1が有する8個の頂点には、SrイオンおよびBaイオンのうちいずれか一方が存在している。単位格子1が有する頂点をSrサイト2とする。単位格子1が有する6面の面心には、Oイオン4が存在する。

(もっと読む)

誘電体膜及びその製造方法、並びにキャパシタ

【課題】結晶粒のサイズを制御し、誘電体膜を貫通する結晶粒界やクラックの発生を抑制することによって、リーク電流の少ない高性能のキャパシタを提供する。

【解決手段】電極3,5の間に誘電体膜4が挟持されてなるキャパシタであって、誘電体膜4は、アルカリ土類金属と遷移金属との酸化物に、アルカリ土類金属の炭酸塩を0.1〜10mol%の範囲で含む。

(もっと読む)

データ保持装置及びこれを用いた論理演算回路

【課題】マスクパターンの疎密に起因する強誘電体素子の特性ばらつきを適切に低減することが可能なデータ保持装置及び、これを用いた論理演算回路の提供。

【解決手段】データ保持装置において、不揮発性記憶部に含まれる複数の強誘電体素子X(素子幅m)は、各々よりも素子幅の小さいダミー素子Y(素子幅n、ただしn<m)によって包囲されている。これによってマスクパターンの疎密に起因するエッチングのローディング効果を抑制する事が可能となる。

(もっと読む)

半導体装置

【課題】実動作キャパシタとダミーキャパシタとが形成された半導体装置において、水素・水分、不均一なストレスによる実動作キャパシタの性能劣化を抑制し、FeRAMの寿命特性を向上する。

【解決手段】半導体基板10上の実動作キャパシタ部26の下部電極30と強誘電体膜32と上部電極34を有する複数の実動作キャパシタ36aと、半導体基板10上の実動作キャパシタ部26の外側のダミーキャパシタ部28の下部電極30と強誘電体膜32と上部電極34を有する複数のダミーキャパシタ36bと、複数の実動作キャパシタ36a上の複数の配線40と、複数のダミーキャパシタ36b上の配線40を有し、ダミーキャパシタ36bのピッチの実動作キャパシタ36aのピッチに対する比は、0.9〜1.1の範囲にあり、ダミーキャパシタ36b上の配線40のピッチの実動作キャパシタ36a上の配線40のピッチに対する比は、0.9〜1.1の範囲にある。

(もっと読む)

強誘電体メモリ・デバイスの作製方法

【課題】タグ、ラベル又はパッケージの印刷プロセス、あるいは、パッケージング・プロセス自体に容易に採用できる再書き込み可能な不揮発性メモリ・デバイスを作製する簡易で安価な方法を提供する。

【解決手段】a)第1の印刷手段を用いて絶縁性基板上に第1の印刷インクで第1の電極層を印刷し、それによって第1の組の電極を形成するためと、b)第2の印刷手段を用いて第1の電極層上に第2の印刷インクでメモリ材料のパターニングされた、あるいは、パターニングされていない層を印刷し、c)第3の印刷手段を用いてメモリ層上に第3の印刷インクで第2の電極層を印刷し、それによって第2の組の電極を形成するための連続した工程を含み、それら単独又は組合せのいずれかで実行される作製方法を提供する。

(もっと読む)

誘電体デバイスの製造方法及びエッチング方法

【課題】強誘電体と電極との間のエッチング選択性を高め、強誘電体を高精度にエッチングすることができる誘電体デバイスの製造方法及びエッチング方法を提供する。

【解決手段】金属からなる第1の電極層2の上に酸化物からなる誘電体層3を形成し、誘電体層3の上にエッチングマスク4を形成し、CHF3を含むエッチングガスのプラズマによってエッチングマスク4を介して誘電体層3をエッチングすることで、前記第1の電極層2を露出させる。

(もっと読む)

拡散バリアー層及びその製造方法

【課題】表面を有する基材アセンブリを提供し、この表面の少なくとも一部の上にバリアー層を提供することを含む、集積回路の製造で使用する方法を提供する。

【解決手段】バリアー層14は、白金(x):ルテニウム(1−x)合金でできており、ここでxは約0.60〜約0.995、好ましくはxは約0.90〜0.98である。バリアー層14は、化学気相堆積によって作ることができ、バリアー層14を形成する表面の少なくとも一部は、ケイ素含有表面でよい。この方法は、キャパシター、蓄積セル、接触ライニング等の製造で使用する。

(もっと読む)

強誘電体メモリおよびその動作方法

【課題】ワード線を昇圧せずにセル内のノードを電源電圧に駆動する。

【解決手段】強誘電体メモリは,複数のワード線と複数のプレート線と複数のビット線対と複数のチャージ線とメモリセルとを有する。メモリセルは,ワード線にゲートが接続されビット線対に第一のソース・ドレインがそれぞれ接続された一対の第一導電型MOSFETと,一対の第一導電型MOSFETの第二のソース・ドレインとプレート線との間にそれぞれ設けられた一対の強誘電体キャパシタと,一対の強誘電体キャパシタとチャージ線との間に設けられゲートとドレインとが交差接続された一対の第二導電型MOSFETとをそれぞれ有する。そして,チャージ線駆動回路は,読み出し動作時および書き込み動作時にチャージ線を電源電圧に駆動する。

(もっと読む)

強誘電体メモリおよびその制御方法

【課題】セルデータ読み出しのシグナルマージンを向上させることができる強誘電体メモリおよびその制御方法を実現する。

【解決手段】本発明の実施形態における強誘電体メモリは、セルキャパシタとセルトランジスタとが並列接続された複数のメモリセルと、隣り合う2つのメモリセルにおいてセルキャパシタの下部電極同士または上部電極同士が接続されるよう複数のメモリセルが直列に接続されて、その一端がビット線(/BL、BL)に接続され、他端がプレート線(/PL0、PL0)に接続されたセルブロック(MB0、MB1)と、下部電極がプレート線(/PL0、PL0)に電気的に接続される場合と、上部電極がプレート線(/PL0、PL0)に電気的に接続される場合とでセルキャパシタの電極間にかかる電界が同じ方向に印加されるようにプレート線(/PL0、PL0)およびビット線(/BL、BL)を制御する制御回路11および12を有する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ膜の薄膜化を図るも、リーク電流の増加を抑止しつつ大きな分極反転量を確保し、薄いキャパシタ膜を有する信頼性の高いキャパシタ構造を備えた半導体装置を実現する。

【解決手段】FeRAMの強誘電体キャパシタ構造を形成するに際して、下部電極膜を形成し(ステップS1)、第1の強誘電体膜を形成し(ステップS2)、第1の熱処理で第1の強誘電体膜を結晶化し(ステップS3)、第1の強誘電体膜上にアモルファス状態の第2の強誘電体膜を形成し(ステップS4)、第2の強誘電体膜上にアモルファス状態のSRO膜を形成し(ステップS5)、SRO膜上に第1の上部電極膜を形成し(ステップS6)、第2の熱処理で第2の強誘電体膜及びSRO膜を結晶化する(ステップS7)。

(もっと読む)

論理回路とそれを使用するメモリ

【課題】

低い電源電圧でも動作可能な論理回路を提供する。

【解決手段】

論理回路は,電源電圧側に接続された第1導電型の第1のMOSFETと,基準電圧側に接続されゲートに入力信号が供給される第1導電型の第2のMOSFETと,第1,第2のMOSFETの電流端子の接続ノードに接続された出力端子と,第1のMOSFETのゲートとソース間に設けられたカップリングキャパシタと,第1のMOSFETのゲートと電源電圧との間に設けられた抵抗とを有する。

(もっと読む)

強誘電体薄膜及び該強誘電体薄膜を用いた薄膜キャパシタ

【課題】寿命信頼性を向上し得る、強誘電体薄膜及び該強誘電体薄膜を用いた薄膜キャパシタを提供する。

【解決手段】(PbxLay)(ZrzTi(1-z))O3(式中、0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物に、Bi、Si、Pb、Ge、Sn、Al、Ga、In、Mg、Ca、Sr、Ba、V、Nb、Ta、Sc、Y、Ti、Zr、Hf、Cr、Mn、Fe、Co、Ni、Zn、Cd、Li、Na、K、P、B、Ce、Nd、Sm及びCsからなる群より選ばれた1種或いは2種以上の元素から構成される金属酸化物がある一定の割合で混合した混合複合金属酸化物の形態をとる強誘電体薄膜が、2〜23層の焼成層を積層して構成され、焼成層の厚さtが45〜500nmであり、焼成層中に存在する結晶粒の定方向最大径の平均xが200〜5000nmであり、焼成層のいずれにおいても1.5t<x<23tの関係を満たす。

(もっと読む)

半導体装置およびその製造方法

【課題】経年劣化および分極反転の繰り返しによる劣化の少ない強誘電体キャパシタまたは高誘電率を有する誘電体キャパシタを提供する。比抵抗の増大なしに信頼性の高い配線を有する半導体装置を提供する。

【解決手段】半導体基板表面上に形成された電極を含み、前記電極が、配向性を有する導電体層からなり、前記電極に加え、

下式

M1xM21-x

M1:Au、Pt、Ir、Pd、Os、Re、Rh、Tu、Cu、Co、Fe、Ni、V、Cr

M2:Ta、Ti、Zr、Hf、W、Y、Mo、Nb

で表されるアモルファスまたは微結晶からなるバリア層を含むことを特徴とする。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】簡便な手法で、従来の強誘電体薄膜よりも大幅に比誘電率を向上し得る、高容量密度の薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZTなどの強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、Biを含む複合金属酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、各原料が上記一般式で示される金属原子比を与えるような割合となるように、有機溶媒中に溶解している有機金属化合物溶液からなり、複合金属酸化物Bを構成するための原料が、n−オクタン酸基がその酸素原子を介して金属元素と結合している化合物であることを特徴とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

薄膜キャパシタ

【課題】MIM構造の薄膜キャパシタにおいて、Ptに代わる上部電極を用いた場合であっても、IV特性や信頼性を維持する。

【解決手段】薄膜キャパシタ10は、基板12上に、下部電極14,誘電体層16,上部電極18を順次形成したMIM構造であり、上下の電極のうち、少なくとも上部電極18が、窒化物と金属を積層した積層電極となっている。窒化物としては、Ta,Tiなどの高融点金属を含むことが好ましく、また、窒化物と積層される金属が、前記窒化物に含まれる金属と同じであることが好ましい。更に、窒化物がSiを含んでいてもよい。少なくとも上部電極18に窒化物を含む積層電極を用いることで、Pt電極を用いる場合に必要だった特性回復のアニール処理の必要なく、同等のIV特性を得られるとともに信頼性も向上する。また、誘電体層16と上部電極18の密着性が改善され、剥離が生じない。

(もっと読む)

1 - 20 / 352

[ Back to top ]