Fターム[5F083FR02]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733) | キャパシタを有するもの(破壊読出型) (1,245) | 1Tr/1C型 (791)

Fターム[5F083FR02]に分類される特許

1 - 20 / 791

半導体装置の製造方法

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

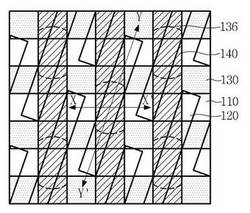

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体素子及びその形成方法

【課題】ビットラインを容易に形成することができ、ビットライン工程マージンを増加させ、さらに隣接したビットライン間のキャパシタンスを減少させる半導体素子及びその形成方法を提供する。

【解決手段】本発明に係る半導体素子は、半導体基板10で一方向に延長され、垂直チャンネル領域12b,14bを含む第1及び第2ピラー12,14と、第1及び第2ピラー12,14の内部で垂直チャンネル領域12b,14bの下部に位置する第1ビットライン22と、第1ビットライン22を含む第1ピラー12及び第2ピラー14の間に位置する絶縁膜32とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

(もっと読む)

半導体記憶装置

【課題】記憶素子の加工が容易であり、かつ、記憶素子が安定した特性を有するメモリを提供する。

【解決手段】本実施形態によるメモリは、半導体基板を備える。複数のアクティブエリア列は、半導体基板上に設けられ第1の方向に配列された複数のアクティブエリアをそれぞれが含む複数のアクティブエリア列であり、第1の方向に対して直交する第2の方向に隣接するアクティブエリアは互いに半ピッチずつずれて配置されている。複数のセルトランジスタは、アクティブエリアのそれぞれに対応して設けられている。複数の記憶素子は、複数のセルトランジスタの一端に電気的に接続されている。上部電極は、複数のアクティブエリア列のうち第2の方向に隣接する第1および第2のアクティブエリア列に対応する複数の記憶素子に交互に接続されている。ビット線は、第1および第2のアクティブエリア列に含まれる複数のセルトランジスタの他端に電気的に接続されている。

(もっと読む)

記憶装置及び記憶装置の製造方法

【課題】低電圧で動作する分極率の高い強誘電体メモリを提供する。

【解決手段】基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置により上記課題を解決する。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置の製造方法

【課題】金属酸化膜の表面に形成される導電膜の基板面内における厚さばらつきを低減して、半導体装置の歩留まりを向上させることが可能であり、かつ導電膜の成長速度を向上させて、半導体装置の生産性を向上させることの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、金属酸化膜を含む誘電体膜5を形成する工程と、誘電体膜5において、表面5aに非晶質の金属酸化膜が露出した状態で、誘電体膜5の表面5aに導電膜6を形成する工程と、を含む。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

強誘電体キャパシタ

【課題】還元性雰囲気による特性劣化を抑制することができる構造の強誘電体キャパシタを提供する。

【解決手段】強誘電体キャパシタ積層構造8は、強誘電体膜3と、強誘電体膜の一方表面に接する下部電極2と、強誘電体膜3の他方表面に接する上部電極4とを含む。上部電極4および下部電極2のうちのうちの少なくともいずれか一方が、酸化物導電体層と金属層とを交互に積層した積層電極構造を有している。この積層電極構造は、酸化物導電体層および金属層のうちの少なくともいずれか一方を2層以上含む。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

強誘電体キャパシタの製造方法及び強誘電体キャパシタ

【課題】強誘電体膜の表面に現れた窪みを、強誘電体材料で効率的に埋め込むことが可能な強誘電体キャパシタの製造方法を提供する。

【解決手段】基板10の上に第1導電膜11を形成する。第1導電膜11の上に、表面に複数の凹部15が形成された第1強誘電体膜12を形成する。第1強誘電体膜12の表面の凹部15を埋め込むように、第1強誘電体膜12の上に、原子層堆積法により第2強誘電体膜13を形成する。第2強誘電体膜13の上に、第2導電膜17を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法

【課題】液体プロセスに採用し易い配向性の制御が可能な半導体装置や強誘電体素子の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ソース電極およびドレイン電極と、前記ソース電極及び前記ドレイン電極との間に配置され、チャネル部を有する有機半導体膜と、ゲート電極と、前記チャネル部と前記ゲート電極との間に配置されたゲート絶縁膜と、を有する半導体装置の製造方法であって、前記チャネル部を第1の温度に加熱する工程と、前記第1の温度の前記有機半導体膜に、前記第1の温度よりも低い第2の温度の絶縁性ポリマーを含む液滴材料を配置し一定の方向に延ばす塗工工程により前記ゲート絶縁膜を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の面積を削減する。

【解決手段】複数のメモリセル(NMC,DMC)のうち周辺回路領域(PC)に隣接するメモリセル(DMC)と半導体基板(100)との間には、そのメモリセル(DMC)の下部電極(M13)から半導体基板(100)に向けて延伸するコンタクトプラグが形成されていない。第1のコンタクトプラグ(C101)は、半導体基板(100)の平面視において第1のコンタクトプラグの端面の少なくとも一部がメモリセルアレイ(MARY)の周縁よりも内側に配置されるように形成されている。

(もっと読む)

半導体記憶装置の製造方法および半導体記憶装置

【課題】 半導体記憶装置のキャパシタの構成要素として、強誘電体等の容量絶縁膜を液状材料の塗布により形成する製造方法において、CMPによる下部電極へのスクラッチ防止と、容量絶縁膜膜厚のメモリセルアレイ内、下部電極内での均一性を実現し、キャパシタ特性を向上させる。

【解決手段】 例えば下部電極8c上にタングステン犠牲膜としての第1金属膜20を形成した後、層間絶縁膜11で被覆する。次に層間絶縁膜11をCMP法で平坦化すると共にエッチングで第1金属膜20を露出させ、さらにタングステン膜等の第2金属膜22を堆積する。次に第2金属膜22をCMP法で研磨し、再び第1金属膜20を露出させた後、第1金属膜20を除去する。次に第2層間絶縁膜11と下部電極8c上に絶縁材料の前駆体を含む液状材料を塗布し、熱処理を行って例えば強誘電体からなる容量絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】実動作キャパシタとダミーキャパシタとが形成された半導体装置において、水素・水分、不均一なストレスによる実動作キャパシタの性能劣化を抑制し、FeRAMの寿命特性を向上する。

【解決手段】半導体基板10上の実動作キャパシタ部26の下部電極30と強誘電体膜32と上部電極34を有する複数の実動作キャパシタ36aと、半導体基板10上の実動作キャパシタ部26の外側のダミーキャパシタ部28の下部電極30と強誘電体膜32と上部電極34を有する複数のダミーキャパシタ36bと、複数の実動作キャパシタ36a上の複数の配線40と、複数のダミーキャパシタ36b上の配線40を有し、ダミーキャパシタ36bのピッチの実動作キャパシタ36aのピッチに対する比は、0.9〜1.1の範囲にあり、ダミーキャパシタ36b上の配線40のピッチの実動作キャパシタ36a上の配線40のピッチに対する比は、0.9〜1.1の範囲にある。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

メモリセルキャパシタ構造におけるメモリセルキャパシタプレートの形成方法

【課題】酸素にさらされても絶縁膜を形成しない材料からメモリセルキャパシタプレートを製造するための形成方法を提供する。

【解決手段】メモリセルキャパシタプレートの形成方法は、犠牲層を堆積する工程と、その犠牲層内に開口部を形成する工程とを含む。続いて、酸素にさらされても相当の導電性を維持する導電性料を含む電極材料層702を、犠牲層の上面に堆積し、開口部の少なくとも一部を充填する。次に、電極材料層702の一部を少なくとも犠牲層の上面と同じ略同じ高さにまで除去することによりメモリセルキャパシタプレートの上面を画定し、その後、犠牲層を除去する。

(もっと読む)

1 - 20 / 791

[ Back to top ]