Fターム[5F083GA03]の内容

Fターム[5F083GA03]に分類される特許

1 - 20 / 322

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造の容易な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第2のメモリセルを具備する第2のNANDセルユニットを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1のNANDセルユニットの両端に位置し、第1の浮遊ゲートと同層に形成され、第1の半導体層と接続される下部コンタクトと、第2のNANDセルユニットの両端に位置し、第2の半導体層と下部コンタクトとを接続する上部コンタクトとを備える。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】パンチスルーを抑制しつつ、セレクトゲート電極からのフリンジ電界を低減する。

【解決手段】空隙AG1は、制御ゲート電極8およびセレクトゲート電極12下に潜るようにしてトレンチ2に沿って連続して形成され、セレクトゲートトランジスタのドレイン領域間に達している。そして、セレクトゲートトランジスタのドレイン領域間において、空隙AG1が埋め戻し絶縁膜RBにて埋め戻されている。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】本発明は、第1の不純物拡散領域と第2の不純物拡散領域との間に位置するピラーを流れるドレイン電流が、隣接するピラーにリーク電流として流れることを防止可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13に立設されたピラー28と、Y方向に延在するように半導体基板13に設けられ、Y方向と交差するX方向において対向するピラー28の第2の側壁を露出する第1の溝16と、ピラー28の第2の側壁の下部に設けられた第1の不純物拡散領域と、ピラー28の上端に設けられた第2の不純物拡散領域と、半導体基板13に内設され、第1の溝16の底16Aに配置された絶縁層14と、を有する。

(もっと読む)

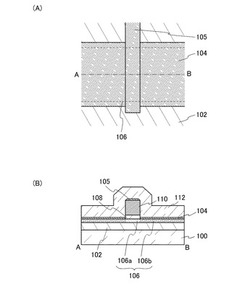

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体素子及びその形成方法

【課題】ビットラインを容易に形成することができ、ビットライン工程マージンを増加させ、さらに隣接したビットライン間のキャパシタンスを減少させる半導体素子及びその形成方法を提供する。

【解決手段】本発明に係る半導体素子は、半導体基板10で一方向に延長され、垂直チャンネル領域12b,14bを含む第1及び第2ピラー12,14と、第1及び第2ピラー12,14の内部で垂直チャンネル領域12b,14bの下部に位置する第1ビットライン22と、第1ビットライン22を含む第1ピラー12及び第2ピラー14の間に位置する絶縁膜32とを含む。

(もっと読む)

半導体装置、メモリカード、データ処理システムおよび半導体装置の製造方法

【課題】歩留まりや信頼性の低下を招くことなく、隣接セルのフローティング・ゲート間の結合容量を小さくすることができ、隣接セルの書き込み情報の影響を小さくした状態でフローティング・ゲートの電位を制御することが可能なNAND型フラッシュメモリを提供する。

【解決手段】一導電型の半導体材料層表面のチャネル領域上方に第2の絶縁膜12を介して形成されたゲート電極部と、ゲート電極部の上方に前記ゲート電極部と一体形成されたキャパシタ電極部と含むフローティング・ゲート13と、キャパシタ電極部の側面を囲むように第1の絶縁膜12を介して形成されたコントロールゲート10となる第1の電極と、を有する。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】不純物添加シリコン層に添加された不純物が不純物無添加シリコン層に拡散するのを抑制する。

【解決手段】セレクトゲート電極SG1上にはワード線WL1が積層され、最上層のワード線WL1上にはセレクトゲート電極SG2がロウごとに形成されることで、NANDセルNC1が構成され、セレクトゲート電極SG1、SG2およびワード線WL1は、不純物添加シリコン層2と層間絶縁膜とを拡散防止層3を介して交互に積層することで構成し、ワード線WL1は、拡散防止層3にて挟まれた不純物添加シリコン層2にて構成する。

(もっと読む)

半導体記憶装置

【課題】ゲート面積に依存するトランジスタばらつきを抑制し、読み出し動作を高速化した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向に延びるワード線WL、カラム方向に延びる複数のビット線BL0,BL1,BL2で構成されたビット線グループ、並びに、トランジスタからなりワード線及びビット線グループの交差部に設けられたメモリセル、を有するメモリセルアレイと、ビット線を介してメモリセルからデータを読む読み出し回路とを備え、メモリセルは、トランジスタのソース又はドレインを、ビット線グループに属する複数のビット線BL0,BL1,BL2のいずれとも接続しないか又はいずれか1本とだけ接続するかの異なる接続状態を有し、トランジスタのゲートとなるアクティブ領域AAは、ビット線グループの複数のビット線BL0,BL1,BL2の配置領域及び各ビット線間のスペースに連続的に形成されている

(もっと読む)

半導体記憶装置、半導体装置及び半導体記憶装置の製造方法

【課題】DRAMとReRAMとを混載する場合において、容量素子及び抵抗変化素子の性能を維持しながら製造コストを低減する。

【解決手段】半導体記憶装置は、抵抗変化素子1と容量素子101とを具備している。抵抗変化素子1は、第1深さD1のシリンダー型のMIM構造を有し、抵抗変化型メモリ用である。容量素子101は、第1深さD1よりも深い第2深さD2のシリンダー型のMIM構造を有し、DRAM用である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】寄生抵抗がより低いチャネルボディ層を有する不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置は、半導体層と、第1絶縁層が表面に設けられた第2絶縁層と、第3絶縁層と、第2絶縁層および第3絶縁層の上に、電極層と絶縁膜とを有する第1積層体と、第1積層体の積層方向に貫通し第2絶縁層に達する一対の第1ホールのそれぞれの側壁に設けられたメモリ膜と、メモリ膜の内側に設けられた第1チャネルボディ層と、層間絶縁膜と選択ゲートとを有する第2積層体と、一対の第1ホールのそれぞれ上端と連通し、第2積層体の積層方向に貫通する第2ホールの側壁に設けられたゲート絶縁膜と、ゲート絶縁膜の内側に設けられた第2チャネルボディ層と、第1積層体の下側に設けられた連結部と、一対の第1ホールの間に挟まれ、第1積層体の表面から第1絶縁層に達する第4絶縁層と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】隣接セルの書き込み閾値の変動を抑制すると共に、制御ゲート電極膜とシリコン基板との間のリーク電流を低減して消去特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。前記電極間絶縁膜は、第1のシリコン酸化膜、第1のシリコン窒化膜、第2のシリコン酸化膜および第2のシリコン窒化膜を積層形成した積層構造を有する。そして、前記電極間絶縁膜は、前記第2のシリコン酸化膜のうちの前記素子分離絶縁膜の上面上の部分の膜厚が前記電荷蓄積層の上面上の部分の膜厚より薄くなるように構成した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高電界リークを低減して、書き込み特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。そして、前記電極間絶縁膜は、シリコン窒化膜もしくは高誘電率膜を2層のシリコン酸化膜で挟んだ積層構造または高誘電率膜とシリコン酸化膜の積層構造及び前記積層構造と前記制御電極層の間に形成された第2のシリコン窒化膜を有し、前記第2のシリコン窒化膜のうちの前記電荷蓄積層の上面上の部分を消失させた。

(もっと読む)

抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法

【課題】安定したスイッチング動作を低コストで実行する抵抗変化型不揮発性記憶装置を提供する。

【解決手段】抵抗変化型不揮発性記憶装置は、第1配線3と、第1配線3上に形成された層間絶縁層53と、層間絶縁膜53上に形成された第2配線6と、第1配線3と第2配線6との間に形成された抵抗変化型素子11とを具備する。層間絶縁層53は、第1配線3と第2配線6とに挟まれるように形成され、第1配線3の幅以下の幅を有するホール9を備える。抵抗変化型素子11は、第1配線3と接して、ホール9の底部に形成された下部電極13と、下部電極13上に形成された抵抗変化層12と、抵抗変化層12上に形成された上部電極11とを備える。下部電極13、抵抗変化層12及び上部電極11は、ホール9の内部に形成される。第1配線3は銅を含み、下部電極13、13aはルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

(もっと読む)

1 - 20 / 322

[ Back to top ]