Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,041 - 2,060 / 2,405

互いに自己整合的に形成されたセルダイオード及び下部電極を有する相変化記憶セル及びその製造方法

【課題】垂直ダイオードを有する集積回路素子が提供される。

【解決手段】前記集積回路素子は集積回路基板及び前記集積回路基板上の絶縁膜を具備する。前記絶縁膜を貫通するコンタクトホールが設けられる。前記コンタクトホールの下部領域内に垂直ダイオードが設けられ、前記垂直ダイオード上の前記コンタクトホール内に下部電極が設けられる。前記下部電極の下部面は前記垂直ダイオードの上部面上に位置する。前記下部電極は前記垂直ダイオードと自己整合される。前記下部電極の上部面は前記コンタクトホールの水平断面積よりも小さい面積を有する。前記集積回路素子の製造方法も提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ型キャパシタのトレンチ部のサイズを殆ど大きくすることなく、電気的容量の増大が図られたトレンチ型キャパシタを備える半導体装置を提供する。

【解決手段】半導体装置7は、半導体基板1および少なくとも1個のトレンチ型キャパシタ10を具備する。半導体基板1には、少なくとも下部2bの内面が凹凸形状に形成されたトレンチ部2が表面から掘り下げられて少なくとも1箇所に形成されている。キャパシタ10は、半導体基板1との間に容量絶縁膜8を挟んでトレンチ部2の内部に電極用導電体9の一部が設けられて形成されている。

(もっと読む)

Bi系誘電体薄膜形成用組成物およびBi系誘電体薄膜

【課題】800℃未満の低温焼成によってもBi系誘電体の結晶化薄膜を得ることができるBi系誘電体薄膜形成用組成物とBi系誘電体薄膜を提供する。

【解決手段】少なくともSr、Bi、Taおよびランタノイド系元素Aの各金属または複合金属のアルコキシド、有機塩あるいは錯体を反応させることによって得られる化合物を含有させてBi系誘電体薄膜形成用組成物を構成する。この組成物の塗膜を800℃未満の低温で焼成することにより、下記一般式(1)

Sr1-XAβBi2+Y(Ta2-ZNbZ)O9+α・・・・・(1)

(式中、Aは、ランタノイド系元素を表す。X、Y、αは、それぞれ独立に0以上1未満の数を表し、Zは、0以上2未満の数を表し、βは、0.09以上0.9以下の数を表す。)で表されるBi系誘電体の結晶化薄膜を得る。

(もっと読む)

積層キャパシタDRAMセルの形成方法

本発明は、接触プラグの行と平行な底板の行とを具えた半導体構造物を含む。このプラグのピッチは、底板のピッチのほぼ倍となる。本発明は、半導体構造物の形成方法を含む。接触プラグの第一の行および第二の行および第三の行に対してほぼ直交するような、複数の導電層が基板上に形成される。複数の導電層の内部に導電層のそれぞれを貫くようにして、開口部を蝕刻する。この開口部は、第一の接触プラグの行と第二の接触プラグの行との横方向の間に配置される。開口部を蝕刻した後に、複数の導電層に被せるように誘電体を堆積させてから、第二の導電性材料をこの誘電体の上に被せて堆積させる。本発明には、プロセッサと、このプロセッサと関連して動作するメモリとを含んだ電子システムが含まれる。こうしたメモリ装置は、倍ピッチにしたキャパシタを含んだメモリアレイを有する。 (もっと読む)

4.5F2DRAMセルのための接地されたゲートを備えたトレンチ分離トランジスタおよびそれの製造方法

接地されたゲートを有する分離トランジスタが、第1のアクセストランジスタ構造と第2のアクセストランジスタ構造との間に形成され、メモリーデバイスのアクセストランジスタ構造間を分離する。一実施形態においては、アクセストランジスタ構造は、凹状アクセストランジスタである。一実施形態においては、メモリーデバイスは、DRAMである。さらなる実施形態においては、メモリーデバイスは、4.5F2DRAMセルである。 (もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、NAND型フラッシュメモリにおいて、選択ゲートトランジスタの水平方向のゲート長を小さくできるようにする。

【解決手段】たとえば、メモリセルアレイは、マトリクス状に配置された複数のメモリセルユニットを備える。各メモリセルユニットは、電気的なデータの書き込みおよび消去が可能な所定個のメモリセルトランジスタMCを列方向に直列に接続したメモリセル列の、その一端が第1の選択ゲートトランジスタを介してビット線BLに接続され、他端が第2の選択ゲートトランジスタSGSを介してソース線SLに接続されている。選択ゲートトランジスタSGSは、ゲート電極部GE2の一部が、シリコン基板11の表面部に設けられた溝部12内に埋め込まれている。

(もっと読む)

半導体集積回路装置

【課題】ワード線の抵抗値の増大を抑制しつつ、メモリセルトランジスタの集積度を高めることができ、かつ、微細加工性に優れた不揮発性半導体記憶装置を提供すること。

【解決手段】制御ゲート(WL)は、インターゲート絶縁膜に接する第1の導電膜と、この第1の導電膜に電気的に接続される第2の導電膜と、を含む。第1スタックゲート構造と第2スタックゲート構造との間を絶縁する層間絶縁膜は、浮遊ゲート(FG)間、及び制御ゲート(WL)の一部分間を絶縁する第1の絶縁膜と、制御ゲート(WL)の他部分間を絶縁する第2の絶縁膜と、第1の絶縁膜と第2の絶縁膜との間に設けられ、第1、第2の絶縁膜に対してエッチング選択比をとれる第3の絶縁膜と、を含む。

(もっと読む)

メモリセル及び記憶装置

【課題】 電気抵抗の状態により情報を記憶・保持する記憶素子を用いた場合に、書込みと消去の処理が簡単にできるようにする。

【解決手段】 可変抵抗素子1と、可変抵抗素子1の両端に印加する電圧を制御するスイッチング素子としてのMOSトランジスタ2と、可変抵抗素子1とMOSトランジスタ2との間(又はMOSトランジスタ2のドレイン側)に直列に接続された、非線形電流電圧特性を有する抵抗素子6とを備えるメモリセルとして構成した。また、このメモリセルを備えた記憶装置として構成した。かかる構成としたことで、書込み時と読出し時とで、MOSトランジスタのゲートに印加する電圧を等しくすることができる。

(もっと読む)

強誘電体記憶装置およびその製造方法

【課題】強誘電体記憶装置の微細化を達成する。

【解決手段】基板10に形成されたトランジスタ部分50と、第一の層間膜60を介して上部に形成され、トランジスタ50のチャネル長方向に電極100間をむすぶ方向が沿うように配置された強誘電体キャパシタとを備え、前記強誘電体膜90の形成時に犠牲膜による溝を利用することにより、キャパシタの電極100間の距離をリソグラフィーによる加工寸法以下に微細化することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】 補助ゲート電極型のフラッシュメモリを有する半導体装置の信頼性を向上させる。

【解決手段】 フラッシュメモリの補助ゲート配線上に窒化シリコンを主体とする材料で形成されたキャップ絶縁膜3において、ワード線WLの隣接間のキャップ絶縁膜3の厚さを、ワード線WLと補助ゲート配線AGLとの間のキャップ絶縁膜3の厚さよりも薄くする。これにより、斜め方向に隣接するビット間に寄生する容量を低減できるので、メモリセルのしきい値電圧の変動を抑制または防止することができる。したがって、補助ゲート電極型のフラッシュメモリを有する半導体装置の信頼性を向上させることができる。

(もっと読む)

記憶素子及び記憶装置

【課題】 記憶層の耐圧を充分に確保することを可能にすると共に、初期化動作に必要な電圧値を低く抑えることが可能な構成の記憶素子を提供する。

【解決手段】 第1の電極と第2の電極との間に、記憶層4が挟まれて構成され、この記憶層4が、絶縁性或いは半絶縁性であり、記憶層4に接して金属元素を含有する層が設けられ、第1の電極と第2の電極間に電圧を印加することにより、記憶層4の抵抗値が変化する構成であり、記憶層4が厚さ方向において不連続に金属元素41が含有されている記憶素子を構成する。

(もっと読む)

半導体記憶装置

【課題】 より高密度にフューズを配置することを可能にする半導体記憶装置を提供する。

【解決手段】 下層基板100と、下層基板100上に形成された中間絶縁膜202と、下層基板100上に形成された下層配線層201−1と、中間絶縁膜202上に形成された上層フューズ204−1と、下層配線層201−1と上層フューズ204−1とを電気的に接続するコンタクト配線203−1とを含む配線パターンと、下層基板100上に形成された下層配線層201−2と、中間絶縁膜202上に形成され且つ上層フューズ204−1と幅方向において重ならない領域(照射領域LS)を互いに有する上層フューズ204−2と、下層配線層201−2と上層フューズ204−2とを電気的に接続するコンタクト配線203−2とを含み、上記の配線パターンと所定の距離aを離間して隣り合う配線パターンとを有する。

(もっと読む)

半導体装置

【課題】メモリセルが備えるキャパシタの電荷リークを抑制することができ、且つ、キャパシタの有効面積を増大させると共にその容量値のばらつきを抑制する。

【解決手段】SOI層3には分離トレンチ40が形成されており、その中には分離絶縁膜4が形成される。分離絶縁膜4には、分離トレンチ40の内壁を露出する開口部41が形成されており、当該開口部41は絶縁層2にまで達している。キャパシタ102の下部電極(不純物拡散層24)並びに誘電体層21は、開口部41に露出した分離トレンチ40の内壁に延在し、上部電極22の少なくとも一部は開口部41に埋め込まれる。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】 面積が小さい磁気ランダムアクセスメモリを提供する。

【解決手段】 磁気ランダムアクセスメモリは、内部の磁化方向に応じて情報を記憶する複数のメモリセル1を含む。第1書き込み線2は、第1延在部2a、第2延在部2b、第1接続部2bを含む。第1延在部は、第1方向に沿い、第1端および第2端を有する。第2延在部は、第1方向に沿い、第1端および第2端とそれぞれ同じ側の第3端および第4端を有する。第1接続部は、第1端と第3端とを接続する。第2書き込み線3は、第1書き込み線と共に複数のメモリセルの1つを挟む。第1書き込み線に電流を流す複数の第1周辺回路4は、第2端および第4端の一方または両方と、第1接続部と、に接続される。

(もっと読む)

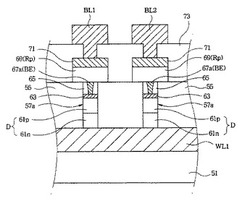

相変化記憶素子及びその製造方法

【課題】セル大きさの増大を防止できる相変化記憶素子及びその製造方法を提供すること。

【解決手段】相変化記憶素子は、相変化セル領域25及び電圧印加領域24を有する半導体基板21と、半導体基板21上に形成された第1酸化膜26、窒化膜27及び第2酸化膜28と、第1酸化膜26、窒化膜27及び第2酸化膜28に隣接して相変化セル領域に形成された第1プラグ32と、第1酸化膜26及び窒化膜27に隣接して電圧印加領域に形成された第2プラグ33と、第2プラグ33上に形成された導電ライン34と、第1プラグ32、導電ライン34及び第2酸化膜28上に形成された第3酸化膜35と、第3酸化膜35に隣接し、第1プラグ32と直接コンタクトするように第1プラグ32の上に形成されたプラグ形状の下部電極37と、下部電極37上にパターン形状で形成された相変化膜38及び上部電極39とを備える。

(もっと読む)

半導体装置及び半導体装置の配線方法

【課題】 負荷容量のアンバランスを軽減でき、さらには実装面積を削減できる半導体装置を提供する。

【解決手段】 半導体装置は、拡散領域A1と、ゲートG1と、拡散領域A2と、ゲートG2と、拡散領域A3とで2個のトランジスタを構成する第1回路1と、拡散領域B1と、ゲートG1と、拡散領域B2と、ゲートG2と、拡散領域B3とで2個のトランジスタを構成する第2回路2とを備える。拡散領域A1とB3、拡散領域A2とB2、拡散領域A3とB1とを接続、または拡散領域A1とA3とB2、拡散領域A2とB1とB3を接続して使用すると、製造過程で拡散層とゲートの位置関係がずれたとしても、負荷容量のアンバランスが生じることがない。

(もっと読む)

半導体装置

【課題】ヒューズを切断するか否かで回路状態を設定することなく、不良メモリセルを冗長メモリセルに簡単に置換することができる半導体装置を提供する。

【解決手段】半導体装置は、複数のメモリセルおよび冗長メモリセルを含むメモリを搭載する。選択信号に応じて、メモリセルの不良ビットを冗長メモリセルに置換するか否かを制御する冗長セルセレクタと、選択信号とグランドとの間に接続されたプルダウン抵抗とを備える。選択信号は接続パッドに接続され、接続パッドは、選択信号の電位に応じて、オープン状態とされているか、もしくは電源ピンにボンディングされている。

(もっと読む)

半導体集積回路装置

【課題】素子分離溝の幅を微細化し、それによってMISFETを微細化できる半導体集積回路装置を提供する。

【解決手段】基板1の主面上に、素子分離溝2によって周囲を囲まれた島状の平面パターンを有する複数の活性領域が、第1方向にそれぞれ間隔をおいて配置され、複数の活性領域のそれぞれに半導体素子が形成されている。素子分離溝2によって周囲を囲まれた活性領域は、周辺部に、凸状の丸みが付いた凸状部を有しており、第1方向における活性領域の幅aと、活性領域同士の間の間隔bとの和を、第1方向における最小ピッチとすると、第1方向における活性領域の幅aは最小ピッチの1/2よりも大きく、間隔bは最小ピッチの1/2よりも小さい。この最小ピッチは、フォトリソグラフィ技術の解像限界に基づいて予め決まっている最小加工寸法の2倍である。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法を提供する。

【解決手段】 半導体素子の製造方法であって、(a)少なくとも二つのディープトレンチコンデンサ208を内部に有すると共に、前記ディープトレンチコンデンサ208の上部が露出する基板200を提供する工程と、(b)前記ディープトレンチコンデンサ208の前記基盤200上に露出している部分の側壁を取り囲むスペーサ226を形成する工程と、(c)前記ディープトレンチコンデンサの上面と前記スペーサ226とをマスクとして用いた前記基板200のエッチングにより、凹部228を前記基板に形成する工程と、(d)前記凹部228内に凹型ゲート232を形成する工程とを含んで構成される。

(もっと読む)

スイッチング素子、書き換え可能な論理集積回路およびメモリ素子

【課題】高集積化可能で、電源を切ってもオン状態およびオフ状態のうちいずれか一方の状態を保持し、オン状態での抵抗値が低く、さらに上記いずれか一方の状態に再プログラムが可能なスイッチング素子を提供する。

【解決手段】電気化学反応に用いられる金属イオンが伝導するためのイオン伝導体14と、イオン伝導体14に接して、所定の距離だけ離れて設けられたソース電極11およびドレイン電極12と、オン状態に遷移させる電圧が印加されるとソース電極11およびドレイン電極12の間に金属イオンによる金属を析出させてソース電極11およびドレイン電極12を電気的に接続し、オフ状態に遷移させる電圧が印加されると析出した金属を溶解させてソース電極11およびドレイン電極12の電気的接続を切るための、イオン伝導体14に接して設けられたゲート電極13とを有する。

(もっと読む)

2,041 - 2,060 / 2,405

[ Back to top ]