Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,061 - 2,080 / 2,405

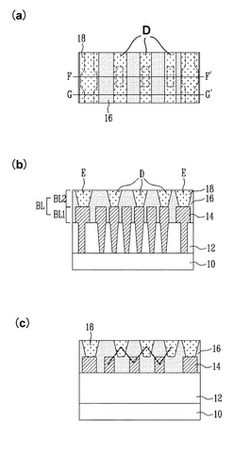

フラッシュメモリ素子のビットライン形成方法

【課題】ビットラインの間隔が最小化されると同時にビットラインの静電容量が増加することを防止してセンシングタイムを減らす。

【解決手段】半導体素子の形成された半導体基板10上にドレインコンタクトホールに埋め込まれると同時に第1層間絶縁膜12の上部に所定の厚さ形成されるように第1金属物質14を形成する段階と、前記第1層間絶縁膜12の上部に所定の厚さ形成された第1金属物質14をパターニングし、第1金属配線の奇数番目に配置される第1金属層、及び前記第1金属層の間に位置するランディングパッドを形成する段階と、前記第1金属層及びランディングパッドが形成された結果物の全面に第2層間絶縁膜16を形成した後パターニングして、前記ランディングパッドを露出させるトレンチを形成する段階と、前記トレンチの内部にのみ第2金属物質18が埋め込み、第1金属配線の偶数番目に配置される第2金属層を形成する段階とを含む。

(もっと読む)

双方向分割ゲートNANDフラッシュメモリ構造及びアレイ、そのプログラミング方法、消去方法及び読み出し方法、並びに、製造方法

【課題】NANDフラッシュメモリ構造において、各セルについてのライン数を削減して、不揮発性メモリデバイスのピッチを改善すること。

【解決手段】分割ゲートNANDフラッシュメモリ構造が、第1伝導型の半導体基板上に形成される。このNAND構造は、第2伝導型の第1領域と、基板内にこの第1領域から間隔をおいて配置されてこの第1領域との間にチャネル領域を定める、第2伝導型の第2領域と、を備える。各々が上記チャネル領域から絶縁された複数の浮動ゲートが、互いに間隔をおいて配置される。各々が上記チャネル領域から絶縁された複数の制御ゲートが、互いに間隔をおいて配置される。該制御ゲートの各々は、1対の浮動ゲートの間にあって該1対の浮動ゲートに容量的に接続される。各々が上記チャネル領域から絶縁された複数の選択ゲートが、互いに間隔をおいて配置される。該選択ゲートの各々は、1対の浮動ゲートの間にある。

(もっと読む)

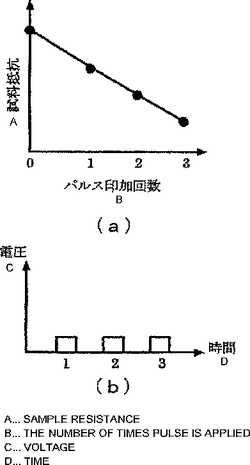

多値メモリおよびそのための相変化型記録媒体への記録方法

相変化型記録媒体への電気パルスの印加回数を制御することによって、抵抗値の段階的な変化を制御することで、抵抗値の違いによって多値情報を記録する。電気パルスは、相変化型記録媒体を高抵抗状態から低抵抗状態へと変化させる第一印加手段、低抵抗状態から高抵抗状態へと変化させる第二印加手段により段階的に抵抗値を変化させる。そして、記録された情報と書き込むべき情報との比較差分から、書き込むべき情報へ変化させるために必要な電気パルスが選択されその印加回数が算出される。本発明によって、回路構成が簡単で高集積化に好適な多値メモリが提供される。  (もっと読む)

(もっと読む)

磁気記憶素子

【課題】 素子の微細化に伴う反転磁界の増大を抑制し、かつ記録層の磁化分布を制御することが可能な磁気記憶素子を提供する。

【解決手段】 この強磁性トンネル接合素子7では、記録層22を円形にしたので、素子の微細化に伴う反転磁界の増大を抑制することができる。また、記録層22は順次積層された強磁性層25、非磁性層26、強磁性層27、非磁性層28、および強磁性層29を含み、強磁性層25と27、および強磁性層27と29はそれぞれ反平行結合しているので、記録層22の磁化分布を略一方向に制御することができる。

(もっと読む)

分割ゲートNANDフラッシュメモリ構造及びアレイ、そのプログラミング方法、消去方法及び読み出し方法、並びに、製造方法

【課題】NANDフラッシュメモリ構造において、各セルについてライン数を削減して、不揮発性メモリデバイスのピッチを改善すること。

【解決手段】分割ゲートNANDフラッシュメモリ構造が第1伝導型の半導体基板の上に形成される。このNAND構造は、上記基板における第2伝導型の第1領域と、該第1領域から間隔をおいて配置された、上記基板における第2伝導型の第2領域とを備える。連続した第1チャネル領域が、上記第1領域と上記第2領域との間に定められる。複数の浮動ゲートが互いに間隔をおいて配置され、これら複数の浮動ゲートの各々は、上記チャネル領域の別々の部分上に配置される。各々が1つの浮動ゲートと関連しかつ該浮動ゲートに隣接する複数の制御ゲートが設けられる。各制御ゲートは、2つの部分、すなわち、上記チャネル領域の部分上にある第1部分と、関連する浮動ゲートの上にありかつ該浮動ゲートに容量的に接続される第2部分とを有する。

(もっと読む)

記憶素子および半導体装置

【課題】不揮発性であって、かつ情報の書き換えが可能であり、また、作製が簡単であり、スイッチング特性に優れ、動作電圧の低い記憶素子、記憶装置および半導体装置を安価で提供することを課題とする。

【解決手段】第1の導電層と、前記第1の導電層に対向する第2の導電層と、第1の導電層と第2の導電層間に設置された有機化合物層を有し、前記有機化合物層は、少なくとも一種の側鎖にアミド基を有する高分子材料を用いた記憶素子を提供する。

(もっと読む)

磁気抵抗効果素子、磁気ヘッド、磁気記録再生装置、および磁気メモリ

【課題】低抵抗を維持したまま、高密度記録に対応した高いMR変化率が得られる磁気抵抗効果素子を提供する。

【解決手段】3層以上の金属磁性層と、前記3層以上の金属磁性層の間に設けられた接続層と、前記金属磁性層および接続層に対して垂直方向に電流を通電させる電極とを具備し、前記3層以上の金属磁性層のうち最下層または最上層の金属磁性層は磁化方向が固着され、外部磁界がゼロのときに最下層の金属磁性層の磁化方向と最上層の金属磁性層の磁化方向がほぼ直交するように中間の金属磁性層の磁化方向がねじれている磁気抵抗効果素子。

(もっと読む)

小さく、スペースの狭い構成物の配列を形成する方法

集積回路に用いるための、小さく高密度に間隔をあけた孔もしくは支柱の配列を形成するための方法を開示する。高密度に充填された構成物を形成するために、様々なパターン転写ステップ、および、エッチングステップを、ピッチ減少化技術と組み合わせて用いることができる。一つの層に統合することができる、交差し引き伸ばされた構成物のピッチが減少しているパターンの重ね合わせたものを形成するために、従来のフォトリソグラフィーステップをピッチ減少化技術と組み合わせて用いることができる。 (もっと読む)

半導体装置及びその製造方法

【課題】ビット線絶縁膜の形成後に該ビット線拡散層を大きく拡散させることなく、接続部の面積を十分に確保し該接続部における拡散層抵抗の増大を抑制して、メモリセルの微細化を図れるようにする。

【解決手段】半導体装置は、半導体基板1の上部に形成され、それぞれ行方向に延びる複数のビット線拡散層2と、各ビット線拡散層2の上にそれぞれ形成された複数のビット線絶縁膜3と、各ビット線拡散層2同士の間に形成された複数のゲート絶縁膜10と、各ビット線絶縁膜3及び各ゲート絶縁膜10と交差する複数のワード線4とを有している。各ゲート絶縁膜10と各ワード線4との交差部にメモリセルが形成され、半導体基板1の上部には、各ビット線拡散層2とそれぞれ電気的に接続された接続部6aを有する複数の接続拡散層6が形成されており、半導体基板1における各接続部6aの上面は、各接続拡散層6の上面よりも低い。

(もっと読む)

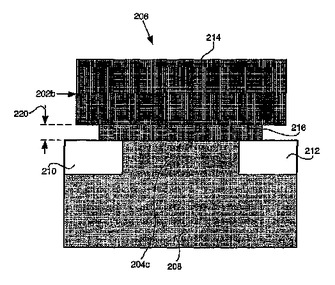

誘電体の破壊によってプログラムすることが可能なリードオンリメモリアレイ

一実施の形態によれば、プログラムすることが可能なROMアレイは、基板に位置付けられた少なくとも1のビット線(204c)を含んでいる。また、プログラムすることが可能なROMアレイは、少なくとも1のビット線(204c)を横切るように位置付けられた少なくとも1のワード線(202b)を含んでいる。また、プログラムすることが可能なROMアレイは、少なくとも1のビット線(204c)と少なくとも1のワード線(202b)との交差点に位置付けられたメモリセル(206)を含み、メモリセル(206)は、少なくとも1のビット線(204c)と少なくとも1のワード線(202b)との間に位置付けられた誘電体領域(216)を含んでいる。プログラミング動作は、誘電体領域(216)を破壊することによって、メモリセル(206)を第1の論理状態から第2の論理状態へ変化させる。プログラミング動作は、メモリセル(206)をダイオードとして動作させる。メモリセル(206)の抵抗は、メモリセル(206)が第1または第2の論理状態を有しているかどうかを決定するために、読出動作において測定され得る。  (もっと読む)

(もっと読む)

電荷蓄積型メモリ

【課題】 メモリセルの微細化を図った電荷蓄積型メモリを提供する。

【解決手段】 第1の障壁層2と電荷蓄積層3と第2の障壁層4を酸化アルミニウムで構成し、且つ電荷蓄積層3を1〜9原子層の範囲内の厚みとし、且つ前記電荷蓄積層3にはアルミニウム原子を化学量論的に過剰に存在させ、メモリセルのサイズが10nm角のときその電荷蓄積層3にアルミニウム原子の局在準位を50個超えるように持たせる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置におけるMOSトランジスタのソース・ドレイン間のリーク電流を低減する。

【解決手段】DRAMをSOI基板上に形成する。DRAMのセンスアンプ20、プリチャージ回路23、ビット線選択回路26A,26B、メモリセル27、ダミーセル28およびコラム選択回路29におけるトランジスタQn1,Qn2,Qp1,Qp2,Qpc,Qe,Qb,Qd,Qm,Qioのボディ領域を電気的に固定した。

(もっと読む)

相変化メモリおよびその製造方法

【課題】 記憶セルのサイズが小さくなった場合にも、記憶セル間の特性を略同一にすることが可能で、かつ相変化のために必要な電流量を十分に小さくすることを可能にする。

【解決手段】 第1の電極11と、第1の電極上に設けられた略同一形状を有する少なくとも2個の導電体13を有し、これらの導電体が導電体よりも高抵抗な高抵抗膜12によって隔てられている導電部と、導電部上に設けられ、第1の比抵抗を有する第1の相状態と、第1の比抵抗とは異なる第2の比抵抗を有する第2の相状態との間で相変化可能な相変化材料を有する記録層14と、記録層上に設けられた第2の電極15と、を備えた記憶セル1を有している。

(もっと読む)

渦巻状に巻かれた回路デバイスおよびその製造方法

基板上に回路層を形成することにより、渦巻状に巻かれた回路が生成される。この回路層の上および下に、任意の絶縁体層を配置することができる。この回路層は、メモリ、制御、または他の回路素子であることが考えられ、この回路層は、渦巻状に巻いて、高密度の渦巻状に巻かれたデバイスとなるように基板から解放される。回路層が解放される際に渦巻状に巻く動作を行なう、応力をかけた、渦巻状に巻く層が含まれ得る。  (もっと読む)

(もっと読む)

フラッシュメモリ素子およびその製造方法

【課題】周辺セルの干渉効果によるしきい値電圧シフトを減らすためのフラッシュメモリ素子およびその製造方法を提供する。

【解決手段】半導体基板上に形成されたトンネル誘電膜と、前記トンネル誘電膜上に形成され、セル単位で島状に分離されるフローティングゲートと、前記フローティングゲートを含んだ全面に形成された層間誘電膜と、前記層間誘電膜上に形成され、前記フローティングゲートの上面および側面を完全に覆いながら一方向に配列されるコントロールゲートとを含む。

(もっと読む)

分離トンネル窓を有する不揮発性半導体メモリセルの製造方法

【課題】本発明は、分離トンネル窓セル(SZ)を有する不揮発性半導体メモリセル(TF)を製造する方法に関する。

【解決手段】上記方法は、トンネル領域(TG)と、トンネル層(4)と、トンネル窓メモリ層(T5)と、誘電体トンネル窓層(T6)と、トンネル窓制御電極層(T7)とを有するトンネル窓セル(TF)を形成する工程と、チャネル領域(KG)と、ゲート層(3)と、メモリ層(5)と、誘電体層(6)と、制御電極層(7)とを有するトランジスタメモリセル(TZ)を形成する工程とを包含する。上記製造方法により、トンネル領域(TG)は、トンネル窓セル(TF)をマスクとして利用することによって、トンネル注入(IT)による遅い注入工程で形成される。得られるメモリセルは、少ない面積を必要とし、高いプログラム/消去サイクル数を有する。

(もっと読む)

半導体記憶装置

【課題】 微細化とソース拡散層の低抵抗化が可能な不揮発性半導体記憶装置を提供する。

【解決手段】 基板4に形成されたP型のウェル2上にN型のソース拡散層104およびN型のドレイン拡散層が形成された不揮発性半導体記憶装置であって、各ソース拡散層104をその延伸方向に沿った直線と基板4の法線とを含む平面で切った断面が凹凸形状となっており、凸部の上壁層306および凹部の下壁層307が側壁層308を介して連続することでソース拡散層104をなすとともにこの上下壁層306・307および側壁層308を覆うようにシリサイド204aが形成され、かつ該シリサイド204aを覆うように絶縁層205が形成され、上壁層306上に位置するシリサイド204aと絶縁層205との界面および下壁層307上に位置するシリサイド204aと絶縁膜205との界面の距離dが1000Å以下である。

(もっと読む)

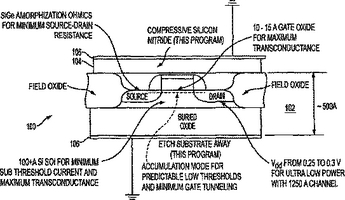

斬新な低電力不揮発性メモリおよびゲートスタック

良好な電荷保持のために、高い電荷ブロッキングバリアおよび深いキャリアトラッピングサイトを維持しながら、直接的なトンネルプログラミングと消去を可能にするNOR又はNANDメモリアーキテクチャにおいて、バンドギャップ技術に基づくゲートスタックを、反転モードおよび通常モードのフローティングノードメモリセルにおける非対称トンネルバリアと一緒に、使用することを促進する不揮発性メモリデバイスおよびアレイが記載されています。低電圧で直接的なトンネリングプログラムと消去の能力は、高いエネルギーキャリアからゲートスタックおよび結晶格子に対する損害を減少させて、書込み疲労を減少させ、デバイス寿命を増進させます。低電圧で直接的なトンネルプログラムと消去の能力は、また、低電圧設計およびさらなるデバイス形状性のスケーリングを介して、サイズ縮小を可能にします。本発明のメモリセルは、また、多数ビット記憶を可能にします。これらの特性は、本発明のメモリデバイスの実施の形態が、システム内のDRAMおよびROM双方に取って代わることができて、ユニバーサルメモリの定義内で動作することを可能にします。 (もっと読む)

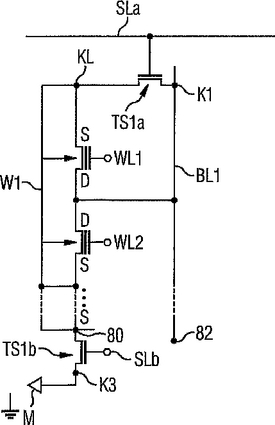

集積されたメモリ回路構造、特にUCPフラッシュメモリ

【課題】チップ面積の低減および電気特性の改善の少なくとも一方を実現できるメモリ回路構造50を提供する。

【解決手段】トランジスタをそれぞれ含む複数のメモリセルをマトリックス状に配置する。上記マトリックスの行における、メモリセルの各トランジスタの各制御電極に各ワード線WL1、WL2を配置する。上記マトリックスの列における、メモリセルの各トランジスタの各端子電極に各ビット線BL1、W1を配置する。スイッチング素子TS1aを、上記列毎に配置する。上記スイッチング素子TS1aは、上記の同一の列に位置する2つの各ビット線BL1、W1同士を電気的に断接できるようになっている。上記スイッチング素子TS1aにより、メモリ回路構造50における、チップ面積を低減および/または電気特性を改善できる。  (もっと読む)

(もっと読む)

強誘電体メモリ装置及びその製造方法

本発明は強誘電体メモリ装置及びその製造方法に関し、メモリ装置に適用される強誘電体のヒステリシス特性及び残留分極特性を大幅に増強することにより安定的なメモリ動作を提供する。本発明においては強誘電体メモリに用いられる強誘電体物質としてβ相の結晶構造を有するPVDFを用いる。本発明に係るPVDF薄膜は約0から1Vへ印加電圧が上昇することによって分極が増加して約1V程度で約5μC/cm2以上の分極を示し、再び0から−1Vへ印加電圧が下降することにつれて分極が減少していって、約−1V程度で約−6μC/cm2以下の分極を示す良好なヒステリシス特性を有する。 (もっと読む)

2,061 - 2,080 / 2,405

[ Back to top ]