Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,081 - 2,100 / 2,405

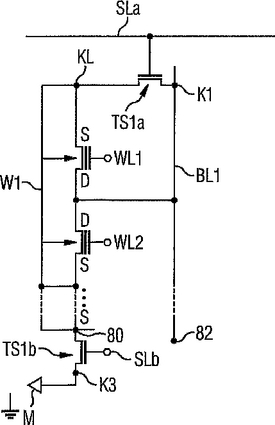

集積されたメモリ回路構造、特にUCPフラッシュメモリ

【課題】チップ面積の低減および電気特性の改善の少なくとも一方を実現できるメモリ回路構造50を提供する。

【解決手段】トランジスタをそれぞれ含む複数のメモリセルをマトリックス状に配置する。上記マトリックスの行における、メモリセルの各トランジスタの各制御電極に各ワード線WL1、WL2を配置する。上記マトリックスの列における、メモリセルの各トランジスタの各端子電極に各ビット線BL1、W1を配置する。スイッチング素子TS1aを、上記列毎に配置する。上記スイッチング素子TS1aは、上記の同一の列に位置する2つの各ビット線BL1、W1同士を電気的に断接できるようになっている。上記スイッチング素子TS1aにより、メモリ回路構造50における、チップ面積を低減および/または電気特性を改善できる。  (もっと読む)

(もっと読む)

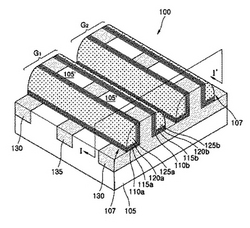

平面コンタクトを有する超スケール変更可能な縦型MOSトランジスタ

ダイまたはチップの基板(11)内のドレイン電極(17)の上方に形成されたドープシリコンブロックまたは島は、チャネル(21、23、25)の所望の長さに対応する高さを有する。ソース電極(27)がシリコン島の上方に形成され、上方からのコンタクト(41)が可能となる。上方からのコンタクト(43)もL字型のコントロールゲート(33、35)および表面下のドレインとなされる。作られる縦型トランジスタに対し、ソース、ゲートおよびドレイン用の水平方向のコンタクトのアレイが形成される。ゲートとチャネルとの間の層(29)内にナノ結晶(31)を組込んだ場合、不揮発性フローティングゲートトランジスタが形成され得る。ナノ結晶層がなければ、MOSまたはCMOSトランジスタが形成される。  (もっと読む)

(もっと読む)

マルチビット及びマルチレベル不揮発性メモリ素子、その動作方法及び製造方法

【課題】マルチビット及びマルチレベル不揮発性メモリ素子、その動作方法及び製造方法を提供する。

【解決手段】フィンの両側壁にスペーサ形態にそれぞれ形成された一対のゲート電極と、ゲート電極と半導体基板との間にそれぞれ形成された一対のストレージノードと、を備える不揮発性メモリ素子である。ゲート電極は、相互に離隔されてフィンにそれぞれ形成されたソース及びドレインを共有する。チャンネル領域は、ソース及びドレイン間のフィンの両側壁の表面領域にそれぞれ形成される。

(もっと読む)

ビット線構造およびその製造方法

本発明は、ビット線構造およびその製造方法に関する。この方法では、分離トレンチ(T)は、導電性レンチ充填層(5)によって、第2コンタクト部(KS)と第2コンタクト部(KS)に隣接する第1コンタクト部(KD)との少なくとも付近が充填されている。上記導電性レンチ充填層(5)は、埋め込み接触バイパス線を得るために、第2コンタクト部(KS)に隣接する第1不純物領域(D)を相互連結している。  (もっと読む)

(もっと読む)

相変化メモリ装置

本発明は、相変化メモリセルに関するものである。相変化メモリセルは、第1薄層スペーサと第2薄層スペーサとを有している。この第1薄層スペーサは、サブリソグラフィック寸法を規定し、第1電極と電気的に接続している。また、第2薄層スペーサは、サブリソグラフィック寸法を規定し、第2電極と、第1薄層スペーサとの間を電気的に接続している。そして、第1薄層スペーサが第2薄層スペーサに電気的に接続された境界領域に相変化メモリセルが形成されている。  (もっと読む)

(もっと読む)

半導体装置

【課題】2つのバイポーラトランジスタを用いたアンチヒューズにおいて、書込み電圧を低減する。

【解決手段】第1エミッタ電極8と、第1ベース電極6と、第1コレクタ電極7とを第1領域の上方に有する第1トランジスタQ1を具備し、第1ベース電極6と第1ベース領域の間を接続するベース引出しポリシリコン9は、第1領域の外に設けられる第2領域の上方を通過させ、抵抗値を付加する。

(もっと読む)

多ビット仮想接地NANDメモリデバイス、メモリデバイス

【課題】記憶密度を増大化できるメモリデバイスを提供する。

【解決手段】仮想接地NAND構造内に、電荷トラップ多ビットメモリセルのアレイを配置する。上記メモリセルは、電子をメモリ層へとファウラー−ノルドハイムトンネリングすることによって消去される。書き込み動作は、ホット正孔注入によって行われる。書き込み電圧は、1つのビット線によって、2つのNANDチェインへ直列に印加される。プログラムされる上記メモリセル側にある次に続くビット線は浮遊電位に保持されていて、一方、他方の側にあるビット線は抑制電圧に設定される。この抑制電圧は、プログラムされない、アドレス指定されたメモリセルのプログラム障害を抑制するために供給される。上記電荷トラップメモリセルの仮想接地NAND構造は、記憶密度を増加させることができる。

(もっと読む)

ナノ複合体の誘電膜、その誘電膜を有するキャパシタ及びその製造方法

【課題】漏れ電流特性に優れ、コンケーブ構造を含む種々のキャパシタで採用可能であり、且つ、高い誘電率を得ることができるナノ複合体の誘電膜、その誘電体を有するキャパシタ及びその製造方法を提供すること。

【解決手段】キャパシタ用誘電膜は、HfO2と少なくともHfO2の比誘電率と同じ比誘電率を有する誘電膜(ZrO2、La2O3またはTa2O5の中から選択される誘電率が25〜30であり、バンドギャップエネルギーが4.3〜7.8)がナノ複合体の形態で混合されたナノ複合体の誘電膜を含むことによって、相対的に薄い厚さでも誘電率の損失なしに漏れ電流特性を確保しながら高い誘電率を有するキャパシタを製造することができる効果がある。

(もっと読む)

磁気メモリ及びその製造方法

【課題】MRAMのディスターブ耐性の向上。

【解決手段】磁気メモリは、磁気抵抗素子を有するメモリセル10と、そのメモリセル10に情報を書き込む際の書き込み磁場を生成する書き込み電流が流れる書き込み配線100と、その書き込み配線100のメモリセル10に対向する対向面FSを除く面の少なくとも一部を覆う強磁性体膜120と、バイアス磁場印加部130とを備える。バイアス磁場印加部130は、書き込み配線100の長手方向(X)に沿った第1成分を含むバイアス磁場を、強磁性体膜120に印加する。その第1成分の正負符号は、強磁性体膜120のうち少なくともメモリセル10とオーバーラップするオーバーラップ領域ROにおいて、一様である。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 チップの主面内のパターンの解像度を向上させる。

【解決手段】 チップを含む半導体ウエハの半導体基板1の主面上にキャップ膜を形成した後、チップ内のメモリ領域Mにキャップパターン15aを形成するための露光、現像およびエッチング処理と、チップ内においてメモリ領域Mから離れた空き領域Eにキャップパターン15b1を形成するための露光、現像およびエッチング処理とをそれぞれ別々に行う。これにより、メモリ領域Mおよび空き領域Eの各々に合った条件で露光および現像等を行うことができるので、チップの主面内のパターンの解像度を向上させることができる。

(もっと読む)

バックバイアスを用いてSOI基板に形成されたフラッシュブロックを消去するためのフラッシュメモリ素子の製造方法、その消去方法及びその構造

【課題】工程が簡単で、再現性が高く、リフラッシュが可能なフラッシュ素子をSOI基板を用いて製作する方法を提供し、フラッシュ素子の大きさを小型に製作するために、SOI基板を用いて製作する方法を提供する。

【解決手段】本発明に係わるSOI基板上に形成されたフラッシュブロックでバックバイアスを用いてフラッシュブロックを消去できるフラッシュメモリ素子の製作方法は、SOI基板上にフラッシュブロックが形成されるステップ及びSOI基板の下面にボディー電極が形成されるステップとを含む。

(もっと読む)

半導体記憶装置

【課題】 ワード線断線故障が発生した場合の歩留まり低下を抑えて歩留まりを改善することができる半導体記憶装置を提供する。

【解決手段】 ワード線WL1,WL2は異なる配線層に形成される金属配線である。ワード線WL1とワード線WL2とは複数の接続部CN1〜CNMにより電気的に接続される。ワード線WL1,WL2のうちの一方のワード線が断線しても、接続部CN1〜CNMのいずれかを介して他方のワード線から電位が与えられる。また、ワード線WL1,WL2が異なる配線層に形成されているので2本のワード線がともに断線する可能性が低くなる。よって断線故障による動作不良が生じにくくなるので歩留まりを向上することができる。

(もっと読む)

半導体装置の製造方法

【課題】 的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 下地領域(13,15,16)上に第1のマスクパターン(21a,21b)を形成する工程と、下地領域上に、第1のピッチで配置された複数のダミーラインパターン(21c)を形成する工程と、ダミーラインパターンの両長側面に形成された所定マスク部分を有する第2のマスクパターン(25c)を形成する工程と、ダミーラインパターンを除去する工程と、第1のマスクパターン及び所定マスク部分をマスクとして用いて下地領域をエッチングする工程と、を備える。

(もっと読む)

所定のピン配列を有するメモリモジュール

【課題】信号ピンが基準として電源ピンを用いることによって生じるノイズの増加を抑えるメモリモジュールを提供する。

【解決手段】メモリモジュール(104、106)は、支持基板と、支持基板上に取り付けられる複数のメモリデバイス(122、124)と、支持基板上で所定の配列を有するピン(PF、PR)とを備え、ピン(PF、PR)は、電源ピン、グラウンドピン及びメモリデバイスに接続される信号ピンから構成され、ピン(PF、PR)の所定の配列では、信号ピンの各々は基準としてグラウンドピンを利用し、電源ピンとグラウンドピンとの間の電気抵抗を下げるために、電源ピンの各々はグラウンドピンに隣接していることを特徴とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体集積回路

【課題】 不揮発記憶保持用途の電界効果トランジスタと、論理演算用途の電界効果トランジスタの製造工程を別々に設けることなく前記2用途の電界効果トランジスタを同一半導体基板上に同一構造に作製できるようにする。

【解決手段】 ゲート絶縁構造体12に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタで半導体集積回路のメモリ回路とロジック回路の両方を構成し、ゲート絶縁構造体に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタのゲート-基板領域間に印加する電圧の大きさと印加タイミングを制御することによって、論理演算状態と記憶書込み状態と不揮発記憶保持状態を電気的に切り替える。

(もっと読む)

半導体集積回路装置およびその書き込み方法

【課題】書き込み電圧を低減でき、微細化に有利な半導体集積回路装置およびその書き込み方法を提供する。

【解決手段】半導体集積回路装置は、マトリクス状に設けられ、それぞれが浮遊ゲートと制御ゲートとを有する複数のメモリセルトランジスタMTを備えたメモリセルアレイ13と、前記メモリセルアレイの周辺に配置され、電流経路の一端が選択制御ゲートに接続された第1高耐圧系トランジスタTR3と、電流経路の一端が前記選択制御ゲートに隣接する第1非選択制御ゲートに接続され、前記第1非選択制御ゲートに前記メモリセルトランジスタの電流経路が導通する程度の中間電圧を印加して、前記選択制御ゲートと前記第1非選択ゲートとの間に生じた第1容量カップリングにより、前記選択制御ゲートに印加された電圧を書き込み電圧まで上昇させる第2高耐圧系トランジスタTR2とを備えた高電圧系回路領域12とを具備する。

(もっと読む)

微細コンタクトを備える半導体素子及びその製造方法

【課題】フォトリソグラフィの解像度を超えるサイズのコンタクトを多様な形態で製作できる微細コンタクトを備える半導体素子及びその製造方法を提供する。

【解決手段】層間絶縁膜を貫通して導電領域と連結され、層間絶縁膜の最上層に層間絶縁膜とエッチング選択比が異なる第1スペーサにより取り囲まれた第1コンタクト、及び導電領域に連結され、第1コンタクトと共に第1方向に配列されつつ第1スペーサの間に埋め込まれる第2コンタクトを備える半導体素子である。これにより、層間絶縁膜内に形成されたホール形態のコンタクトホールの両側壁を覆うスペーサを利用してコンタクトのピッチを1/2に減らせ、第1方向と垂直な第2方向の層間絶縁膜に第3コンタクトを形成することによって、多様な配列を有するコンタクトを形成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 素子分離領域上へのフローティングゲート電極の張り出しを無くすことで素子の微細化を図ると共に、所望のカップリング比を得ることが可能な半導体装置を提供する。

【解決手段】 第1の多結晶シリコン膜5は、その上部5aが下側から上側にかけて先細り形状(テーパ部5aa)に形成されている。第1の多結晶シリコン膜5の上部5aのテーパ部5aaの側部に形成された素子分離絶縁膜11をドライエッチング処理で除去できる。

(もっと読む)

半導体装置

【課題】 キャパシタが埋め込まれるトレンチの間隔に余裕を持たせることができる半導体装置を提供する。

【解決手段】 メモリセルMC1,MC2は、トレンチ7に埋め込まれたキャパシタを有する。トレンチ7は、面方位{100}の表面を有する半導体基板に形成される。トレンチ7の横断面は長方形である。トレンチ7の横断面は、ワード線WLの延びる方向に対して同じ向きに傾いている。

(もっと読む)

2,081 - 2,100 / 2,405

[ Back to top ]