Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,201 - 2,220 / 2,405

半導体装置およびその製造方法

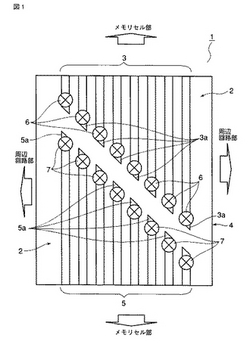

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】書き込み電流の低減と微細化に適したMTJ素子の形状を提案する。

【解決手段】本発明の例に関わるMTJ素子は、磁化方向が固定される第1強磁性層と磁化方向が磁場に応じて変化する第2強磁性層とを備える。第2強磁性層は、長軸方向を持つ本体部11aと、本体部11aから長軸とは異なる方向に突出する1つの突出部11bとから構成される。

(もっと読む)

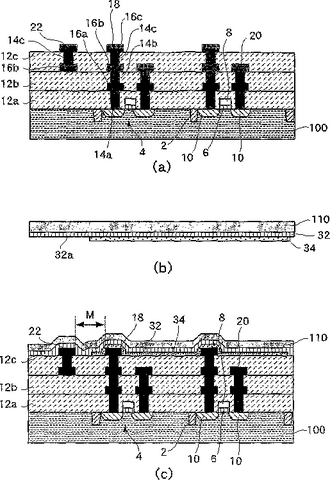

強誘電体メモリ装置

この発明は、メモリセルトランジスタとメモリセルキャパシタとからなるメモリセルを複数有する強誘電体メモリ装置(101)において、各メモリセルキャパシタ(101a)を、各メモリセルキャパシタ毎に独立した下部電極(2)と、該下部電極(2)上に形成された強誘電体層(3)と、該強誘電体層(3)上に形成され、複数が共通に接続されてプレート電極を形成する上部電極(4)とから構成し、上部電極の幅を、強誘電体層の幅よりも狭くしたものである。この発明に係る強誘電体メモリ装置では、上部電極の幅を強誘電体層の幅より小さくしたことにより、上部電極と下部電極との間での電流リークを防止することができ、これにより、上部電極と下部電極との間での電流リークの発生を招くことなくメモリセルキャパシタの配置間隔を縮小して、より小さいメモリセルサイズを実現することができる。  (もっと読む)

(もっと読む)

磁気メモリ装置並びにその読み出し方法及び書き込み方法

【課題】磁性層のスピンの向きに基づく抵抗変化を利用した磁気メモリ装置に関し、高集積化が可能であり、MTJ素子の特性ばらつきに対する十分な読み出しマージンを有し、メモリ動作の際のノイズに対する耐性が高い磁気メモリ装置、並びにこのような磁気メモリ装置の読み出し方法及び書き込み方法を提供する。

【解決手段】直列接続された互いに相補的な抵抗状態をとる2つの磁気抵抗効果素子と、これら磁気抵抗効果素子の接続ノードに接続された選択用トランジスタとを有するメモリセルと、磁気抵抗効果素子の接続ノードに選択用トランジスタを介して接続されたビット線と、ビット線に出力される接続ノードの電圧に基づいて磁気抵抗効果素子に記憶された記憶情報を読み出す読み出し回路とを有する。

(もっと読む)

ツインビットセル構造のNOR型フラッシュメモリ素子及びその製造方法

【課題】ツインビットセル構造のNOR型フラッシュメモリ素子及びその製造方法を提供する。

【解決手段】基板上で所定方向に沿って直線状に平行に延びている複数の活性領域と、活性領域上に形成され、複数のワードラインのうち選択される1本のワードラインと複数本のビットラインのうち選択される1本のビットラインとの接点によって各々決定される複数のメモリセルを備えるNOR型フラッシュメモリ素子である。活性領域には、複数のソース/ドレイン領域が形成されており、ソース/ドレイン領域は、複数のメモリセルのうち、相互隣接した2つのメモリセルを共有する。ソース/ドレイン領域は、各々1個のビットラインコンタクトを通じてビットラインと電気的に連結されうる。複数のメモリセルのうち、選択される相互隣接した4個のメモリセルは、1個のビットラインコンタクトを共有する。

(もっと読む)

半導体記憶装置

【課題】セル間のショートを抑制して動作信頼性を向上すると共に、高速動作化に寄与できる半導体記憶装置を提供する。

【解決手段】DRAMセルが形成される活性領域7は、シリコン基板1に形成された分離トレンチ40により規定され、分離トレンチ40内には分離絶縁膜4が形成される。DRAMセルは、ゲート電極12およびそのサイドウォール13を備えるMOSトランジスタと、上部電極22およびそのサイドウォール23を備えるキャパシタを有している。分離トレンチ40の上部にはリセス41が形成され、キャパシタの上部電極22はその内部に埋め込まれた埋設部を有する。上部電極22において、埋設部の外側エッジE1は、サイドウォールの外側エッジE2よりも内側に位置している。

(もっと読む)

強誘電体メモリ

【課題】低電圧動作が可能でセルサイズが小さい強誘電体メモリを提案する。

【解決手段】本発明の例に関わる強誘電体メモリは、ノードN1,N2の間に接続される第1NMOSと、ノードN2,N3の間に接続される第2NMOSと、ノードP1,P2の間に接続される第1PMOSと、ノードP2,P3との間に接続される第2PMOSと、第1配線層内に形成され、ノードN1,P1を接続する第1配線と、第1配線層内に形成され、ノードN3,P3を接続する第2配線と、第2配線層内に形成され、ノードN2,P2を接続する第3配線と、第1電極が第1配線に接続される第1キャパシタCF1と、第1電極が第2配線に接続される第2キャパシタCF2とを備え、第1及び第2キャパシタCF1,CF2の第2電極は、共に、ノードN2又はノードP2に接続される。

(もっと読む)

不揮発性メモリおよびその製造方法

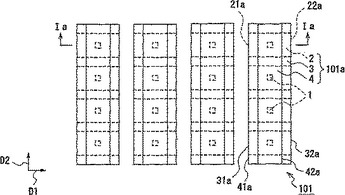

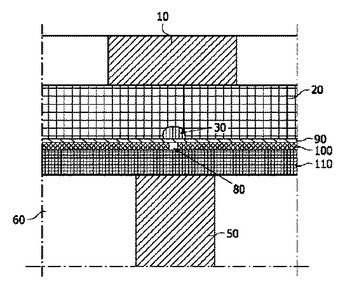

第1の基板(100)と、第2の基板(110)とを備え、第1の基板(100)は、マトリクス状に配置された複数のスイッチング素子(4)と、各スイッチング素子(4)に電気的に接続された複数の第1の電極(18)とを有し、第2の基板(110)は、導電膜(32)と、電気的パルスが印加されることにより抵抗値が変化する記録層(34)とを有しており、

複数の第1の電極(18)は、記録層(34)により一体的に覆われており、これによって、複数の第1の電極(18)と導電膜(32)との間に記録層(34)が挟持され、第1の基板(100)は、第2の電極(22)をさらに備え、第2の電極(22)は、導電膜(32)と電気的に接続され、記録層(34)への通電時に一定電圧に保持される不揮発性メモリである。この不揮発性メモリによれば、高集積度を低コストで実現することができる。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】製造コストを低減可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルMTJを含む。複数の第1書き込み線WBLは、複数の前記メモリセルと電気的、または磁気的、または電気的且つ磁気的に接続され、且つ第1方向に沿って設けられる。第1接続線CONWBLは、複数の前記第1書き込み線の少なくとも2つを相互に電気的に接続する。

(もっと読む)

半導体記憶装置

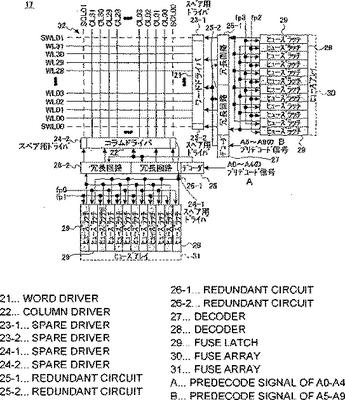

半導体記憶装置は、第1のアドレスを冗長するための複数の第1のヒューズラッチ回路と、第2のアドレスを冗長するための複数の第2のヒューズラッチ回路と、複数の第2のヒューズラッチ回路を無効にするための無効回路と、複数の第1のヒューズラッチ回路に対応する複数の第1のヒューズの位置は互いに隣接することがなく、複数の第2のヒューズラッチ回路に対応する第2のヒューズの位置が間に介在することを特徴とする。  (もっと読む)

(もっと読む)

熱電プログラマブル装置のアンチヒューズ

熱プログラマブルメモリは、熱プログラマブル抵抗材料、好適には、相変化材料のプログラマブル素子(20)と、プログラマブル材料に隣接するように配置された破壊可能な又は破壊されたアンチヒューズ(80)とを有する。そのような破壊されたアンチヒューズは、製造中に誘電体に小さな孔を形成するよう高電圧を短時間誘電体の両端間に印加できるようにするために導電層(90,110)に包囲された誘電層(100)から有して、材料をプログラミングする際のきわめて小さいヒータとして用いることができる小さい導通経路を形成することができる。孔による電流の制限のために、高抵抗状態に切り替えるために加熱する必要がある材料の量が非常に少なくなる。その結果、プログラム電力を低くすることができる。  (もっと読む)

(もっと読む)

半導体装置のキャパシタ及びその製造方法

【課題】低い漏洩電流の特性と高い静電容量を有する半導体装置のキャパシタ及びその製造方法を提供する。

【解決手段】半導体装置のキャパシタは、半導体基板上の所定の下部構造上に形成された下部電極と、前記下部電極上に形成され、低い漏洩電流の特性を有するAlON膜と、前記AlON膜上に形成され、前記AlON膜に比べて相対的に高い誘電率を有するYON膜と、前記YON膜上に形成された上部電極とを含む。

(もっと読む)

多重透過位相マスク及びこれを用いた露光方法

【課題】マスクの微細なパターンの臨界寸法を正確に実現しうる多重透過位相マスク及びこれを用いた露光方法を提供する。

【解決手段】露光装置に使用されるマスクにおいて、透明基板10と、該透明基板10の上部に形成されており、光透過領域Aと光遮断領域Bとを定義する光遮断膜12と、前記光透過領域Aの所定領域に形成され、光の位相を反転させて透過させる位相反転領域14と、を備えてなることを特徴とする多重透過位相マスク及びこれを用いた露光方法を提供する。

(もっと読む)

半導体装置

【課題】高速で信号/データを転送することのできる小占有面積の終端回路を内蔵する出力回路を提供する。

【解決手段】パッド(5)を駆動する出力トランジスタ(2a、2b、4a、4b)をドレイン不純物領域(PDa、NDa)を共有する単位トランジスタの並列体で構成し、また、終端抵抗(12、14)を介してパッドを終端する終端トランジスタ(11a、11b、15a、15b)も、それぞれ、ドレイン不純物領域を共有する単位トランジスタの並列体で構成する。また、終端トランジスタの各単位トランジスタのドレインコンタクト-ゲート間距離(Lpt,Lnt)は、出力トランジスタの各単位トランジスタのドレインコンタクト-ゲート間距離(Lpo,Lno)よりも短くする。サージに対する信頼性を確保しつつ終端回路の面積を低減する。

(もっと読む)

半導体記憶装置及びメモリカード

【課題】 行選択回路における高耐圧のトランジスタの数を削減することにより、回路面積の縮小化を図った半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、複数のメモリブロックを有するメモリセルアレイであって、各メモリブロックに複数のメモリセルがマトリックス状に配置されているとともに、1又は複数のメモリセルを選択するための複数の第1選択ゲートトランジスタを有する、メモリセルアレイと、前記第1選択ゲートトランジスタの導通/非導通を制御する制御信号を、前記第1選択ゲートトランジスタのゲートに入力するための選択ゲート線であって、隣接する2つのメモリブロックで共有された、選択ゲート線と、入力されたアドレス信号で指定された行のメモリブロックを選択する、行選択回路と、を備える。

(もっと読む)

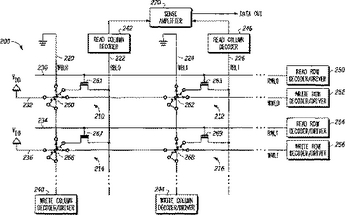

接地された書き込みビット・ライン及び電気的に絶縁された読み出しビット・ラインを有するMRAMアーキテクチャ

磁気抵抗ランダム・アクセス・メモリ(MRAM)アレイ(200)の各メモリ・セル(260、262、266、268)は、磁気抵抗トンネル接合部(MTJ)と、MTJに連結されたトランジスタ(261)とを有する。書き込みは、アレイの行及び列に沿う書き込みライン(220、232)により行なわれる。1組の書き込みライン(232、236)が、トランジスタに接続されていないMTJの端部に接続されている。従って、これらの書き込みラインは、MTJに近く、そのため、MTJに対する良好な磁気結合を有する。これは、書き込み電流を低く維持する上で重要である。これらの書き込みラインは、一方の端部において、ドライバ(240、252)によって駆動される。他方で、MTJに接続されていないメモリ・セルのトランジスタの端部に接続された読み出しビット・ライン(222)において、検出が行なわれる。書き込みドライバからの異なるライン上にセンス・アンプ(270)を有しているので、書き込みドライバ(240、252)のキャパシタンスによって検出に遅れが生じることはない。  (もっと読む)

(もっと読む)

二種の抵抗体を含む不揮発性メモリ素子

【課題】二種の抵抗体を含む不揮発性メモリ素子を提供する。

【解決手段】下部電極と、下部電極上に形成されて2種以上の抵抗パターンを示す第1抵抗層と、第1抵抗層上に形成され、スレショルドスイッチング特性を持つ第2抵抗層と、第2抵抗層上に形成された上部電極と、を備える二種の抵抗体を含む不揮発性メモリ素子。

(もっと読む)

半導体記憶装置

【課題】

メモリセルの面積を増やすことなく高集積化し、低コストでより大容量の半導体記憶装置を提供する。

【解決手段】

半導体層上に形成された電荷保持機能を有する第1メモリ機能体120と、第1メモリ機能体120上に形成された制御ゲート電極106と、第1メモリ機能体120下に配置されたチャネル領域と、チャネル領域の両側に配置され、チャネル領域と逆導電型を有する拡散領域101、102と、第1メモリ機能体120及び制御ゲート電極106の両側または一方側に配置され、拡散領域101、102と接するように形成された電荷保持機能を有する第2メモリ機能体108、109とを備えてなるメモリ素子を有する。

(もっと読む)

磁気記憶装置の製造方法

【課題】エッチングマスクの形成方法を工夫することで、反強磁性層とビット線とのショートを防止し、高集積化を可能とする。

【解決手段】反強磁性層112と磁化固定層113とトンネル絶縁層114との積層膜115を形成し、さらに磁化回転層116と電極層117とマスク絶縁層118を形成し、磁化回転層116より上部を加工して複数の磁気抵抗効果素子101の上部を形成した後、全面を被覆する第1、第2絶縁膜122、123を形成し、異方性エッチングにより第1絶縁膜122の側壁に第2絶縁膜123を残し、積層膜115を分離する領域上に開口部125を有するもので積層膜115を残す領域上に形成したマスクパターン124と第2絶縁膜123とをマスクに用いて第1絶縁膜122を除去し、さらに第2絶縁膜123を除去し、次に第1絶縁膜122、マスク絶縁層118をマスクに用いて積層膜115を除去して磁気抵抗効果素子101を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 酸素イオン注入工程とアニール工程を半導体装置の製造方法に応用し

、半導体装置のコストパフォーマンスを著しく向上させた半導体装置とその製造

方法の提供。

【解決手段】 ゲート酸化膜厚の異なる複数のMOSFETおよび素子分離領域を酸素

インプラを用いた新しい製造方法で構築し、パフォーマンスに優れた半導体集積

回路装置を構成する。

(もっと読む)

2,201 - 2,220 / 2,405

[ Back to top ]